Эти инструкции иллюстрируют рекомендуемые настройки при использовании блоков Divide и Product в модели для улучшения области и синхронизации на целевом FPGA. Каждое руководство имеет уровень серьезности, который указывает уровень соответствия требованиям. Дополнительные сведения см. в разделе Рекомендации по моделированию HDL Уровни серьезности.

Идентификатор руководства

2.7.1

Серьезность

Очень рекомендуем

Описание

Алгоритмы цифровой обработки сигналов (ЦПС) используют несколько умножителей и накопителей. Устройства FPGA, поставляемые поставщиками, такими как Xilinx ® и Intel ®, содержат выделенные фрагменты DSP. Эти малоразмерные, высокоскоростные фрагменты DSP содержат несколько умножителей и накопителей, которые делают устройства FPGA наиболее подходящими для приложений DSP.

Архитектура фрагментов DSP сильно различается у разных поставщиков FPGA и у разных семейств устройств, поставляемых одним и тем же производителем. Чтобы сопоставить модель Simulink ®, содержащую сумматоры, множители и задержки, с фрагментами DSP, адаптируйте модель к архитектуре фрагментов DSP, принимая во внимание следующее:

Расположение флипфлопов, сумматоров и множителей в фрагменте DSP.

Параметры округления и насыщения.

Битовая ширина сумматоров и множителей. Для эффективного отображения используйте в модели битовую ширину, которая меньше или равна битовой ширине блока DSP.

Когда битовая ширина модели становится больше битовой ширины DSP, ваша конструкция не укладывается в один DSP. В этом случае требуется несколько DSP или дополнительная логика.

Можно сопоставить эти блоки в модели с блоками DSP в FPGA:

Добавить и суммировать

Задержка

Продукт

Умножение-сложение

Умножить - накапливать

На этом рисунке показана архитектура DSP Xilinx. FPGA серии Xilinx 7 имеют выделенные фрагменты DSP, использующие эту архитектуру. Архитектура DSP состоит из входных регистров, предварительного сумматора, умножителя 25x18, промежуточных регистров, последующего сумматора и выходного регистра.

Дополнительные сведения см. в разделе Обзор фрагментов DSP48E1 в документации по Xilinx.

На этом рисунке показана архитектура Intel DSP. Эта архитектура DSP для устройств Stratix ® V является архитектурой DSP переменной точности. Блоки DSP могут иметь битовую ширину 9, 18, 27 и 36 битов и комплексное умножение 18 25 для FFT.

Для получения дополнительной информации см. раздел «Блочная архитектура DSP» в документации Intel.

Чтобы узнать, как можно разработать алгоритм для сопоставления с этим блоком DSP, откройте модель hdlcoder_multiplier_adder_dsp.slx

open_system('hdlcoder_multiplier_adder_dsp') set_param('hdlcoder_multiplier_adder_dsp', 'SimulationCommand', 'Update')

Модель состоит из двух подсистем dsp_subsys1 и dsp_subsys2, реализующих операцию C + ((A + D) * B. Эту операцию также можно реализовать с помощью блоков умножения-сложения или умножения-накопления, как показано подсистемами DSP_MultAdd и DSP_MultAcc.

dsp_subsys1 реализует операцию C + ((A + D) * B, используя битовую ширину, равную DSP в FPGA серии Xilinx 7. Если вы откроете мастер рабочего процесса HDL и развернете эту подсистему на Xilinx Virtex ® 7 FPGA, вся конструкция будет точно соответствовать одному фрагменту DSP.

dsp_subsys2 реализует ту же самую операцию, используя битовые ширины, которые больше, чем DSP в Xilinx FPGA. Если развернуть эту подсистему на FPGA Xilinx Virtex 7, будет видно, что вся конструкция соответствует одному фрагменту DSP и использует дополнительную логику среза.

auto для блока усиления2.7.2

Очень рекомендуем

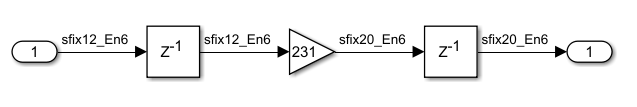

При использовании блока усиления в конструкции для достижения наиболее эффективной реализации по площади установите для свойства блока HDL ConstMultiplierOptimization значение auto. Генератор кода выбирает между CSD и FCSD реализации, которые дают наименьший размер схемы и генерируют код HDL без использования оператора умножения (*).

Вы можете использовать эту настройку, чтобы избежать нацеливания ресурсов DSP и уменьшить количество логических схем на Intel ® Quartus ® Prime при синтезировании вашего дизайна на целевом FPGA. Например, в этой таблице показан сгенерированный код HDL для блока усиления в зависимости от настроек свойств блока HDL для блока ConstMultipliureOptimization.

ConstMultiplierOptimization Настройка и влияние на сгенерированный код HDL

ConstMultiplierOptimization Настройка | Операции | Сгенерированный код HDL |

|---|---|---|

CSD | Создает параллельные входные данные и добавляет или вычитает результаты.

| Этот код показывает сгенерированный код VHDL. -- CSD Encoding(231): 1001'01001'; Cost (Adders) = 3 DOUT_mul_temp <= ((resize(DIN & '0' & '0' & '0' & '0' & '0' & '0' & '0' & '0', 21) - resize(DIN & '0' & '0' & '0' & '0' & '0', 21)) + resize(DIN & '0' & '0' & '0', 21)) - resize(DIN, 21); DOUT <= DOUT_mul_temp(19 DOWNTO 0); В этом коде отображается созданный код Verilog.

// CSD Encoding (231) : 1001'01001'; Cost (Adders) = 3

assign Gain_1 = {DIN[11], {DIN, 8'b00000000}};

assign Gain_2 = {{4{DIN[11]}}, {DIN, 5'b00000}};

assign Gain_3 = {{6{DIN[11]}}, {DIN, 3'b000}};

assign Gain_4 = {{9{DIN[11]}}, DIN};

assign DOUT_mul_temp = ((Gain_1 - Gain_2) + Gain_3) - Gain_4;

assign DOUT = DOUT_mul_temp[19:0];

|

FCSD | Добавляет входные данные и данные приведения в каждом каскаде.

| Этот код показывает сгенерированный код VHDL. -- FCSD for 231 = 33 X 7; Total Cost = 2 -- CSD Encoding (33) : 0100001; Cost (Adders) = 1 Gain_factor <= resize(DIN & '0' & '0' & '0' & '0' & '0', 21) + resize(DIN, 21); -- CSD Encoding (7) : 1001'; Cost (Adders) = 1 DOUT_mul_temp <= resize(Gain_factor & '0' & '0' & '0', 21) - Gain_factor; DOUT <= DOUT_mul_temp(19 DOWNTO 0); В этом коде отображается созданный код Verilog.

// FCSD for 231 = 33 X 7; Total Cost = 2

// CSD Encoding (33) : 0100001; Cost (Adders) = 1

assign Gain_3 = {{4{DIN[11]}}, {DIN, 5'b00000}};

assign Gain_4 = {{9{DIN[11]}}, DIN};

assign Gain_factor = Gain_3 + Gain_4;

// CSD Encoding (7) : 1001'; Cost (Adders) = 1

assign Gain_1 = {Gain_factor, 3'b000};

assign Gain_2 = Gain_1[20:0];

assign DOUT_mul_temp = Gain_2 - Gain_factor;

assign DOUT = DOUT_mul_temp[19:0];

|

auto | Выбирает реализацию CSD или FCSD, использующую меньшее количество сумматоров. | Сгенерированный код HDL аналогичен реализации CSD или FCSD. |

none | Использует оператор умножения (*). | Этот код показывает сгенерированный код VHDL. DOUT_mul_temp <= to_signed(2#011100111#, 9) * DIN; DOUT <= DOUT_mul_temp(19 DOWNTO 0); В этом коде отображается созданный код Verilog. assign DOUT_mul_temp = 231 * DIN; assign DOUT = DOUT_mul_temp[19:0]; |

ShiftAdd Архитектура разделительного блока для типов с фиксированной точкой2.7.3

Рекомендуется

При использовании типов данных с фиксированной точкой в качестве входных данных блока разделения укажите архитектуру HDL блока как ShiftAdd а затем задайте свойству блока HDL UsePipelines значение on. В этой архитектуре блок вычисляет результат, используя несколько операций сдвига и добавления. Для достижения более высоких тактовых частот на целевом устройстве FPGA выполняются конвейерные операции.

При использовании типов данных с плавающей запятой в качестве входных данных блока разделения оставьте для архитектуры HDL значение по умолчанию Linear и установите для IP-библиотеки с плавающей запятой значение Native Floating Point.