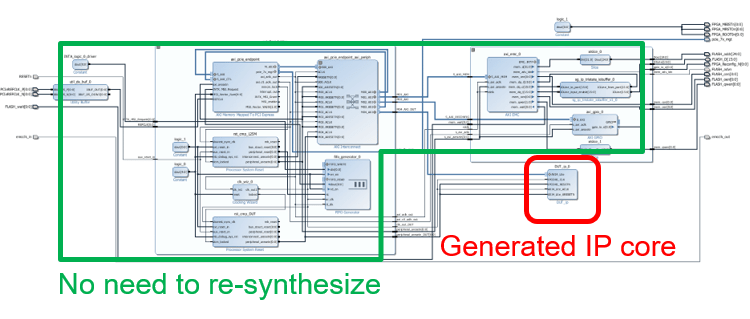

Для целевых платформ, поддерживающих IP Core Generation с помощью Xilinx ® Vivado ® можно использовать кэширование IP. Кэширование IP сокращает время синтеза эталонных конструкций, имеющих множество IP-модулей или имеющих IP-модули со значительным временем выполнения синтеза. При включении кэширования IP-адресов проект Vivado использует рабочий процесс вне контекста (OOC). Этот рабочий процесс синтезирует IP-адрес в ссылочной конструкции вне контекста из конструкции верхнего уровня. Рабочий процесс OOC ускоряет выполнение проекта, так как средство синтеза повторно использует кэш IP-адресов и не должно повторно синтезировать IP-адрес при запуске рабочего процесса.

Если кэширование IP не включено, по умолчанию в проекте Vivado используется глобальный поток синтеза. Этот процесс синтезирует IP-модули в эталонной конструкции вместе с конструкцией верхнего уровня. При последующих запусках проекта этот рабочий процесс повторно анализирует IP-модули в эталонном проекте.

Целевой рабочий процесс:

IP Core Generation

Simulink Real-Time FPGA I/O для плат Speedgoat, использующих Xilinx Vivado

Инструмент синтеза: Xilinx Vivado

IP-кэш - это папка, состоящая из подпапок, соответствующих IP-модулям в эталонном проекте. Каждая подпапка организована по хэш-индексу, который соответствует имени файла. Для каждого IP-модуля подпапка состоит из файлов Xilinx Core Instance (XCI), файлов Design Checkpoint (DCP) и файлов журнала синтеза. DCP - это файл-контейнер, содержащий синтезированные списки соединений, файлы-заглушки HDL черного ящика и ограничения выходного тактового сигнала.

Для повторного использования IP-кэша при выполнении рабочего процесса IP-синтез должен соответствовать индексу хеширования в IP-кэше. Совпадение хеш-индекса соответствует попаданию в IP-кэш. Чтобы попасть в IP-кэш при последующих запусках, используйте то же самое:

Параметры компонентов, языка и целевой платформы

Ссылочный вариант конструкции

Целевая частота

hdl_prj при создании IP-кэша

При включении кэширования IP-адресов в проекте Xilinx Vivado используется рабочий процесс вне контекста (OOC). Поток проектирования OOC представляет собой рабочий процесс снизу вверх, который:

Синтезирует IP-модули в эталонной конструкции отдельно от конструкции верхнего уровня. Результатом синтеза является файл контрольной точки проекта (DCP).

Синтезирует дизайн верхнего уровня, рассматривая IP-адрес в эталонном дизайне как черный ящик, используя файлы-заглушки HDL, поставляемые с DCP.

Реализует проект на целевом устройстве, связывая списки соединений из файлов контрольных точек IP-проекта с списком соединений верхнего уровня.

Для крупных эталонных проектов поток OOC увеличивает время выполнения синтеза, поскольку не требуется повторно синтезировать IP-адрес при изменении конструкции и выполнении рабочего процесса. Дополнительные сведения о рабочем процессе OOC и параметрах синтеза IP см. в документации Xilinx.

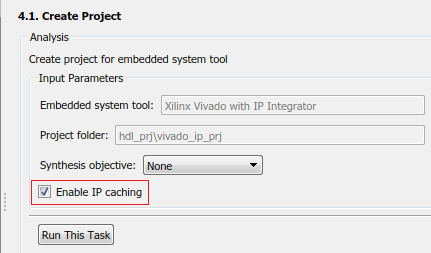

Перед включением кэширования IP-адресов укажите IP Core Generation в качестве целевого рабочего процесса, а затем укажите параметры целевой платформы. Чтобы включить кэширование IP:

В помощнике по рабочим процессам HDL в задаче Создать проект установите флажок Включить кэширование IP-адресов.

В командной строке используйте команду EnableIPCaching имущества hdlcoder.WorkflowConfig класс. Чтобы использовать это свойство, создайте объект hdlcoder.WorkflowConfig или экспортировать параметры помощника по рабочим процессам HDL в сценарий.

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','IP Core Generation'); % ... % ... hWC.EnableIPCaching = true;

Использование кэширования IP для больших эталонных проектов, которые имеют значительное время синтеза. Например, эталонная конструкция HDL Coder™ Default video system (requires HDMI FMC module) является потенциальным кандидатом на кэширование IP.

Примечание

Speedgoat IO333-325K , которая используется с Simulink Real-Time FPGA I/O workflow поставляется с IP-кэшем. При первом запуске рабочего процесса генератор кода повторно использует этот IP-кэш, что увеличивает время синтеза ссылочной конструкции.

Чтобы включить кэширование IP, в помощнике по рабочим процессам HDL укажите IP Core Generation в качестве целевого рабочего процесса, а затем укажите параметры целевой платформы. Перед первым запуском рабочего процесса:

В задаче Создать проект установите флажок Включить кэширование IP-адресов.

При выполнении этой задачи рабочий процесс создает пустую папку IP-кэша. Вы можете видеть ipcache в папке hdl_prj/vivado_ip_prj путь.

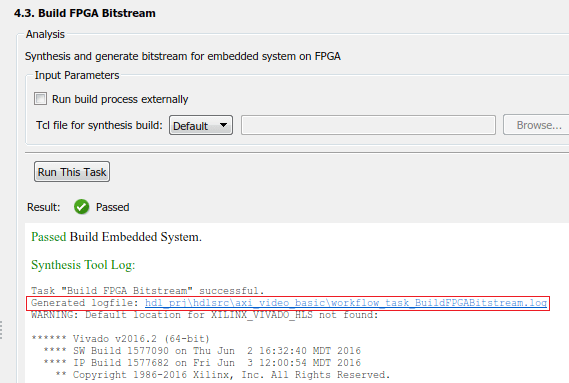

Запустите задачу создания битового потока FPGA.

Эта задача заполняет папку кэша IP журналами синтеза и файлами контрольных точек проекта, созданными для ядра IP HDL и других IP-блоков в эталонной конструкции. После успешного выполнения этой задачи созданные файлы можно просмотреть в ipcache папка.

При запуске IP Core Generation Во второй раз в задаче Bitstream Build FPGA можно увидеть улучшение времени выполнения задачи. Убедитесь, что используются одинаковые IP-параметры и hdl_prj при первом запуске рабочего процесса. После успешного выполнения этой задачи, чтобы узнать, использовался ли кэш IP-адресов в рабочем процессе, откройте workflow_task_buildFPGABitstream.log файл.

Этот фрагмент кода показывает, что проект Vivado запускает максимальное количество заданий для синтеза конструкции и повторного использования IP-модулей в папке IP-кэша. Вы можете видеть, что cacheID IP-модулей соответствуют именам файлов подпапок в ipcache папка.

... # reset_run impl_1 # reset_run synth_1 # launch_runs -jobs 4 synth_1 ... ... ... INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_RGBtoYCbCr_0_0, cacheID = 3575924730488800 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_YCbCrtoRGB_0_0, cacheID = e71459f41e26e141 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_xbar_0, cacheID = d0f0971cb77bcaed INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_axis2hdmi_0_0, cacheID = 7601a322f9fd0ec4 ...

При использовании собственной пользовательской конструкции ссылки кэширование IP-адресов может ускорить синтез конструкции ссылки при первом запуске рабочего процесса. Чтобы повторно использовать IP-кэш, создайте zip-файл IP-кэша, а затем убедитесь, что файл определения конструкции ссылки указывает на этот zip-файл.

Чтобы создать zIP-файл кэша, выполните следующие действия.

Откройте помощник по рабочим процессам HDL для любой модели Simulink ®, которая имеет подсистему DUT, а затем запустите рабочий процесс создания IP-ядра, чтобы создать код RTL и задачу IP-ядра.

В задаче Создать проект установите флажок Включить кэширование IP-адресов и нажмите кнопку Запустить эту задачу. Эта задача создает пустую папку IP-кэша.

Запустите рабочий процесс для задачи создания битового потока FPGA. Эта задача заполняет кэш IP ядром IP HDL и эталонными проектными IP-модулями.

В папке IP-кэша удалите базовые файлы IP, созданные для DUT. Извлечь оставшиеся файлы из этой папки в zip-файл и присвоить ему имя ipcache.zip, а затем сохраните файл в папке ссылочного проекта.

Для повторного использования IP-кэша в файле определения ссылочного проекта plugin_rd.m, используйте IPCacheZipFile имущества hdlcoder.ReferenceDesign класс. Используя это свойство, вы добавляете ipcache.zip файл в проект Xilinx Vivado.

function hRD = plugin_rd() % Reference design definition hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); % ... % ... hRD.IPCacheZipFile = 'ipcache.zip';

hdlcoder.Board | hdlcoder.ReferenceDesign