Пользовательский отчет по IP-ядру создается по умолчанию при создании пользовательского IP-ядра. Отчет описывает поведение и содержимое созданного пользовательского IP-ядра.

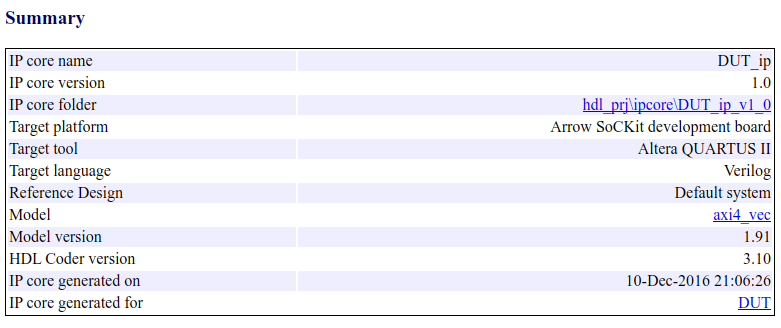

В разделе Сводка показаны настройки кодера при создании пользовательского ядра IP.

На следующем рисунке приведен пример раздела Сводка.

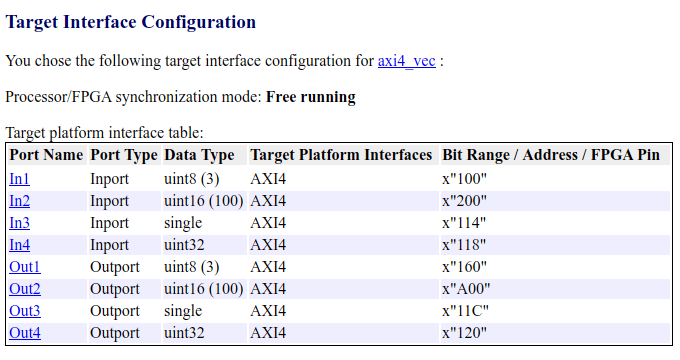

В разделе «Настройка целевого интерфейса» показано, как порты DUT сопоставляются с целевым аппаратным интерфейсом и режимом синхронизации процессора/FPGA.

На следующем рисунке приведен пример раздела «Настройка целевого интерфейса».

Дополнительные сведения о режимах синхронизации процессора/FPGA см. в разделе Синхронизация процессора и FPGA.

Дополнительные сведения об интерфейсах целевой платформы см. в разделе Пользовательское поколение IP Core.

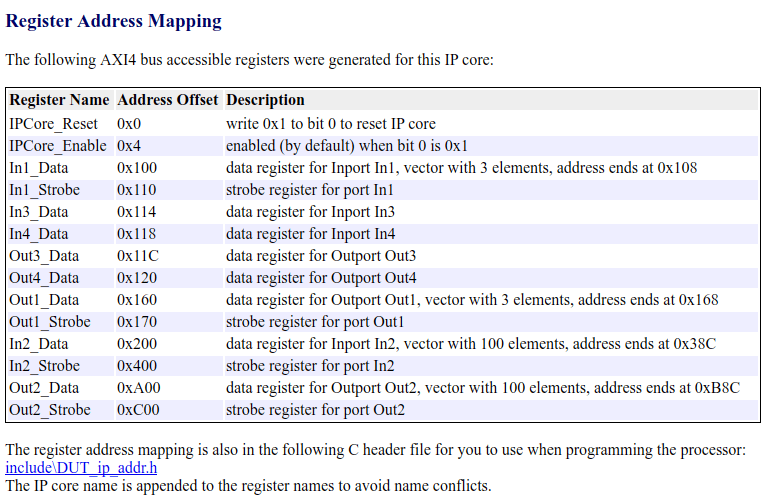

В разделе Register Address Mapping показаны смещения адресов для регистров AXI4-Lite доступных для шины в пользовательском IP-ядре, а также имя файла заголовка C, содержащего те же смещения адресов.

На следующем рисунке приведен пример раздела «Сопоставление адресов регистров».

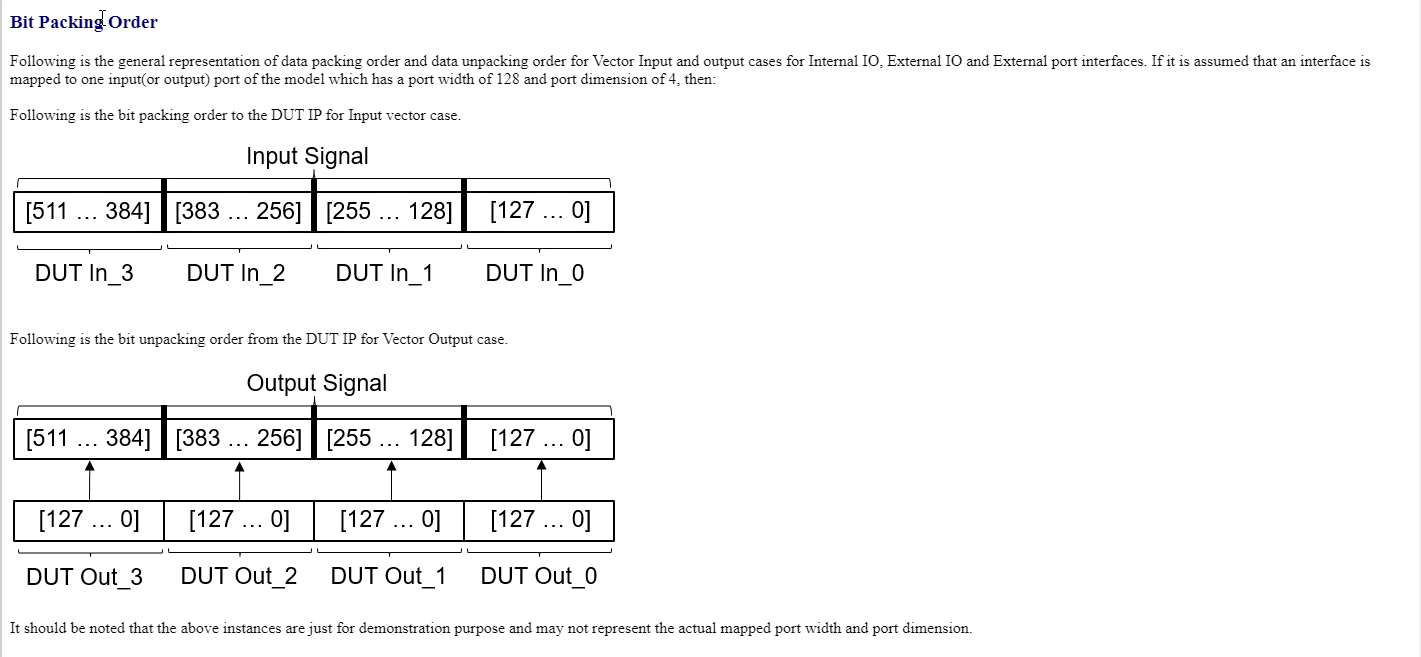

В разделе Bit Packing Order представлен общий обзор заказа на упаковку данных для векторных входов и выходов для интерфейсов внутреннего ввода-вывода, внешнего ввода-вывода и внешнего порта. Этот раздел появляется только в том случае, если ширина порта для внутренних портов ввода-вывода, внешних портов ввода-вывода и внешних портов превышает 128 бит в ширину.

Это изображение является примером раздела «Заказ на упаковку битов»:

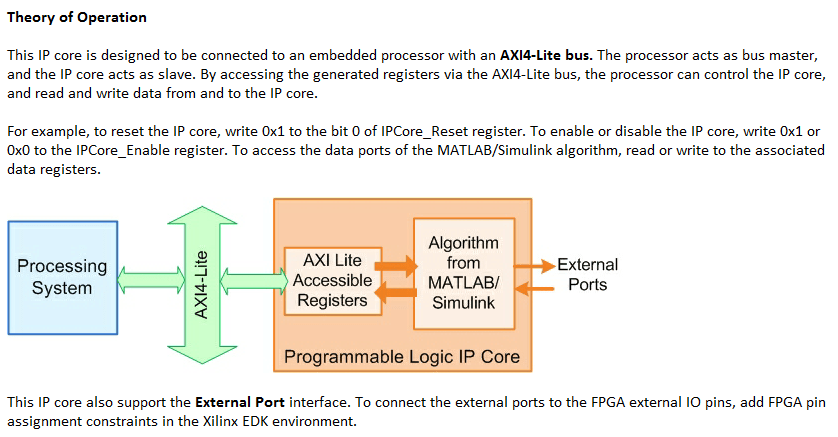

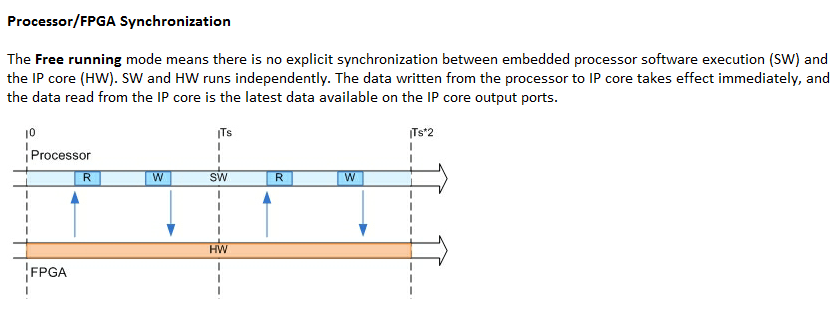

В разделе Руководство пользователя IP Core представлен общий обзор архитектуры системы, описывается режим синхронизации процессора и FPGA, а также даются инструкции по интеграции IP core в встроенную среду системной интеграции.

На следующем рисунке приведен пример описания архитектуры IP Core User Guide.

На следующем рисунке приведен пример описания синхронизации процессора/FPGA.

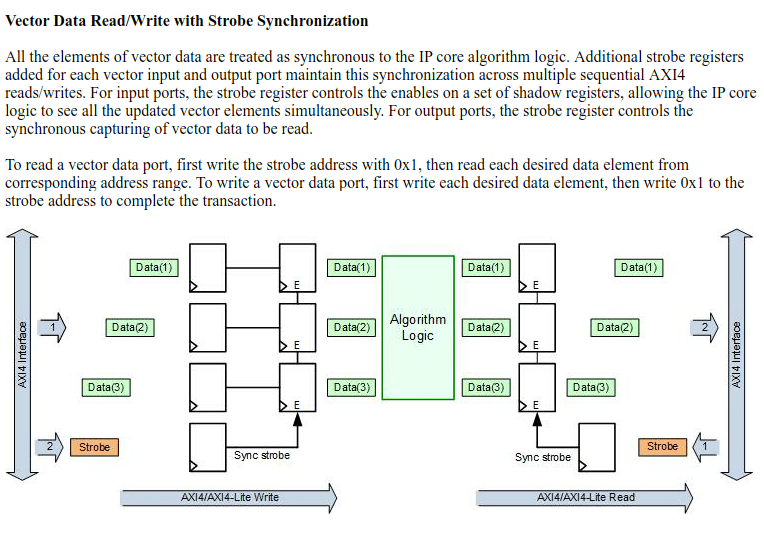

При использовании сигналов векторных данных в интерфейсе DUT в базовом отчете IP отображается этот раздел, в котором показано, как генератор кода синхронизирует векторные данные через интерфейс AXI4.

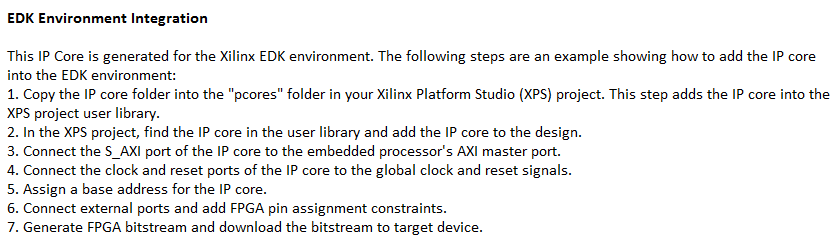

На следующем рисунке приведен пример инструкций по интеграции ядра IP во встроенную среду системной интеграции на платформе Xilinx ®. При использовании платформы Altera ® в отчете отображаются аналогичные инструкции по интеграции ядра IP в среду Altera Qsys.

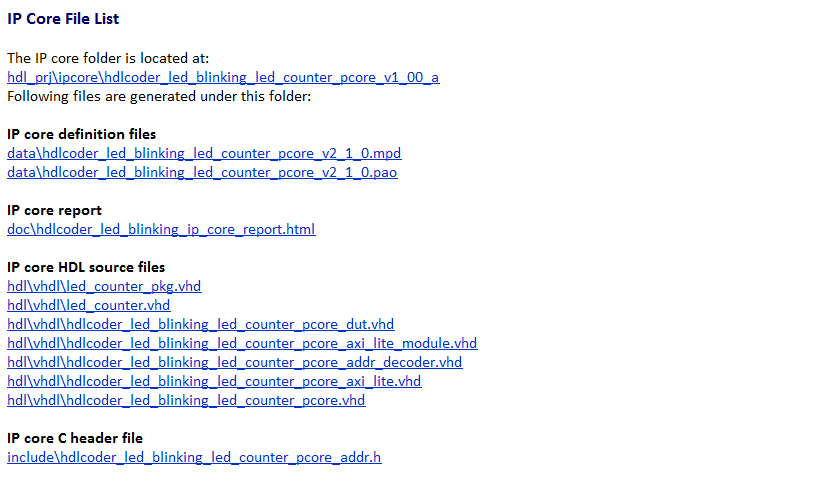

В разделе IP Core File List перечислены файлы и папки, входящие в состав пользовательского IP-ядра.

На следующем рисунке приведен пример списка основных IP-файлов.