Откройте мастер FPGA-in-the-loop, выбрав один из следующих методов вызова:

В окне команды MATLAB введите следующее:

>> filWizard

На панели инструментов Simulink ® на вкладке «Приложения» в разделе «Проверка кода, проверка и тестирование» щелкните Мастер FIL.

Для восстановления предыдущего сеанса используйте следующую команду:

filWizard('./Subsystem_fil/Subsystem_fil.mat')

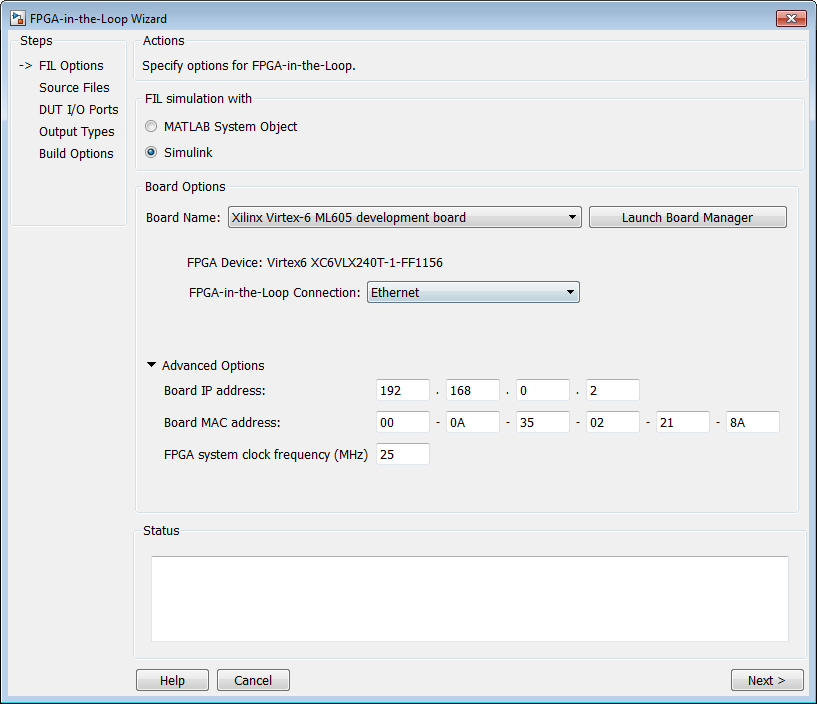

На странице Параметры FIL:

Моделирование FIL: Выбрать Simulink.

Имя платы: Выберите плату разработки FPGA. Если пакет поддержки плат HDL Verifier™ FPGA еще не загружен, см. раздел Загрузка пакета поддержки плат FPGA. (Если нет ни одной из перечисленных плат, пакет поддержки еще не загружен). Если вы планируете самостоятельно определить пользовательскую плату, см. раздел Настройка платы FPGA.

FPGA-in-the-Loop Connection: метод имитационного соединения FIL. Опции раскрывающегося меню обновляются в зависимости от методов подключения, поддерживаемых для выбранной целевой платы. Если целевая плата и HDL Verifier поддерживают подключение, можно выбрать Ethernet, JTAG, или PCI Express.

Дополнительные параметры:

При выборе соединения Ethernet при необходимости можно настроить IP-адрес и MAC-адрес платы.

| Выбор | Инструкции |

|---|---|

| IP-адрес платы | Используйте эту опцию для установки IP-адреса платы, если он не является IP-адресом по умолчанию (192.168.0.2). Если IP-адрес платы по умолчанию (192.168.0.2) используется другим устройством или требуется другая подсеть, измените IP-адрес платы в соответствии со следующими рекомендациями:

|

| MAC-адрес платы | В большинстве случаев изменение MAC-адреса платы не требуется. При подключении нескольких плат разработки FPGA к одному хост-компьютеру измените MAC-адрес платы для любых дополнительных плат таким образом, чтобы каждый адрес был уникальным. Для каждой платы необходимо иметь отдельную сетевую плату. Для изменения MAC-адреса платы щелкните в поле Board MAC address. Укажите адрес, отличный от адреса любого другого устройства, подключенного к компьютеру. Для получения MAC-адреса платы для конкретной платы разработки FPGA обратитесь к этикетке, прикрепленной к плате, или обратитесь к документации по продукции. |

Тактовая частота системы FPGA (МГц): Введите целевую тактовую частоту. Для системных плат Intel и плат, поддерживаемых Xilinx ISE, filWizard проверяет запрашиваемую частоту относительно возможных для запрашиваемой платы. Если запрошенная частота невозможна для данной платы, filWizard возвращает ошибку и предлагает альтернативную частоту. Для плат Xilinx Vivado или PCI Express ® ,filWizard не удается проверить частоту. Инструменты синтеза делают наилучшую попытку на требуемой частоте, но могут выбрать альтернативную частоту, если указанная частота не была достижимой. Значение по умолчанию: 25 МГц.

Нажмите кнопку Далее.

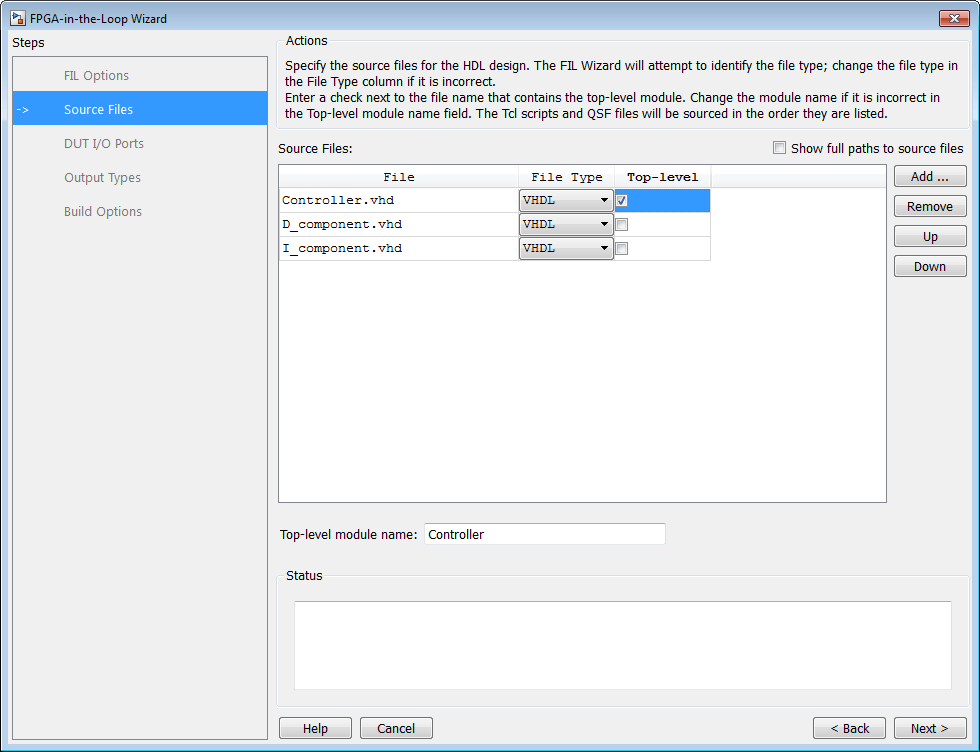

На странице Исходные файлы:

Укажите конструкцию ЛПВП, которая будет косимулирована в FPGA. Эти файлы представляют собой файлы дизайна HDL, которые должны быть проверены на плате FPGA.

Укажите исходные файлы, нажав кнопку «» Добавить «». Выберите файлы в диалоговом окне выбора файлов.

Мастер FIL пытается определить типы исходных файлов. Если какой-либо из типов файлов не соответствует ожидаемому, его можно изменить, выбрав в выпадающем списке Тип файла. Допустимые типы файлов:

VHDL ®

Verilog ®

Netlist

Сценарий Tcl

Ограничения

Другие

«Прочие» означают следующее:

Для Intel файлы указаны как Other добавляются в проект FPGA, но не влияют на созданный блок. Например, можно поместить некоторые комментарии в readme и включить его в этот список файлов.

Для Xilinx файлы указаны как Other может быть любым файлом, принятым Xilinx ISE. ISE просматривает расширение файла, чтобы определить, как использовать этот файл. Например, при добавлении foo.vhd в список и укажите его как OtherISE обрабатывает файл как файл VHDL.

Укажите, какой файл содержит файл HDL верхнего уровня.

Установите флажок в строке файла HDL, содержащего модуль HDL верхнего уровня, в столбце Top-level. Мастер FIL автоматически заполняет поле Имя модуля верхнего уровня именем выбранного файла HDL. Если имя модуля верхнего уровня и имя файла не совпадают, можно вручную изменить имя модуля верхнего уровня в этом диалоговом окне. Перед продолжением укажите имя модуля верхнего уровня.

(Необязательно) Для отображения полных путей к исходным файлам установите флажок «Показать полные пути к исходным файлам».

Нажмите кнопку Далее.

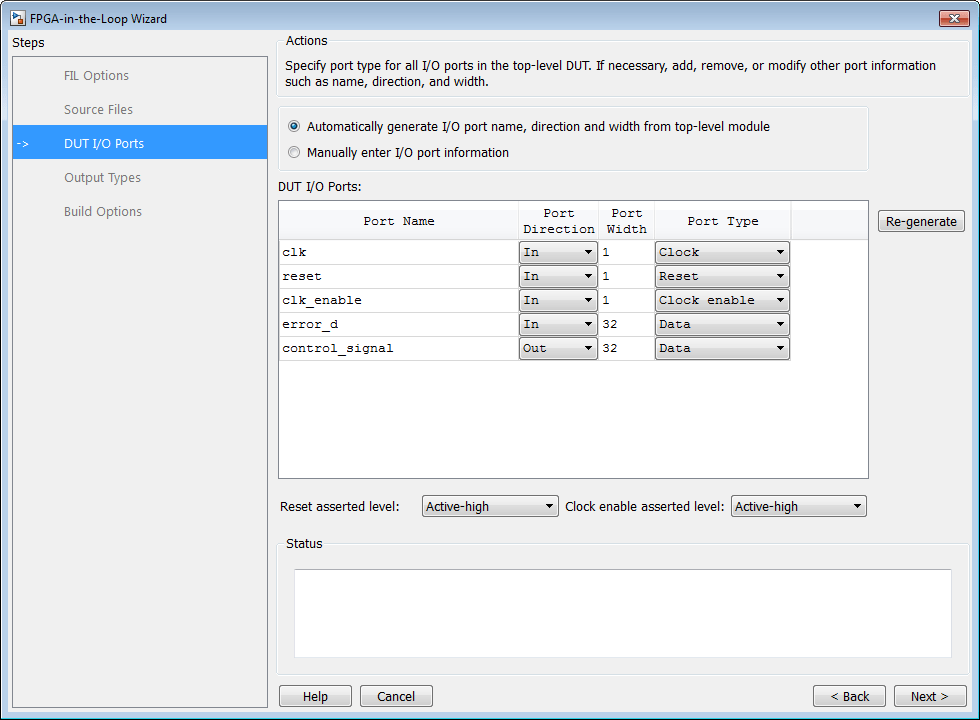

На странице Порты ввода/вывода DUT:

Просмотрите список портов. Мастер FIL анализирует модуль HDL верхнего уровня для получения всех портов ввода/вывода и отображения их в таблице портов ввода/вывода DUT. Синтаксический анализатор пытается определить типы портов из имен портов. Затем мастер отображает эти сигналы в разделе Port Type.

Убедитесь, что все порты/часы ввода/вывода/сброса отображены в соответствии с ожиданиями. Если синтаксический анализатор назначил неверный тип порта для любого порта, можно вручную изменить сигнал. Для синхронного проектирования укажите тактовый сигнал, сброс или, при необходимости, сигнал включения тактового сигнала. Типы портов, указанные в этой таблице, должны совпадать с типами портов в коде HDL. Должен быть хотя бы один выходной порт.

Выберите Manually enter port information для добавления или удаления сигналов.

Щелкните Регенерировать (Regenerate), чтобы перезагрузить таблицу с исходными определениями портов (из кода HDL).

Нажмите кнопку Далее.

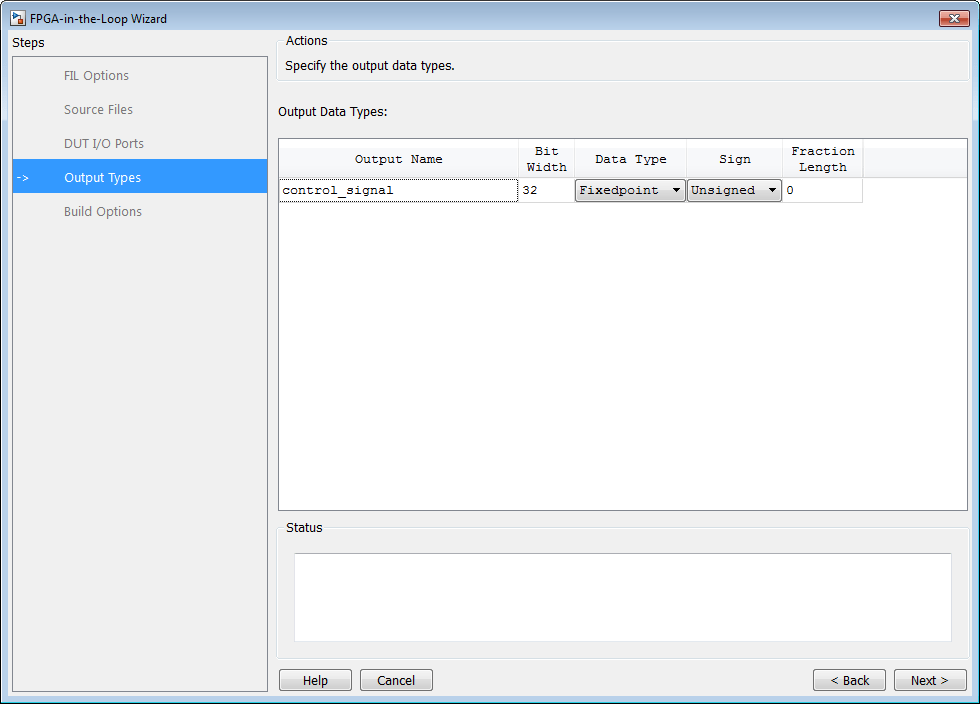

На странице «Типы вывода»:

Укажите типы выходных данных. Мастер назначает типы данных. Если какой-либо тип выходных данных не соответствует ожидаемому, измените тип вручную.

Выберите из:

Fixedpoint

Integer

Logical

Тип данных может зависеть от заданной ширины бита.

Можно указать тип вывода Signed, Unsigned, или Fraction Length.

Нажмите кнопку Далее.

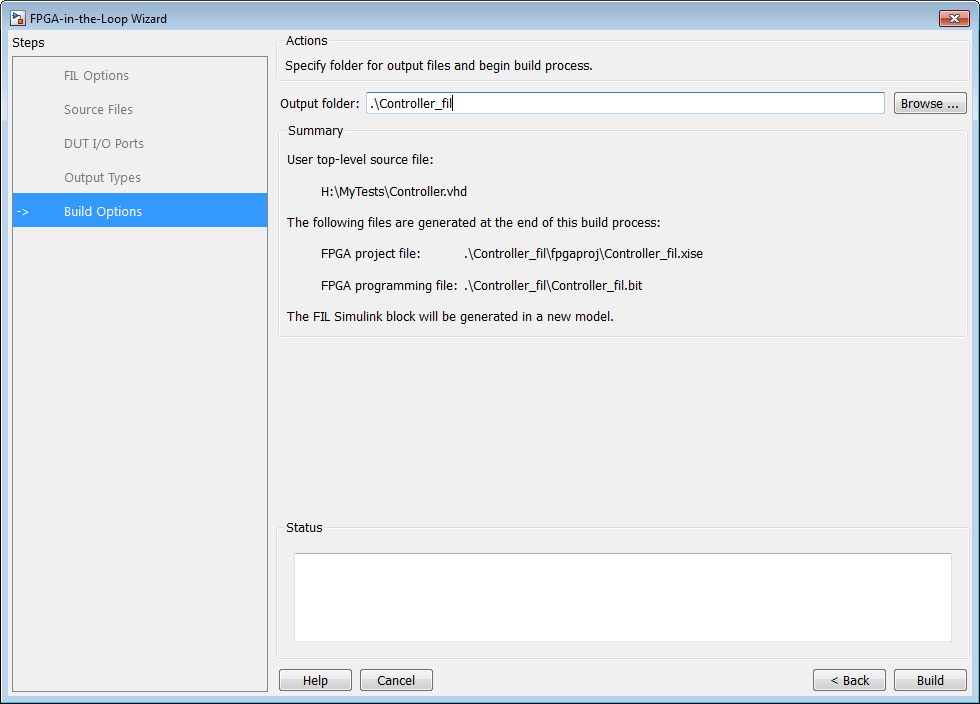

На странице «Параметры построения»:

Укажите папку для выходных файлов. Можно использовать опцию по умолчанию. Обычно по умолчанию используется подпапка с именем модуля верхнего уровня, расположенная под текущей папкой.

В окне Сводка отображаются расположения файла проекта ISE и файла программирования FPGA. Эти два файла могут понадобиться для расширенных операций с маской блока FIL.

Щелкните Создать (Build), чтобы инициировать формирование блока FIL.

Мастер FIL создает блок FIL с именем модуля верхнего уровня и помещает его в новую модель.

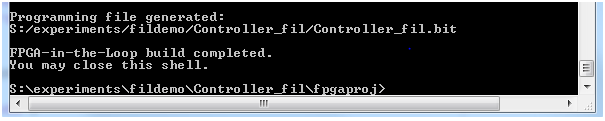

Мастер FIL открывает окно команд.

В этом окне программное обеспечение разработки FPGA выполняет генерацию файлов программирования синтеза, подгонки, PAR и FPGA.

После завершения процесса в окне команд появится сообщение с предложением закрыть окно.

В модели замените подсистему DUT блоком FIL, созданным в новой модели. Сохраните модель под другим именем. Затем можно использовать исходную модель в качестве ссылочной.

Если блок FIL был создан консультантом по рабочим процессам HDL, вряд ли потребуется корректировать какие-либо настройки блока FIL. При создании блока FIL с помощью мастера FIL может потребоваться изменить некоторые настройки. Инструкции по настройке параметров блока FIL см. в разделе Моделирование FIL.

Инструкции для системных плат Intel для Linux

Инструкции для системных плат Intel для Linux

Убедитесь, что плата разработки FPGA установлена, включена и подключена к компьютеру с помощью кабеля JTAG. При программировании используется интерфейс JTAG, даже если для моделирования выбрано другое соединение.

Выполните следующие действия для программирования FPGA:

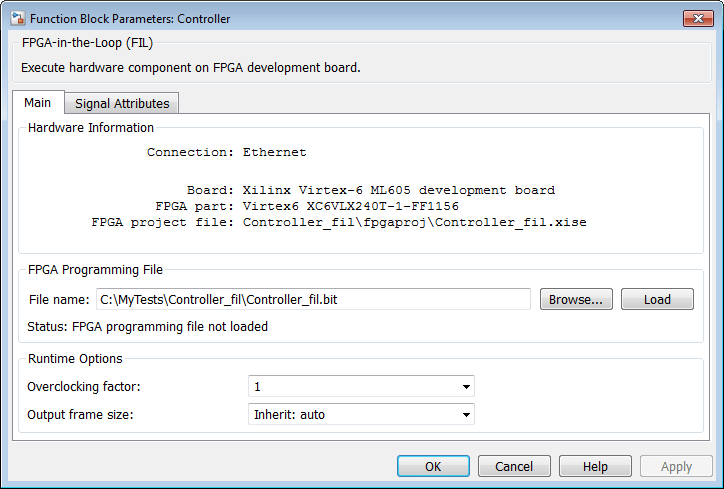

Дважды щелкните блок FIL в модели Simulink, чтобы открыть маску блока.

На вкладке Main (Главная) нажмите Load (Загрузить), чтобы загрузить файл программирования в FPGA через кабель JTAG.

Процесс загрузки может занять от нескольких минут до нескольких минут или дольше, в зависимости от размера подсистемы. Иногда процесс может занять полтора часа или больше для больших подсистем.

Окно сообщения указывает, когда файл программирования FPGA загружен так, как ожидалось. Нажмите кнопку ОК.

В Simulink запустите модель, включающую блок моделирования FIL. Результаты моделирования FIL должны совпадать с результатами эталонной модели Simulink или исходного кода HDL.

Примечание

RAM Initialization: Simulink начинается с момента 0 каждый раз, что означает, что RAM в модели Simulink инициализируется как ноль для каждого прогона. Однако это предположение неверно для аппаратных средств. Оперативная память в FPGA сохраняет свое значение от конца одного моделирования до начала следующего. Если в конструкции имеется ОЗУ, первое моделирование соответствует Simulink, но последующие запуски могут не совпадать. Обходным путем является перезагрузка битового потока FPGA перед повторным запуском моделирования. Чтобы перезагрузить поток битов, нажмите кнопку Load на маске блока FIL.