Моделирование FPGA-in-the-loop (FIL) обеспечивает возможность использования программного обеспечения Simulink ® или MATLAB ® для тестирования конструкций в реальном оборудовании для любого существующего кода HDL. Код HDL может быть написан вручную или сгенерирован программным обеспечением из подсистемы модели.

Для выполнения моделирования FIL необходимо иметь код HDL. Существует два рабочих процесса FIL:

Существует код HDL (мастер FIL).

Примечание

Мастер FIL использует любой синтезируемый код HDL, включая код, автоматически генерируемый из моделей Simulink программным обеспечением HDL Coder™

Имеется код MATLAB или модель Simulink и лицензия HDL Coder (консультант по рабочим процессам HDL).

Примечание

При использовании FIL в консультанте по рабочим процессам кодер HDL использует загруженную конструкцию для создания кода HDL.

Независимо от выбранного потока операций при создании блока или системного object™ FIL выполняет следующие процессы:

Создает блок FIL или объект FIL System, представляющий код HDL

Обеспечивает синтез, логическое отображение, размещение и маршрутизацию (PAR), генерацию файлов программирования и канал связи.

Загружает конструкцию в FPGA

Все эти возможности разработаны для конкретной платы и адаптированы к коду RTL.

Как часть моделирования FIL, блок или системный объект и модель или приложение:

Передача данных от Simulink или MATLAB в FPGA

Получение данных из FPGA

Выполняет дизайн в реальной среде

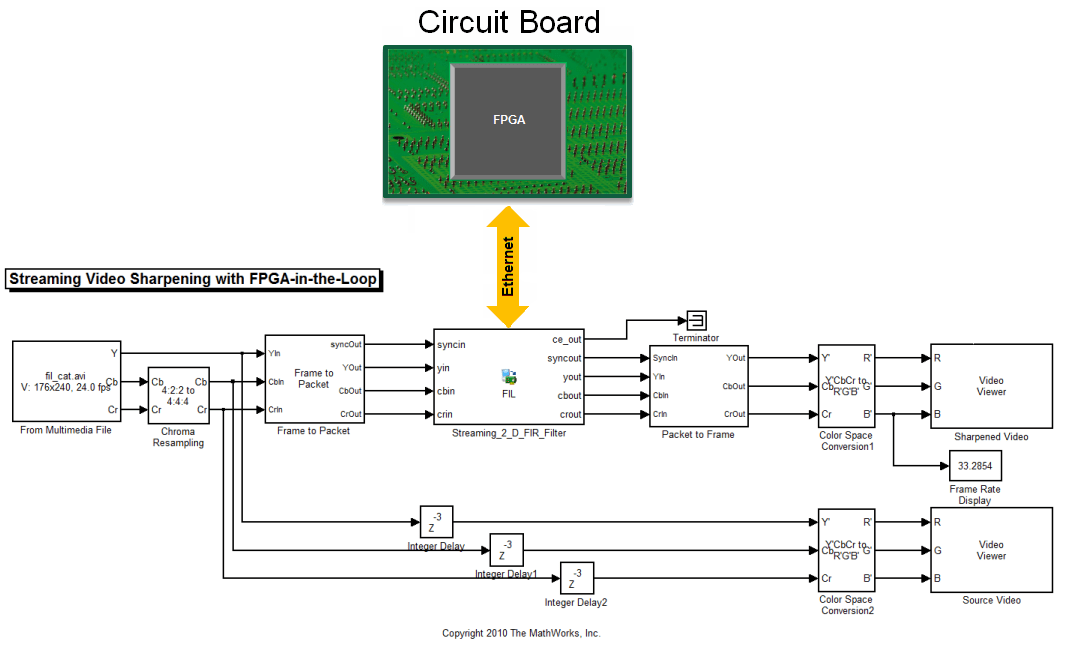

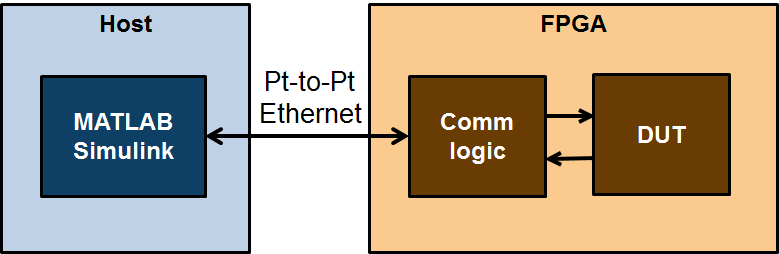

Связи FIL. На следующем рисунке показано взаимодействие HDL Verifier™ между Simulink и платой FPGA с помощью моделирования FIL.

Примечание

Программа HDL Verifier предполагает, что к главному компьютеру подключен только один кабель загрузки и что программное обеспечение программирования FPGA может автоматически обнаружить это подключение. Если нет, используйте программное обеспечение программирования FPGA для программирования FPGA с правильными опциями.

Вид на уровне системы. Все операции ввода-вывода DUT направляются в Simulink через логику связи FIL.

FIL обеспечивает канал связи для передачи и приема данных между Simulink и FPGA. Этот канал может быть подключением JTAG, Ethernet или PCI Express ®. Связь между Simulink и FPGA строго синхронизирована для обеспечения надежной среды проверки.

Для создания файла программирования FIL программное обеспечение выполняет следующие задачи:

Создает код HDL для указанного DUT и создает проект ISE.

Вместе с программным обеспечением FPGA, синтезирует, отображает, размещает и создает файл программирования для FPGA.

Загрузка файла программирования в FPGA на плате разработки через обычное конфигурационное соединение. Как правило, это соединение представляет собой последовательную линию через кабель USB (для получения информации о подключении см. руководство пользователя платы).

Для блоков моделирования FIL нажатие кнопки «Загрузить» на маске блока FIL инициирует загрузку файла программирования.

Для объектов системы моделирования FIL: programFPGA инициирует загрузку файла программирования.

Для моделирования FIL необходимо подготовить следующие элементы или информацию:

Для мастера FIL:

Предоставьте код HDL (написанный вручную или сгенерированный программным обеспечением) для проекта, который вы планируете протестировать.

Выберите файлы HDL и укажите имя модуля верхнего уровня.

Проверьте настройки портов и убедитесь, что мастер FIL определил входные и выходные сигналы и размеры сигналов.

Если используется Simulink, предоставьте модель Simulink, готовую для получения сгенерированного блока FIL.

Для помощника по рабочим процессам HDL:

Можно создать код и запустить FIL из любой подходящей модели Simulink. Следовать рабочему процессу для FPGA-in-the-Loop. См. раздел FIL Simulation with HDL Workflow Advisor for Simulink. Код MATLAB см. в рабочем процессе, описанном в разделе Моделирование FIL с помощью помощника по рабочим процессам HDL для MATLAB.