Следуйте инструкциям для вызова помощника по рабочим процессам HDL. См. раздел Начало работы с консультантом по рабочим процессам HDL (кодер HDL).

Примечание

Для создания кода HDL с помощью помощника по рабочим процессам HDL необходимо иметь лицензию HDL Coder™.

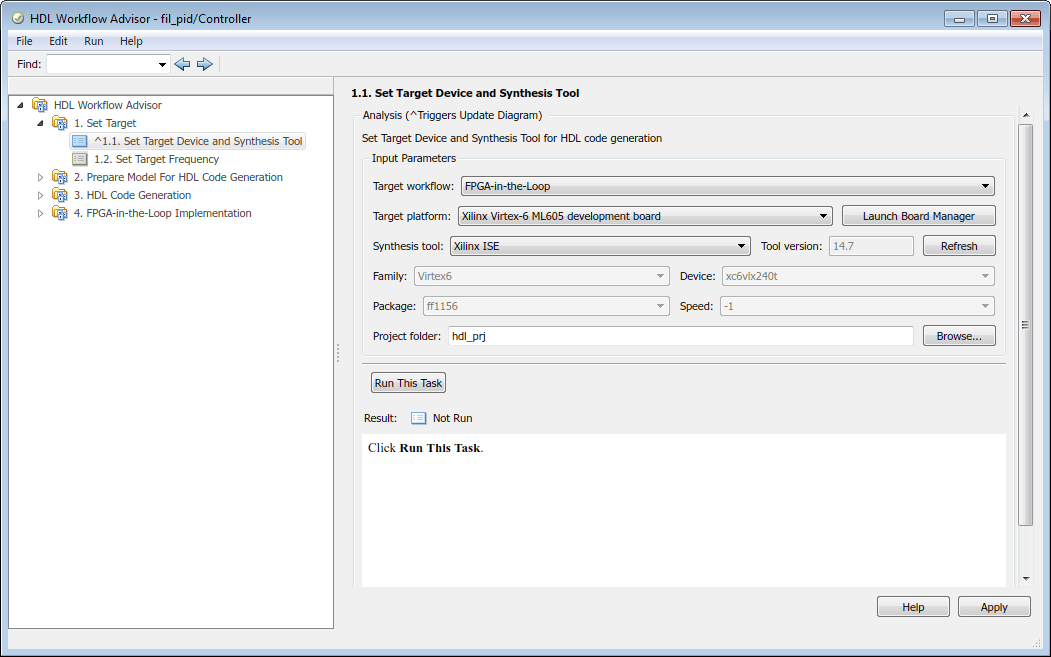

На шаге 1, Set Target, щелкните 1.1 Set Target Device and Synthesis Workflow и выполните следующие действия.

Выбрать FPGA-in-the-Loop из выпадающего списка в целевом рабочем процессе.

В разделе Целевая платформа выберите плату разработки из выпадающего списка. Семейство, устройство, пакет и скорость заполняются консультантом по рабочим процессам HDL. Если пакет поддержки платы HDL Verifier™ FPGA еще не загружен, выберите Get more boards. Затем вернитесь к этому шагу после загрузки пакета поддержки платы FPGA.

В поле «Папка» введите имя папки для сохранения файлов проекта. Значение по умолчанию: hdl_prj в текущей рабочей папке.

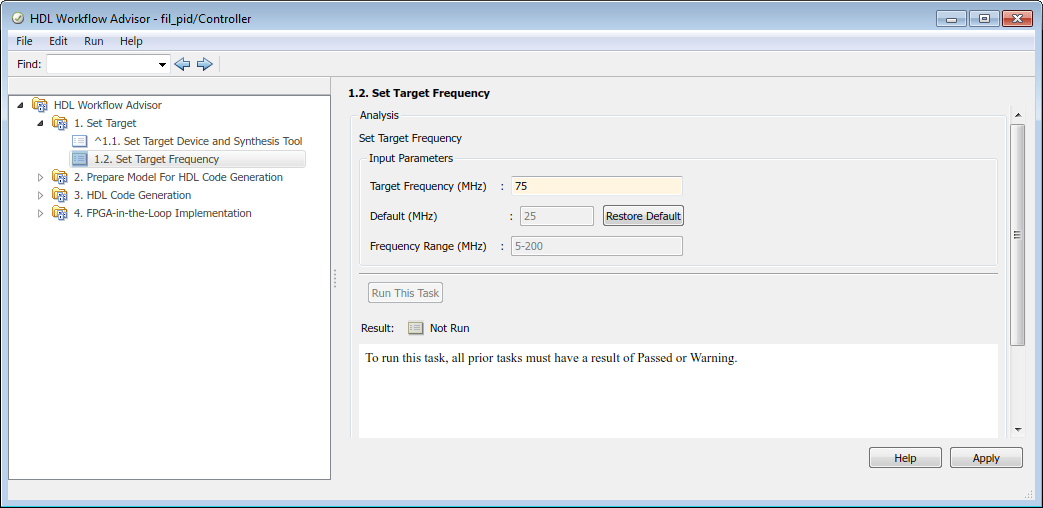

После выбора цели FIL на шаге 1.1 щелкните 1.2 Задать целевую частоту (Set Target Frequency).

Установите целевую частоту (МГц) для тактовой частоты вашей конструкции, реализованной на FPGA. Доступный диапазон частот отображается в параметре Frequency Range (MHz). Для системных плат Intel ® и плат Xilinx ® Workflow Advisor проверяет запрашиваемую частоту на соответствие требуемой системной плате. Если запрошенная частота для этой платы невозможна, помощник по рабочим процессам возвращает ошибку и предлагает альтернативную частоту. Для поддерживаемых плат Xilinx Vivado ® или плат PCI Express ® помощник по рабочим процессам не может проверить частоту. Инструменты синтеза делают наилучшую попытку на требуемой частоте, но могут выбрать альтернативную частоту, если указанная частота не была достижимой. Значение по умолчанию:25 МГц.

На шаге 2, Подготовка модели для генерации кода ЛПВП, выполните шаги 2.1-2.4, как описано в разделе Подготовка модели для создания кода ЛПВП (кодер ЛПВП).

Кроме того, выполните шаг 2.5 Проверка совместимости FPGA-in-the-Loop для проверки совместимости модели с FIL.

На шаге 3, Создание кода HDL, выполните шаги 3.1 и 3.2, как описано в разделе Обзор создания кода HDL (Кодер HDL).

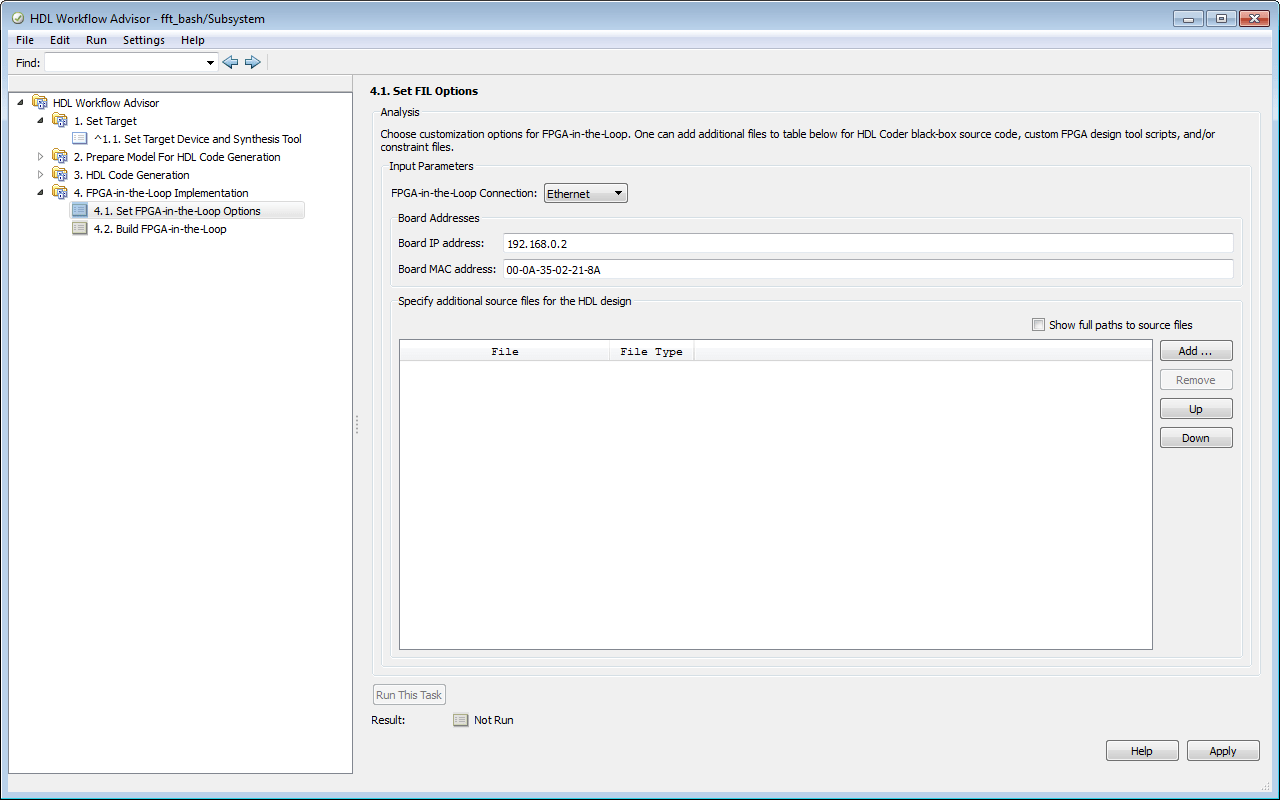

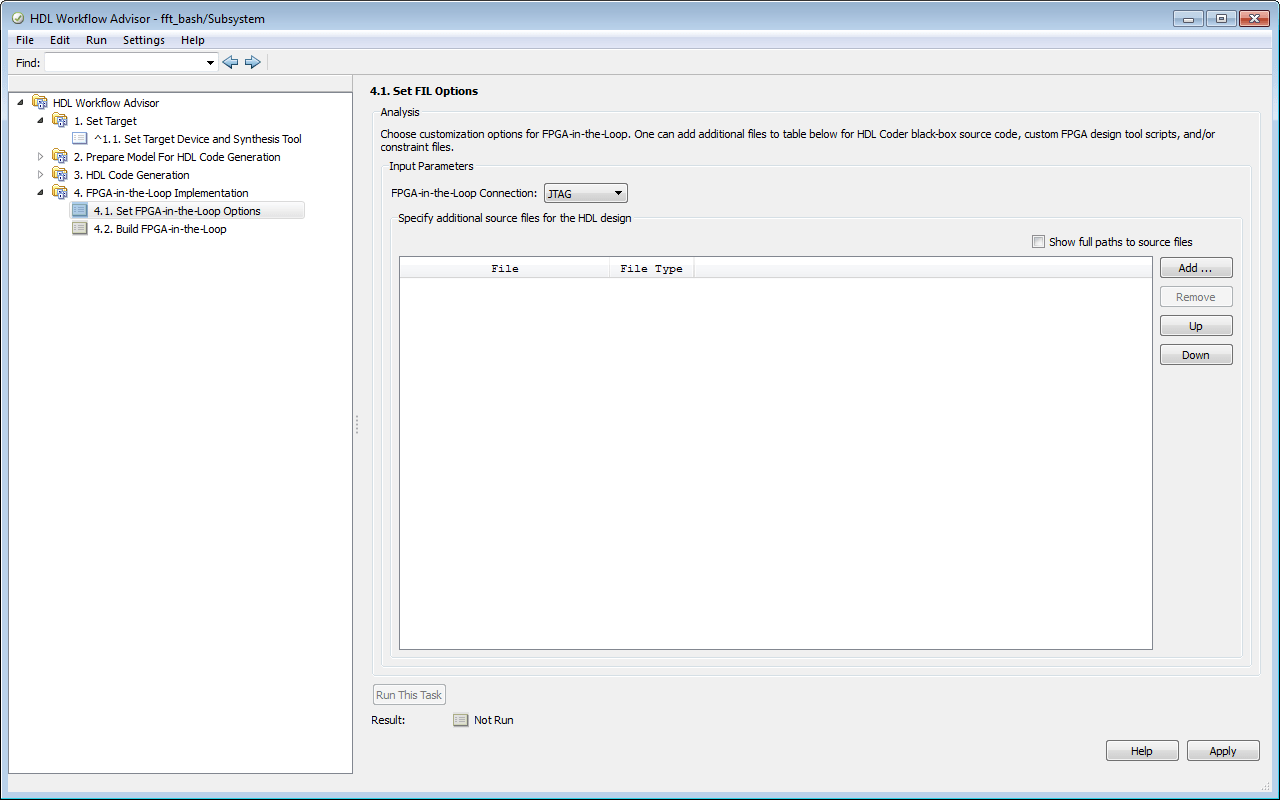

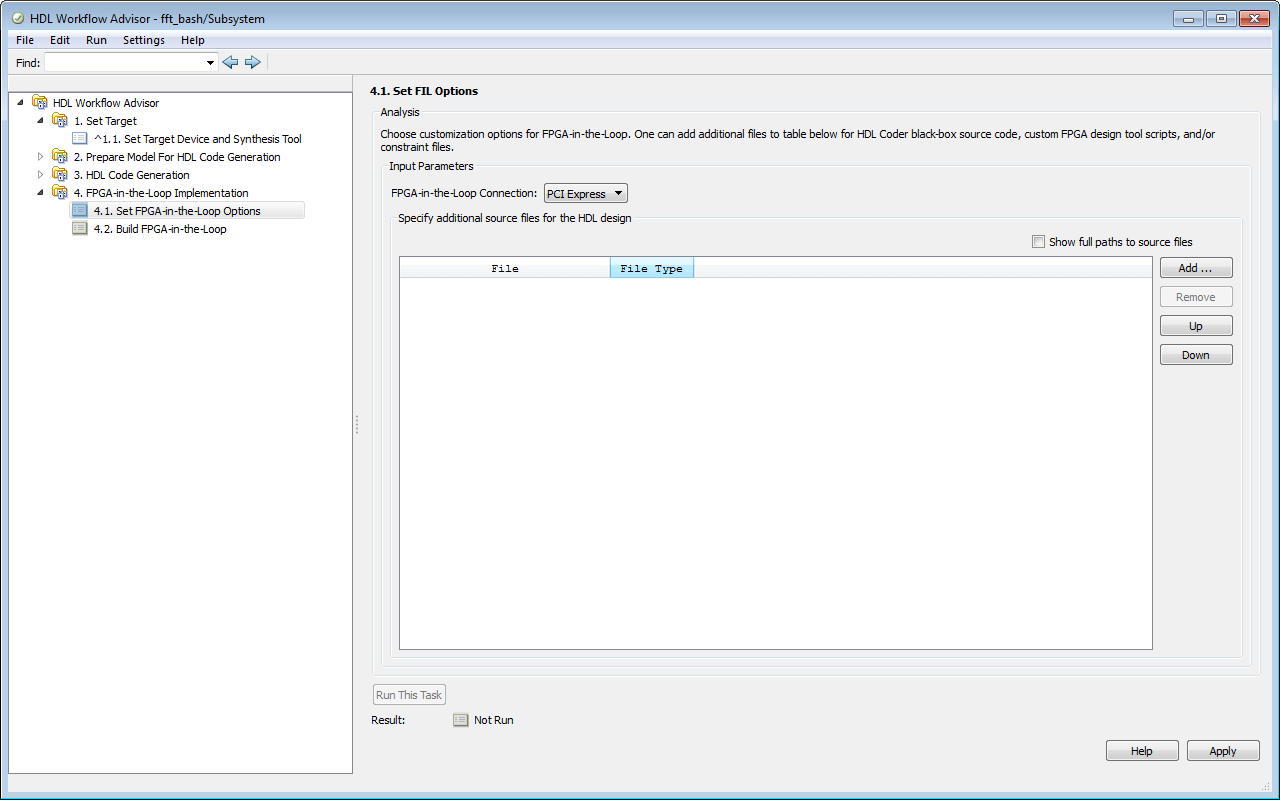

На шаге 4.1 (Set FPGA-in-the-Loop Options) при необходимости измените следующие параметры:

FPGA-in-the-Loop Connection: метод имитационного соединения FIL. Опции раскрывающегося меню обновляются в зависимости от методов подключения, поддерживаемых для выбранной целевой платы. Если целевая плата и HDL Verifier поддерживают подключение, можно выбрать Ethernet, JTAG, или PCI Express.

Адрес платы:

При выборе соединения Ethernet при необходимости можно настроить IP-адрес и MAC-адрес платы.

| Выбор | Инструкции |

|---|---|

| IP-адрес платы | Используйте эту опцию для установки IP-адреса платы, если он не является IP-адресом по умолчанию (192.168.0.2). Если IP-адрес платы по умолчанию (192.168.0.2) используется другим устройством или требуется другая подсеть, измените IP-адрес платы в соответствии со следующими рекомендациями:

|

| MAC-адрес платы | В большинстве случаев изменение MAC-адреса платы не требуется. При подключении нескольких плат разработки FPGA к одному хост-компьютеру измените MAC-адрес платы для любых дополнительных плат таким образом, чтобы каждый адрес был уникальным. Для каждой платы необходимо иметь отдельную сетевую плату. Для изменения MAC-адреса платы щелкните в поле Board MAC address. Укажите адрес, отличный от адреса любого другого устройства, подключенного к компьютеру. Для получения MAC-адреса платы для конкретной платы разработки FPGA обратитесь к этикетке, прикрепленной к плате, или обратитесь к документации по продукции. |

Укажите дополнительные исходные файлы для проекта HDL:

Укажите дополнительные исходные файлы для DUT с помощью Add. Чтобы (дополнительно) отобразить полные пути к исходным файлам, установите флажок Показать полные пути к исходным файлам. Помощник по рабочим процессам HDL пытается определить тип исходного файла. Если тип файла неверен, его можно изменить, выбрав в выпадающем списке Тип файла.

FIL по Ethernet

FIL над JTAG

FIL через PCI Express

На шаге 4.2, Build FPGA-in-the-Loop, щелкните Run this task.

В процессе построения выполняются следующие действия.

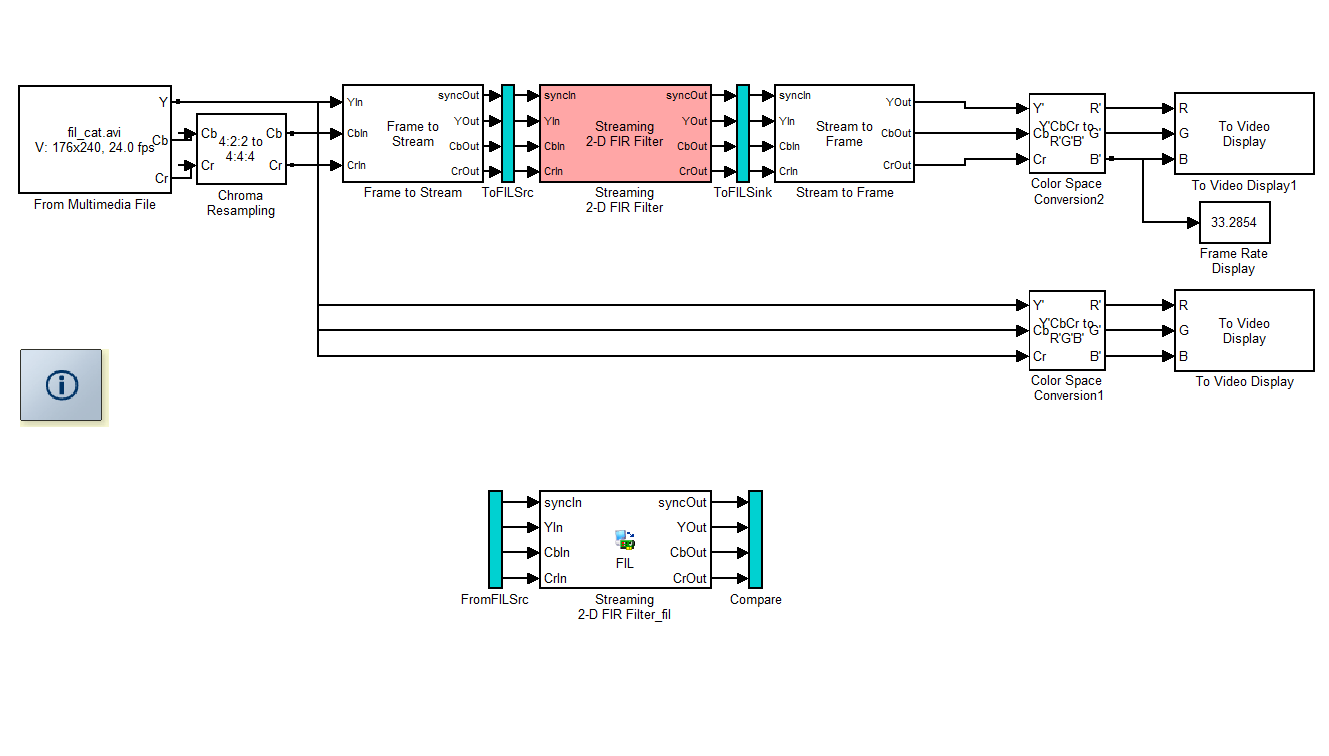

Помощник по рабочим процессам HDL создает блок FIL с именем модуля верхнего уровня и помещает его в новую модель. На следующем рисунке показан пример новой модели, содержащей блок FIL.

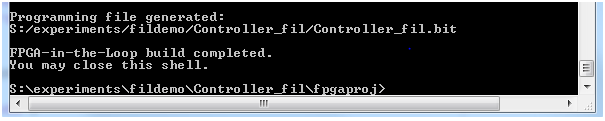

После создания новой модели помощник по рабочим процессам HDL открывает командное окно:

В этом окне программное обеспечение разработки FPGA выполняет генерацию файлов программирования синтеза, подгонки, PAR и FPGA.

После завершения процесса в окне команд появится сообщение с предложением закрыть окно.

Помощник по рабочим процессам HDL строит модель тестового стенда вокруг сгенерированного блока FIL.

Убедитесь, что плата разработки FPGA установлена, включена и подключена к компьютеру в соответствии с документацией производителя платы. Затем выполните следующие действия для программирования FPGA:

Дважды щелкните блок FIL в модели Simulink ®, чтобы открыть маску блока.

На вкладке Main (Главная) нажмите Load (Загрузить), чтобы загрузить файл программирования в FPGA.

Процесс загрузки может занять несколько минут в зависимости от размера подсистемы. Для очень больших подсистем процесс может занять час или больше.

Дополнительные советы по устранению неполадок см. в разделе Загрузка файла программирования в FPGA.

В окне Simulink на вкладке Simulation нажмите кнопку Run. Результаты моделирования FIL должны совпадать с результатами эталонной модели Simulink или исходного кода HDL.

Примечание

Что касается инициализации: Simulink начинается с времени 0 каждый раз, что означает, что RAM в Simulink инициализируется в ноль. Однако это не так в аппаратном обеспечении. Если в конструкции имеется ОЗУ, первое моделирование будет соответствовать Simulink, но любые последующие запуски могут не совпадать.

Обходным путем является перезагрузка битового потока FPGA перед повторным запуском моделирования. Для этого нажмите кнопку «Загрузить» на маске блока FIL.