С помощью мастера создания платы FPGA можно ввести всю необходимую информацию для добавления платы в список плат FPGA. Этот список применяется к рабочим процессам FIL и «под ключ». Ознакомьтесь с требованиями к плате FPGA перед добавлением платы FPGA, чтобы убедиться, что она совместима с рабочим процессом, для которого ее необходимо использовать.

Несколько кнопок мастера создания платы FPGA помогают в навигации:

Назад: Перейдите на предыдущую страницу для просмотра или редактирования уже введенных данных.

Далее: Перейти на следующую страницу, когда все требования текущей страницы будут выполнены.

Справка: Откройте Центр документов и просмотрите эту тему.

Отмена: выход из мастера создания платы FPGA. Можно выйти с сохранением или без сохранения информации из сеанса.

Однократное добавление плат для нескольких пользователей

Для глобального добавления новых плат выполните следующие инструкции. Для доступа к плате, добавляемой глобально, все пользователи должны использовать одну и ту же установку MATLAB ®.

Создайте следующую папку:

matlabroot/toolbox/shared/eda/board/boardfiles

Скопируйте XML-файл описания платы в boardfiles папка.

После копирования XML-файла перезапустите MATLAB. Новая плата отображается в списке плат FPGA для одного или обоих рабочих процессов FIL и «под ключ».

Все платы в этой папке автоматически отображаются в списке плат FPGA для пользователей с одинаковой установкой MATLAB. Для повторного добавления этих плат не требуется использовать FPGA Board Manager.

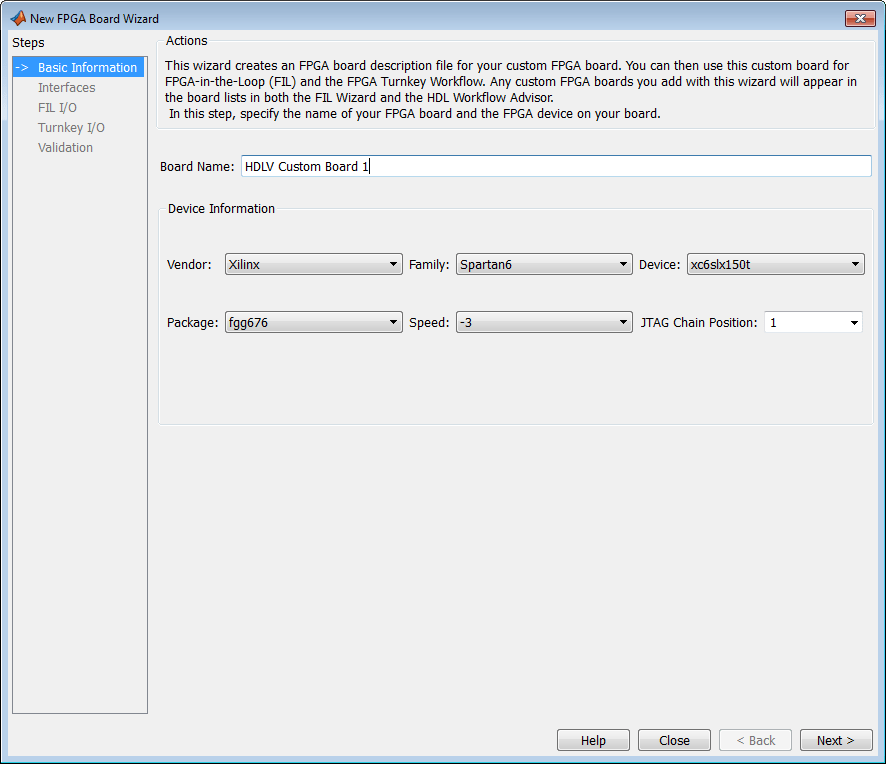

Процесс добавления платы FPGA состоит из следующих шагов:

Имя платы: введите уникальное имя платы.

Информация об устройстве:

Поставщик: Xilinx или Altera

Семейство: Семейство зависит от указанного поставщика. Соответствующие настройки см. в файле спецификаций платы.

Устройство: Используйте файл спецификации платы для выбора правильного устройства.

Только для системных плат Xilinx ®:

Пакет: выберите правильный пакет с помощью файла спецификации платы.

Скорость: выберите правильную скорость с помощью файла спецификации платы.

Позиция цепочки JTAG: значение указывает начальную позицию для цепочки JTAG. Для получения этой информации см. файл спецификации платы.

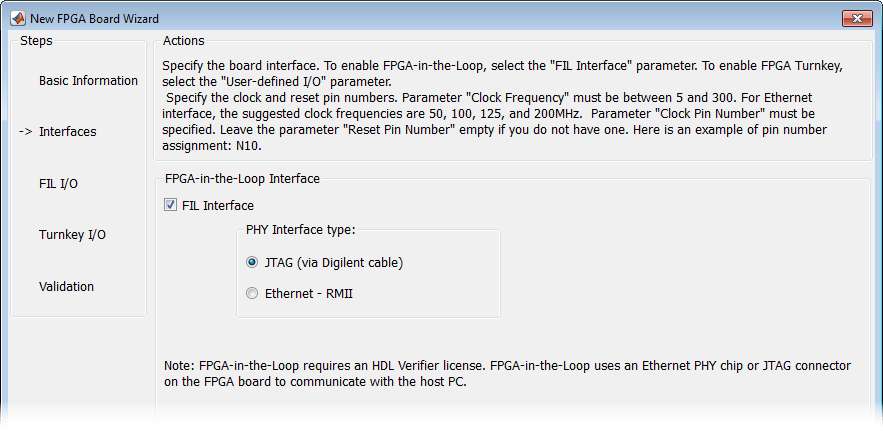

FPGA-in-the-Loop: для использования этой платы с FIL выберите FIL Interface.

Выберите один из следующих типов интерфейса PHY:

Гигабитный Ethernet - GMII

Гигабитный Ethernet - RGMII

Gigabit Ethernet - SGMII (опция SGMII появляется при выборе платы из семейств устройств Stratix ® V или Stratix IV)

Ethernet - MII

Altera JTAG (только для плат Altera ®)

Примечание

Не все интерфейсы доступны для всех плат. Доступность зависит от платы, выбранной в разделе «Основные сведения».

FPGA-in-the-Loop Interface: для использования этой платы с FIL выберите FIL Interface.

Выберите один из следующих типов интерфейса PHY:

JTAG (через кабель Digilent) (только платы Xilinx)

Ethernet - RMII

Примечание

Не все интерфейсы доступны для всех плат. Доступность зависит от платы, выбранной в разделе «Основные сведения».

Дополнительные сведения о настройке соединения JTAG для плат Xilinx см. в разделе JTAG с настройкой кабеля Digilent.

Ограничения. При моделировании конструкции FPGA с помощью кабеля Digilent ® JTAG нельзя использовать любую другую функцию отладки, требующую доступа к JTAG; например, логический анализатор Vivado ®.

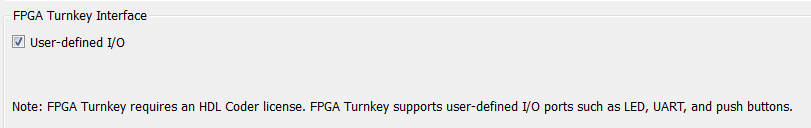

Интерфейс FPGA «под ключ»: если вы хотите использовать плату с рабочим процессом HDL Coder™ FPGA «под ключ», выберите Пользовательский ввод/вывод.

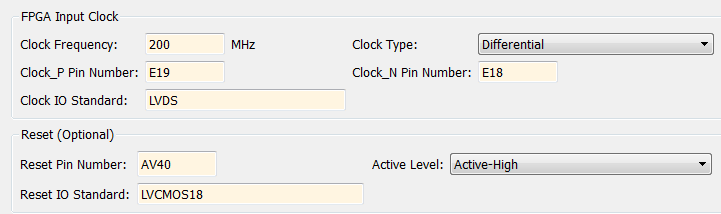

FPGA Input Clock - Подробные сведения о тактовых сигналах требуются для обоих рабочих процессов. Всю необходимую информацию можно найти в файле спецификации платы.

Тактовая частота - должна быть от 5 до 300. Для интерфейса Ethernet предлагаемые тактовые частоты составляют 50, 100, 125 и 200 МГц.

Тип синхросигнала - Single_Ended или Differential.

Номер контакта синхросигнала (Single_Ended) - необходимо указать. Пример: N10.

Clock_P Номер контакта (дифференциальный) - необходимо указать. Пример: E19.

Clock_N Номер контакта (дифференциальный) - необходимо указать. Пример: E18.

Clock IO Standard - программируемый стандарт ввода-вывода, используемый для конфигурирования портов ввода, вывода или двунаправленных портов. Например, LVDS.

Reset (дополнительно) - если требуется указать сброс, найдите номер контакта и активный уровень в файле спецификации платы и введите эту информацию.

Сбросить номер вывода (Reset Pin Number) - оставить пустым, если он отсутствует.

Активный уровень - Active-Low или Active-High.

Reset IO Standard - программируемый стандарт ввода-вывода, используемый для конфигурирования портов ввода, вывода или двунаправленных портов. Например, LVCMOS33.

При выборе соединения Ethernet с платой необходимо указать контакты для сигналов Ethernet на плате FPGA.

Список сигналов: Укажите все номера контактов FPGA для указанных сигналов. Эта информация содержится в файле спецификации платы. Для векторных сигналов перечислите все номера контактов в одной строке, разделенные запятыми.

Примечание

Если в микросхеме PHY отсутствует дополнительный контакт TX_ER, привяжите ETH_TXER к одному из неиспользуемых контактов на плате FPGA.

Создание модуля MDIO для переопределения настроек PHY: См. следующий раздел на FPGA Board Management Data Input/Output Bus (MDIO), чтобы определить, когда использовать эту функцию. Если эта опция выбрана, введите адрес PHY.

Примечание

Обеспечьте ввод-вывод FIL только для соединения Ethernet. Определите хотя бы один выходной порт для интерфейса ввода-вывода «под ключ».

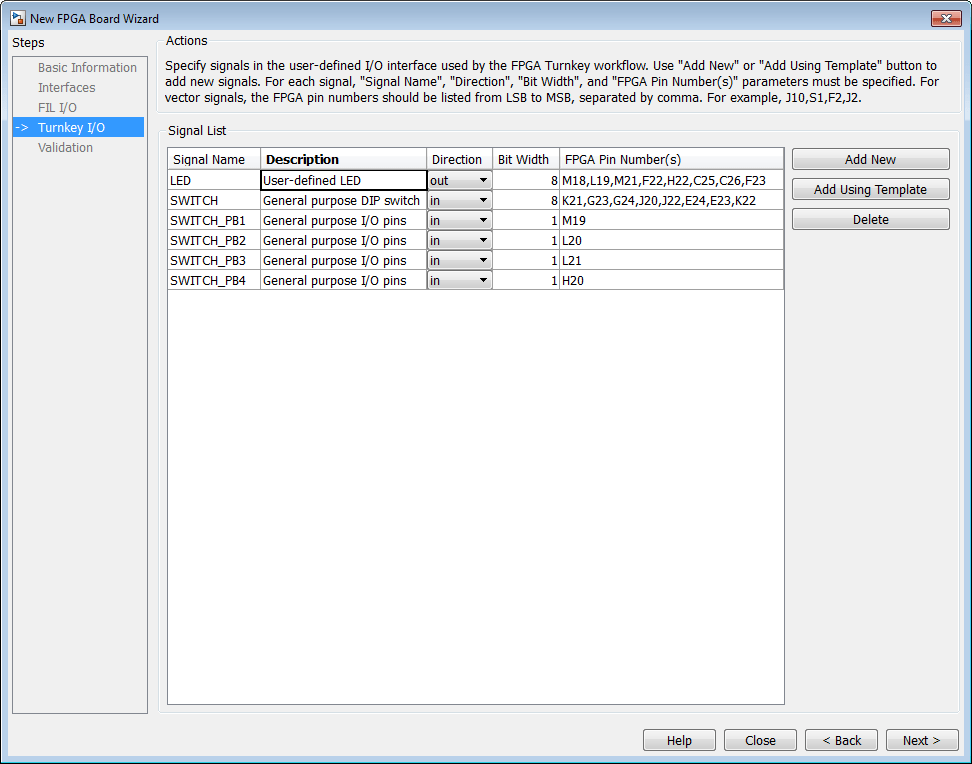

Список сигналов: Укажите все номера контактов FPGA для указанных сигналов. Эта информация содержится в файле спецификации платы. Для векторных сигналов перечислите все номера контактов в одной строке, разделенные запятыми. Количество номеров выводов должно соответствовать битовой ширине соответствующего сигнала.

Add New: Вам предлагается ввести все записи в список сигналов вручную.

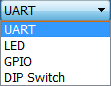

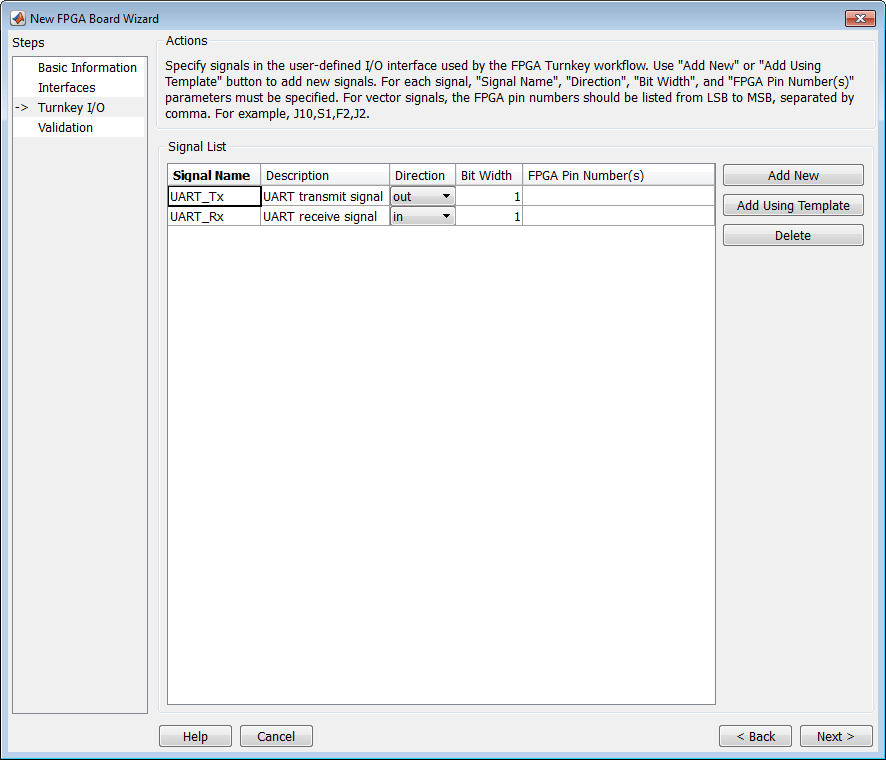

Добавить с помощью шаблона: Мастер предварительно заполняет новую запись сигнала для сигналов UART, LED, GPIO или DIP-переключателя следующим образом:

Общее имя сигнала

Описание

Направление

Битовая ширина

Можно изменить значения в любом из этих предварительно заполненных полей.

Удалить: Удалить выбранный сигнал из списка.

В следующем примере показано использование функции «Добавить с помощью шаблона».

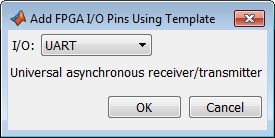

В диалоговом окне «Под ключ» нажмите кнопку «Добавить с помощью шаблона».

Теперь можно просмотреть диалоговое окно шаблона.

Откройте список ввода-вывода и выберите один из следующих вариантов:

Нажмите кнопку ОК.

Мастер добавляет указанный сигнал (или сигналы) в список ввода-вывода.

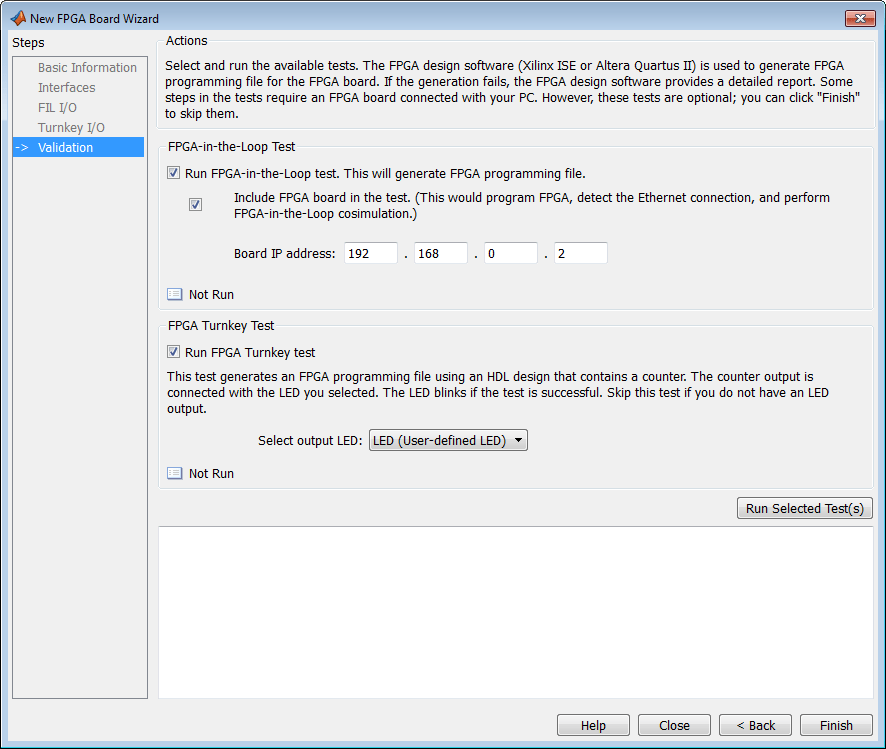

Тест FPGA в контуре

Запустите тест FPGA-in-the-Loop: Выберите, чтобы создать файл программирования FPGA.

Включить плату FPGA в тест: (Дополнительно) Эта программа выбора FPGA с сгенерированным файлом программирования обнаруживает соединение Ethernet (если выбрано) и выполняет моделирование FPGA-in-the-loop.

IP-адрес платы: (только подключение Ethernet) Эта опция используется для установки IP-адреса платы, если он не является IP-адресом по умолчанию (192.168.0.2).

При необходимости измените IP-адрес компьютера на другую подсеть с 192.168.0.x при настройке сетевого адаптера. Если IP-адрес платы по умолчанию 192.168.0.2 используется другим устройством, измените IP-адрес платы в соответствии со следующими рекомендациями:

Адрес подсети, обычно первые 3 байта IP-адреса платы, должен совпадать с IP-адресом хоста.

Последний байт IP-адреса платы должен отличаться от IP-адреса хоста.

IP-адрес платы не должен конфликтовать с IP-адресами других компьютеров.

Например, если IP-адрес хоста - 192.168.8.2, то можно использовать 192.168.8.3, если он доступен.

Испытание FPGA под ключ

Запустите тест FPGA «под ключ»: Выберите, чтобы создать файл программирования FPGA, используя конструкцию HDL, которая содержит счетчик. У вас должна быть прикреплена плата.

Выход счетчика соединен с выбранным индикатором. Пропустите этот тест, если у вас нет светодиодного выхода.

После завершения проверки нажмите кнопку Готово. См. раздел Сохранение файла определения платы.