.

Фактическая поддержка генерации кода зависит от реализации блока.

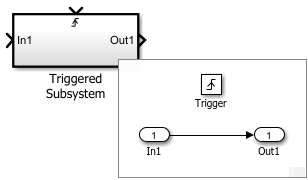

HDL Coder™ предоставляет дополнительные опции конфигурации, которые влияют на реализацию HDL и синтезированную логику. Для получения информации о передовом опыте, ограничениях и том, как можно использовать триггерный сигнал в качестве тактового сигнала с помощью TriggerAsClock см. раздел Использование инициированных подсистем для генерации кода HDL (кодер HDL).

Архитектура HDL| Архитектура | Описание |

|---|

Module (по умолчанию) | Создайте код для подсистемы и блоков в подсистеме. |

BlackBox | Создайте интерфейс черного ящика. Сгенерированный код HDL включает только определения портов ввода/вывода для подсистемы. Поэтому можно использовать подсистему в модели для создания интерфейса с существующим, написанным вручную кодом HDL. Генерация интерфейса черного ящика для подсистем аналогична генерации интерфейса блока модели без тактовых сигналов. |

No HDL

| Удалите подсистему из сгенерированного кода. При моделировании можно использовать подсистему, однако в коде HDL ее можно рассматривать как «no-op». |

Свойства блока HDL| Общая информация |

|---|

| AdaptivePipelining | Автоматическая вставка трубопровода на основе инструмента синтеза, целевой частоты и длины слова множителя. Значение по умолчанию: inherit. См. также раздел Pipelining (кодер HDL).

|

| BalanceDelays | Обнаруживает введение новых задержек по одному пути и вставляет совпадающие задержки по другим путям. Значение по умолчанию: inherit. См. Также «Задержки» (кодер HDL).

|

| ClockRatePipelining | Вставка регистров конвейера с более высокой тактовой частотой вместо более низкой скорости передачи данных. Значение по умолчанию: inherit. См. также ClockRatePipelining (кодер HDL).

|

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках проекта. Распределенная конвейерная обработка не перераспределяет эти регистры. Значение по умолчанию: 0. Дополнительные сведения см. в разделе ConstrainedOutputPipeline (кодер HDL).

|

| DistributedPipelining | Распределение регистров трубопроводов или ресинхронизация регистров. Значение по умолчанию: off. См. также раздел Pipelining (кодер HDL).

|

| DSPStyle | Атрибуты синтеза для отображения множителя. Значение по умолчанию: none. См. также DSPStyle (кодер HDL).

|

| FlattenHierarchy | Удалите иерархию подсистемы из сгенерированного кода HDL. Значение по умолчанию: inherit. См. также FlattenHierarchy (кодер HDL).

|

| InputPipeline | Количество входных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: 0. Дополнительные сведения см. в разделе InputPipeline (кодер HDL).

|

| OutputPipeline | Количество выходных ступеней трубопровода для вставки в сформированный код. Распределенная конвейерная обработка и конвейерная обработка с ограниченным выходом могут перемещать эти регистры. Значение по умолчанию: 0. Дополнительные сведения см. в разделе Выходной конвейер (кодер HDL).

|

| SharingFactor | Количество функционально эквивалентных ресурсов для сопоставления с одним общим ресурсом. Значение по умолчанию - 0. См. также раздел Совместное использование ресурсов (кодер HDL).

|

| StreamingFactor | Количество параллельных путей данных, или векторов, которые мультиплексируются по времени для преобразования в последовательные скалярные пути данных. По умолчанию используется значение 0, которое реализует полностью параллельные пути данных. См. также Потоковая передача (кодер HDL).

|

Целевая спецификация

Этот блок не может быть DUT, поэтому параметры свойств блока на вкладке «Целевая спецификация» игнорируются.

Фактическая поддержка типа данных зависит от реализации блока.