Simulink ® Design Verifier™ позволяет анализировать модели Simulink следующим образом:

Обнаружение ошибок конструкции, которые могут возникнуть во время выполнения.

Создание тестовых примеров, обеспечивающих охват модели.

Доказывать свойства и выявлять нарушения свойств.

Прежде чем Simulink Design Verifier проанализирует модель, программа проверяет, совместима ли модель с анализом. Модель совместима для анализа в следующих случаях:

Модель компилируется в исполняемую форму.

Модель совместима с генерацией кода.

Модель выполняет нулевое моделирование без ошибок, то есть время начала и окончания моделирования равно 0.

Программное обеспечение поддерживает широкий спектр программных возможностей Simulink и Stateflow ® в ваших моделях. Однако существуют возможности, которые не поддерживаются продуктом, описанные в разделе Ограничения поддержки функций программного обеспечения Simulink и ограничения поддержки функций программного обеспечения Stateflow.

Дополнительные сведения о поддерживаемых блоках Simulink см. в разделе Поддерживаемые и неподдерживаемые блоки Simulink в программе Simulink Design Verifier.

Перед началом анализа программа проверяет совместимость модели, а затем создает представление модели. Представление модели включает артефакты модели, которые используются во время анализа. Дополнительные сведения см. в разделе Представление модели для анализа.

Перед началом анализа можно выполнить проверку совместимости модели одним из этих методов. При использовании любого из этих методов представление модели всегда перестраивается.

На вкладке «Проверка проекта» в разделе «Анализ» выберите «Проверка совместимости».

В приложении Model Advisor выберите либо По продукту > Simulink Design Verifier > Проверить совместимость с Simulink Design Verifier, либо По задаче > Simulink Design Verifier Compatibility Check > Проверить совместимость с Simulink Design Verifier. Щелкните Выполнить эту проверку.

Дополнительные сведения см. в разделе Проверки Simulink Design Verifier.

Чтобы запустить проверку совместимости программно в командной строке или в программе MATLAB ®, используйте sldvcompat функция. Дополнительные сведения см. в разделе sldvcompat.

Чтобы проверить совместимость подсистемы, щелкните правой кнопкой мыши подсистему и выберите Design Verifier > Check Subsystem Compatibility.

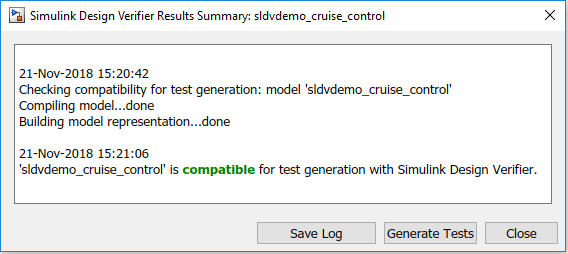

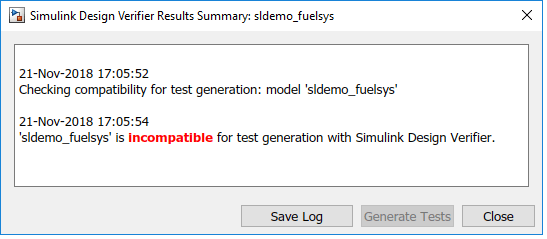

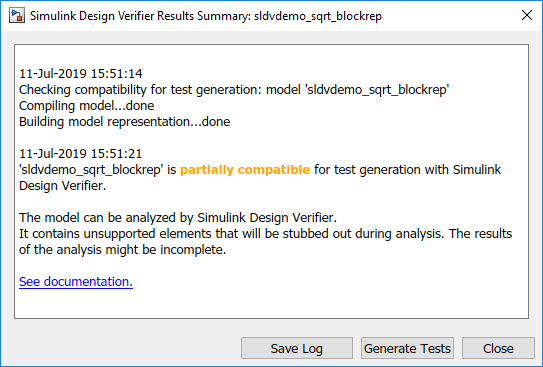

При выполнении проверки совместимости модели в окне Сводка результатов (Results Summary) отображается один из следующих результатов.

Если модель совместима, можно продолжить анализ в окне Сводка результатов (Results Summary). Например, чтобы продолжить анализ генерации теста, щелкните Генерировать тесты (Generate Tests).

Примечание

После завершения проверки совместимости при изменении модели продолжение анализа в окне Сводка результатов (Results Summary) невозможно. При изменении модели повторно запустите проверку совместимости для анализа.

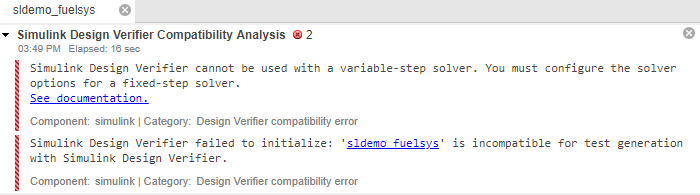

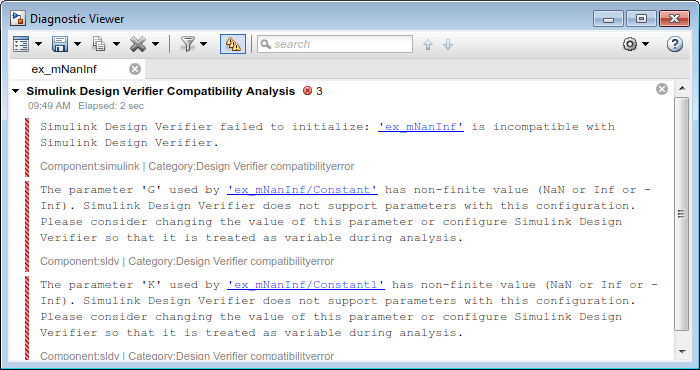

Если модель несовместима с Simulink Design Verifier, можно определить и исправить несовместимость с помощью сообщений программы Diagnostic Viewer. Дополнительные сведения см. в разделе Просмотр диагностики.

Если в модели используется решатель с переменным шагом, настройте тип решателя как Fixed-step.

Если в модели имеются неокончательные данные, измените значение данных или настройте модель таким образом, чтобы данные обрабатывались как переменные во время анализа Simulink Design Verifier. Дополнительные сведения см. в разделе Неготовые данные.

Если модель большая и содержит много подсистем, можно с помощью Test Generation Advisor определить, вызывают ли некоторые подсистемы несовместимость. Дополнительные сведения см. в разделе Использование помощника по созданию тестов для определения анализируемых компонентов.

Модель частично совместима, если по крайней мере один объект модели несовместим. Simulink Design Verifier продолжает анализ частично совместимой модели, блокируя неподдерживаемые элементы. По умолчанию для параметра «Автоматическое блокирование неподдерживаемых блоков и функций» установлено значение On. Дополнительные сведения см. в разделе Обработка несовместимости с автоматической остановкой.

Базовый рабочий процесс для Simulink Design Verifier | Замена блоков для неподдерживаемых блоков | Представление модели для анализа