Сделать имена выходных файлов уникальными путем добавления суффикса

Автоматическое блокирование неподдерживаемых блоков и функций

Использовать указанные входные минимальные и максимальные значения

Выполнение дополнительного анализа для уменьшения числа случаев рациональной аппроксимации

Проверка тестовых примеров или контрпримеров с параллельными вычислениями

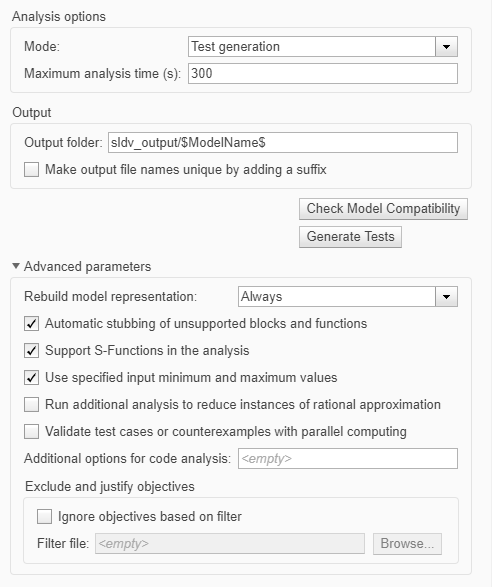

Укажите параметры анализа и настройте выходные данные Simulink ® Design Verifier™.

Укажите режим анализа для Simulink Design Verifier.

По умолчанию:

Test generation

Design error detectionОбнаружение ошибок переполнения целочисленных и фиксированных точек и ошибок деления на ноль в модели

Test generationСоздание тестовых примеров для модели.

Property provingПроверка свойств модели.

Simulink Design Verifier задает значение этой опции при выборе одной из следующих опций анализа на вкладке Design Verifier в разделе Режим (Mode).

Выберите «Обнаружение ошибок конструкции», затем щелкните «Обнаружение ошибок конструкции».

Выберите Генерация тестов и нажмите Генерация тестов.

Выберите Проверка свойств, затем нажмите Доказать свойства.

При установке параметра Режим (Mode) кнопка ниже Проверить совместимость модели (Check Model Compatibility) изменяется следующим образом:

Режим: Test generation, кнопка читается: Создать тесты

Режим: Design error detection, кнопка читает: Обнаружение ошибок

Режим: Property proving, кнопка читает: Докажи свойства

Параметр:

DVMode |

| Тип: символьный массив |

Значение:

'TestGeneration' | 'DesignErrorDetection' | 'PropertyProving' |

По умолчанию:

'TestGeneration' |

Укажите максимальное время (в секундах), которое Simulink Design Verifier тратит на анализ модели. Значение максимального времени анализа можно задать равным значению, которое необходимо предоставить анализу. Анализ также можно остановить в любое время.

По умолчанию:

300

Введенное значение представляет максимальное количество секунд, в течение которых Simulink Design Verifier анализирует модель.

Параметр:

DVMaxProcessTime |

Тип:

double |

| Значение: любое допустимое значение |

По умолчанию:

300 |

Укажите путь, в который Simulink Design Verifier записывает выходные данные.

По умолчанию:

sldv_output/$ModelName$

Введите абсолютный или относительный путь к текущей папке.

$ModelName$ - маркер, представляющий имя модели.

Для настройки имен и расположений выходных данных Simulink Design Verifier можно использовать следующие параметры:

На панели «Результаты»:

Имя файла данных

Имя файла модели прокладки кабелей

Параметры теста Simulink > Имя файла теста

На панели «Отчет»:

Имя файла отчета

Путь к файлу выходной модели

На панели «Замены блоков»:

Путь к файлу выходной модели

Параметр:

DVOutputDir |

| Тип: символьный массив |

| Значение: любой допустимый путь |

По умолчанию:

'sldv_output/$ModelName$' |

Укажите, делает ли Simulink Design Verifier имена выходных файлов уникальными, добавляя числовой суффикс.

По умолчанию: Вкл.

Добавляет добавочный числовой суффикс к именам выходных файлов Simulink Design Verifier. При выборе этого параметра программа не сможет перезаписать существующие файлы с тем же именем.

Не добавляет суффикс к именам выходных файлов Simulink Design Verifier. В этом случае программа может перезаписать существующие файлы с тем же именем.

Параметр:

DVMakeOutputFilesUnique |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'on' |

Выполните проверку совместимости модели с Simulink Design Verifier. Дополнительные сведения см. в разделе Проверки Simulink Design Verifier.

При установке параметра Mode эта кнопка изменяется следующим образом:

Режим: Test generation, кнопка читается: Создать тесты

Дополнительные сведения см. в разделе Создание тестового примера.

Режим: Design error detection, кнопка читает: Обнаружение ошибок

Дополнительные сведения см. в разделе Что такое обнаружение ошибок конструкции?.

Режим: Property proving, кнопка читает: Докажи свойства

Дополнительные сведения см. в разделе Что такое проверка свойств?.

Укажите, требуется ли перестроить представление модели для анализа Simulink Design Verifier.

По умолчанию:

If change is detected

AlwaysВсегда перестраивайте представление модели.

If change is detectedПерестроить представление модели можно только тогда, когда программа обнаружит изменения в модели.

Параметр:

DVRebuildModelRepresentation |

Тип:

character array |

Значение:

'Always' | 'IfChangeIsDetected' |

По умолчанию:

'If change is detected' |

Укажите, следует ли игнорировать неподдерживаемые блоки и функции во время анализа.

По умолчанию: Вкл.

Игнорирует неподдерживаемые блоки и функции и продолжает анализ.

Отображает предупреждение, когда Simulink Design Verifier обнаруживает неподдерживаемый блок или функцию, и запрашивает, хотите ли вы продолжить анализ.

Параметр:

DVAutomaticStubbing |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'on' |

Укажите, следует ли включить поддержку S-функций, скомпилированных для совместимости с Simulink Design Verifier.

По умолчанию: Вкл.

Включает поддержку S-функций, скомпилированных для совместимости с Simulink Design Verifier.

Simulink Design Verifier автоматически блокирует S-функции во время анализа.

Параметр:

DVSFcnSupport |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'on' |

Ограничения и соображения по поддержке S-функций и кода C/C + +

Укажите, следует ли создавать тестовые примеры, в которых указанные минимальное и максимальное значения рассматриваются в качестве ограничений для всех входных сигналов в модели.

По умолчанию: Вкл.

Рассматривает указанные минимальное и максимальное значения в качестве ограничений для всех входных сигналов.

Игнорирует любые указанные минимальные и максимальные значения.

Параметр:

DVDesignMinMaxConstraints |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'on' |

Укажите, пытается ли Simulink Design Verifier уменьшить использование рациональной аппроксимации во время анализа.

По умолчанию: Вкл.

При использовании Simulink Design Verifier для анализа моделей Simulink Design Verifier пытается уменьшить использование рациональной аппроксимации в случае модели. Включение этого параметра может увеличить время анализа.

Simulink Design Verifier не пытается уменьшить использование рациональной аппроксимации при анализе.

Параметр:

DVReduceRationalApprox |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'on' |

Указывает, следует ли проверять тестовые примеры или контрпримеры с параллельными вычислениями. Для этого параметра требуется лицензия Parallel Computing Toolbox™.

Как правило, параллельное выполнение может помочь сократить время проверки, если:

Имеется сложная модель Simulink, для моделирования которой требуется много времени.

Анализ Simulink Design Verifier превышает максимальное время анализа и приводит к ряду задач со статусом «Моделирование потребностей». Дополнительные сведения см. в разделе Удовлетворенные цели - Имитация потребностей и сфальсифицированные цели - Имитация потребностей.

В результате анализа генерации теста генерируются длинные тестовые примеры. Возможно, для оптимизации набора тестов задано значение LongTestcases или максимальное значение шагов теста больше значения по умолчанию. Дополнительные сведения см. в разделе Обзор области создания тестов.

При использовании параллельных вычислений для проверки необходимо учитывать следующие моменты:

Запуск параллельного пула может занять время, что влияет на общее время анализа. Чтобы сократить время анализа, выполните следующие действия.

Перед выполнением анализа генерации теста убедитесь, что параллельный пул уже запущен. По умолчанию параллельный пул отключается после простоя в течение указанного количества минут. Сведения об изменении параметров см. в разделе «Определение параметров параллельного вычисления» на панели инструментов параллельного вычисления.

Загрузите Simulink на всех параллельных работников пула.

Моделирование происходит последовательно, когда:

Кластер не является local. Настройка параметров параллельной настройки для использования local только кластер. Сведения об изменении параметров см. в разделе «Определение параметров параллельного вычисления» на панели инструментов параллельного вычисления.

Модель находится в dirty state перед запуском анализа SLDV.

Модель имеет ToFile блоки.

Модель представляет собой внутренний электрический жгут.

Функции различных продуктов, такие как функциональное тестирование и анализ покрытия от Simulink Test™ Manager, не поддерживают параллельные вычисления для проверки. Дополнительные сведения см. в разделе Выполнение функционального тестирования и анализ покрытия теста (Simulink Test).

По умолчанию: Откл.

Если у вас есть лицензия Parallel Computing Toolbox, то Simulink Design Verifier проверяет тестовые примеры или контрпримеры параллельно для нескольких работников на одной машине.

Simulink Design Verifier проверяет тестовые примеры или контрпримеры в серийном формате.

Параметр:

DVUseParallel |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'off' |

Укажите дополнительные параметры анализа S-функций, которые были скомпилированы для совместимости с Simulink Design Verifier. Дополнительные сведения см. в разделе Ограничения и рекомендации по поддержке S-функций и кода C/C + +.

По умолчанию:

''

Введите дополнительные параметры для анализа S-функций, которые были скомпилированы для совместимости с Simulink Design Verifier. Например, чтобы задать максимальный размер массивов, введите defaultArraySize = 512.

Параметр:

DVCodeAnalysisExtraOptions |

| Тип: символьный массив |

| Значение: любой допустимый параметр для анализа S-функций |

По умолчанию:

'' |

Укажите, чтобы проанализировать модель, игнорируя цели в файле фильтра. Файл фильтра содержит цели покрытия модели для генерации теста и цели обнаружения ошибок конструкции, которые необходимо отфильтровать из анализа.

По умолчанию: Откл.

Игнорирует цели в файле фильтра во время генерации теста и анализа обнаружения ошибок конструкции.

Создает результаты для всех целей для генерации тестов и анализа обнаружения ошибок конструкции, включая результаты из файла фильтра.

Этот параметр включает файл фильтра.

Параметр:

DVCovFilter |

| Тип: символьный массив |

Значение:

'on' | 'off' |

По умолчанию:

'off' |

Фильтрация покрытия (покрытие Simulink)

Укажите папку и имя файла, содержащего цели покрытия модели для создания теста и цели обнаружения ошибок конструкции, которые необходимо отфильтровать из анализа.

По умолчанию:

''

Укажите имя папки и имя файла, содержащие цели, которые необходимо игнорировать при создании теста и анализе обнаружения ошибок конструкции.

Нажмите кнопку «Обзор», чтобы выбрать существующий файл фильтра.

Параметр:

DVCovFilterFileName |

| Тип: символьный массив |

| Значение: любой допустимый путь и имя файла |

По умолчанию:

'' |

Правила и файлы фильтра покрытия (покрытие Simulink)

Фильтрация целей с помощью средства просмотра фильтров анализа

Перейдите к файлу, содержащему цели, которые необходимо игнорировать при обнаружении ошибок конструкции и анализе генерации тестов.

Эта кнопка активируется функцией Игнорировать цели на основе фильтра.