С помощью SoC Blockset™ можно моделировать упрощенный потоковый протокол в модели. Используйте Coder™ HDL для создания AXI4-Stream интерфейсов в ядре IP.

При необходимости создания интерфейса AXI4-Stream в ядре IP в интерфейсе DUT реализуются следующие сигналы:

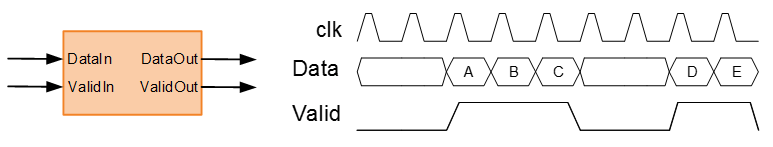

Данные

Действительный

При сопоставлении скалярных портов DUT с интерфейсом AXI4-Stream можно дополнительно моделировать следующие сигналы и сопоставлять их с интерфейсом AXI4-Stream:

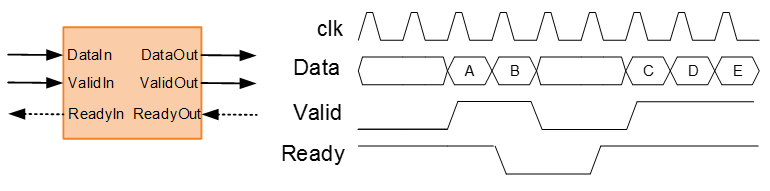

Готов

Другие протокольные сигналы, такие как:

TSTRB

TKEEP

TLAST

TID

TDEST

TUSER

Когда сигнал Data является действительным, подается сигнал Valid.

Интерфейсы AXI4-Stream в DUT могут дополнительно включать сигнал Ready. В подчиненном интерфейсе сигнал Ready позволяет применять противодавление. В главном интерфейсе сигнал Ready позволяет реагировать на обратное давление.

При моделировании сигнала Ready в AXI4-Stream интерфейсах главный интерфейс игнорирует сигналы Data и Valid через один такт после отключения сигнала Ready. После подачи сигнала готовности можно начать отправку сигналов Data и Valid. Можно послать еще один сигнал Data и Valid после отключения сигнала Ready.

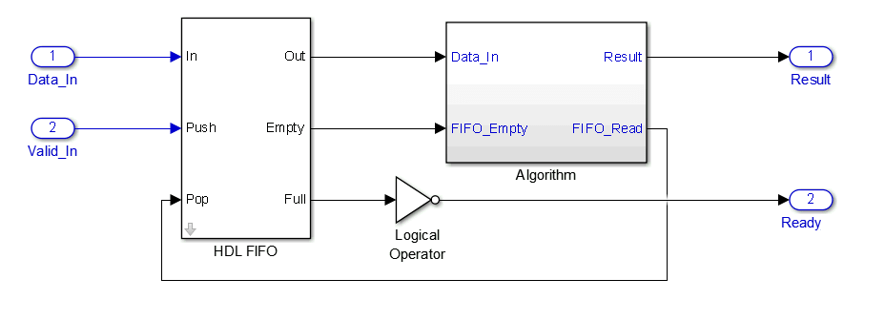

Если не моделировать сигнал готовности, кодер HDL генерирует сигнал и соответствующую логику обратного давления.

Например, если в DUT имеется FIFO для хранения кадра данных, для приложения противодавления к восходящему компоненту можно смоделировать сигнал Ready на основе сигнала FIFO Full.

Канал памяти | Создатель шины SoC