Использование SoC Blockset™ позволяет реализовать в модели упрощенный потоковый пиксельный протокол. Используйте Coder™ HDL для создания IP-ядра HDL с интерфейсами AXI4-Stream Video.

Вы можете использовать текущий пиксельный протокол для отображения интерфейса AXI4-Stream Video. Алгоритмы видео обрабатывают данные последовательно и генерируют видеоданные как последовательный поток пиксельных данных и управляющих сигналов.

Чтобы создать ядро IP с интерфейсами AXI4-Stream Video, в интерфейсе DUT реализуйте следующие сигналы:

Пиксельные данные

Шина управления пикселами

Шина пиксельного управления - это шина, которая имеет следующие сигналы:

hStart

hEnd

vStart

vEnd

valid

Сигналы hStart и hEnd представляют начало активной линии и конец активной линии соответственно. Сигналы vStart и vEnd представляют начало и конец кадра.

При необходимости можно смоделировать сигнал противодавления (Ready) и сопоставить его с интерфейсом AXI4-Stream Video.

Этот рисунок представляет собой изображение размером 2 на 3 пиксела. Активной областью изображения является прямоугольник с пунктирной линией вокруг него и неактивные пикселы, которые его окружают. Пикселы помечаются значениями в градациях серого.

![]()

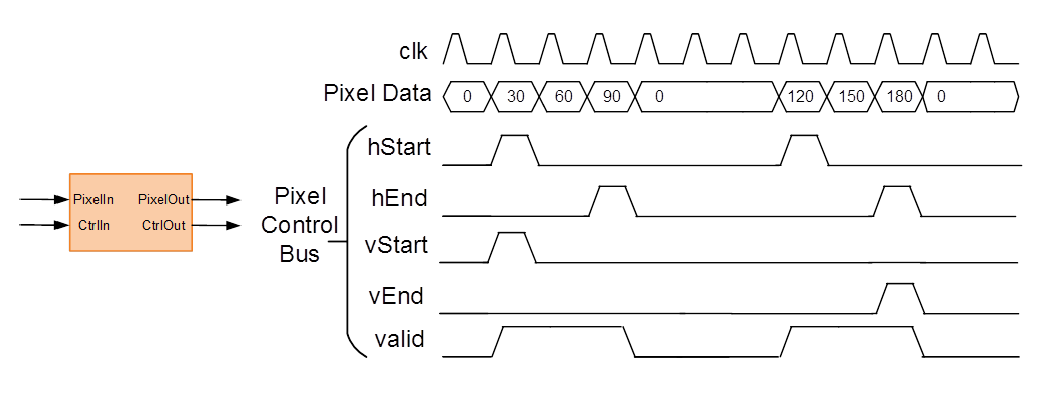

На этом рисунке показана временная диаграмма для сигналов Pixel Data и Pixel Control Bus, моделируемых в интерфейсе DUT.

Сигнал пиксельных данных является первичным видеосигналом, который передается через интерфейс AXI4-Stream Video. Когда сигнал Pixel Data является действительным, утверждается действительный сигнал.

Сигнал hStart становится высоким в начале активных линий. Сигнал hEnd становится высоким в конце активных линий.

Сигнал vStart становится высоким в начале активного кадра во второй строке. Сигнал vEnd становится высоким в конце активного кадра в третьей строке.

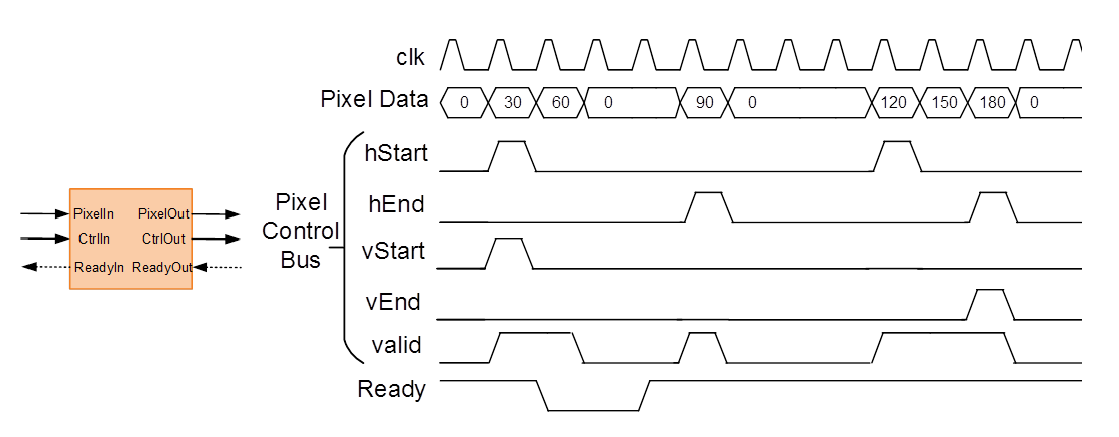

На этом рисунке показана временная диаграмма для пиксельных данных, шины управления пикселями и сигнала готовности, моделируемого в интерфейсе DUT.

При сопоставлении портов DUT с интерфейсом AXI4-Stream Video можно дополнительно смоделировать сигнал противодавления Ready и сопоставить его с интерфейсом AXI4-Stream Video.

В подчиненном интерфейсе с сигналом Ready можно применить противодавление. В главном интерфейсе с сигналом Ready можно реагировать на обратное давление.

При моделировании сигнала Ready в AXI4-Stream видеоинтерфейсах главный интерфейс должен сбросить свой действительный сигнал через один цикл после того, как сигнал Ready будет сброшен.

Если не моделировать сигнал готовности, кодер HDL генерирует соответствующую логику противодавления.

Канал памяти | Создатель шины SoC