Для проектов, требующих доступа к большим наборам данных из внешней памяти, смоделировать алгоритм с помощью упрощенного протокола AXI4 Master. При запуске IP Core Generation workflow, HDL Coder™ генерирует ядро IP с интерфейсами AXI4 Master. Интерфейс AXI4 Master может взаимодействовать между конструкцией и внешним контроллером памяти IP с помощью протокола AXI4 Master.

Упрощенный протокол AXI4 Master можно использовать для сопоставления с интерфейсами AXI4 Master. Используйте упрощенный протокол записи AXI4 Master для транзакции записи и упрощенный протокол чтения AXI4 Master для транзакции чтения.

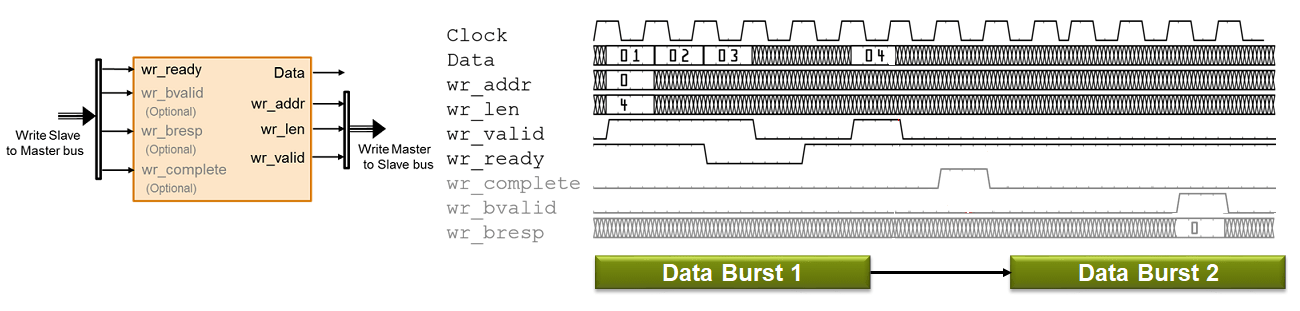

На этом рисунке показана временная диаграмма сигналов, моделируемых в интерфейсах ввода и вывода DUT для транзакции записи AXI4 Master.

DUT ожидает wr_ready стать высоким, чтобы инициировать запрос на запись. Когда wr_ready становится высоким, DUT может послать запрос на запись. Запрос на запись состоит из Data и Write Master to Slave bus сигналы. Эта шина состоит из wr_len, wr_addr, и wr_valid. wr_addr указывает начальный адрес, на который DUT хочет выполнить запись. wr_len сигнал соответствует количеству элементов данных в этой транзакции записи. Data может быть отправлен до тех пор, пока wr_valid высоко. Когда wr_ready становится низким, DUT должен прекратить отправку данных в течение одного тактового цикла, и Data сигнал становится недействительным. Если DUT продолжает посылать данные после одного такта, данные игнорируются.

Упрощенный главный протокол AXI4 поддерживает конвейерные запросы, поэтому не требуется ждать wr_complete сигнал должен быть высоким перед выдачей последующего запроса на запись. Интерфейс поддерживает до 16 транзакций (или 16 слов данных) перед остановкой конвейера и wr_ready сигнал падает.

Выходные сигналы

Смоделировать Data и Write Master to Slave bus сигналы на выходном интерфейсе DUT.

DataДанные, которые требуется перенести, действительны в каждом цикле транзакции.

Write Master to Slave bus который состоит из:

wr_addr: Начальный адрес транзакции записи, который отбирается в первом цикле транзакции. Адрес указан в байтах.

wr_len: Количество значений данных, которые требуется перенести, выбранных в первом цикле транзакции. wr_len сигнал указывается словами.

wr_validКогда этот управляющий сигнал становится высоким, он указывает, что Data сигнал, дискретизированный на выходе, является действительным.

Входные сигналы

Смоделировать Write Slave to Master bus который состоит из:

wr_ready: Этот сигнал соответствует противодавлению от ведомого IP-ядра или внешней памяти. Когда этот управляющий сигнал становится высоким, это означает, что данные могут быть измерены. когда wr_ready низкий, DUT должен прекратить передачу данных в течение одного тактового цикла. Вы также можете использовать wr_ready чтобы определить, может ли DUT послать второй пакетный сигнал сразу после того, как первый пакетный сигнал был определен. wr_ready сигнал остается высоким, чтобы принять второй пакет сразу после того, как принят последний элемент первого пакета.

wr_bvalid (дополнительный сигнал): Ответный сигнал от ведомого IP-ядра, который можно использовать для диагностики. wr_bvalid сигнал становится высоким после того, как AXI4 межсоединение принимает каждую пакетную транзакцию. Если wr_len больше, чем 256модуль записи AXI4 Master разбивает большой пакетный сигнал на 256 пакетов. wr_bvalid становится высоким для каждого пакета 256-го размера.

wr_bresp (дополнительный сигнал): Ответный сигнал от ведомого IP-ядра, который можно использовать для диагностики. Используйте этот сигнал с wr_bvalid сигнал.

wr_complete (необязательный сигнал): Управляющий сигнал, который остается высоким в течение одного такта, указывает, что транзакция записи завершена. Этот сигнал утверждается последним wr_bvalid всплеска.

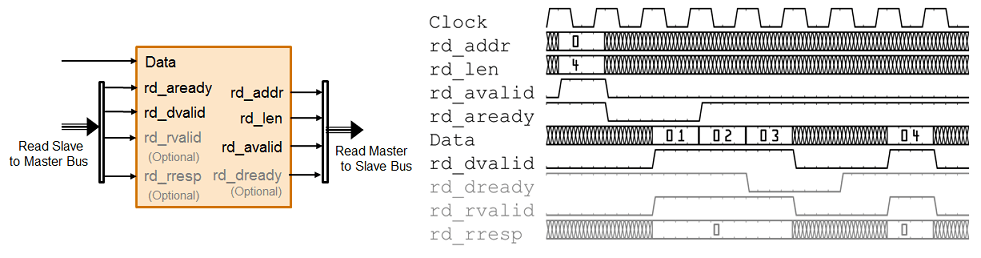

На этом рисунке показана временная диаграмма для сигналов, моделируемых в интерфейсах ввода и вывода DUT для транзакции чтения AXI4 Master. Эти сигналы включают в себя Data, Read Master to Slave Bus, и Read Slave to Master Bus.

DUT ожидает rd_aready становится высоким, чтобы инициировать запрос на чтение. Когда rd_aready высокий, DUT может отправить запрос на чтение. Запрос на чтение состоит из rd_addr, rd_len, и rd_avalid сигналы Read Master to Slave bus. Подчиненный IP или внешняя память отвечает на запрос на чтение, посылая Data на каждом такте. rd_len сигнал соответствует количеству считываемых значений данных. DUT может принимать Data до тех пор, пока rd_dvalid высоко.

Запрос на чтение

Чтобы смоделировать запрос на чтение, в интерфейсе вывода DUT смоделируйте Read Master to Slave bus который состоит из:

rd_addrНачальный адрес для прочитанной транзакции, который был выбран в первом цикле транзакции. Адрес указан в байтах.

rd_len: Количество значений данных, которые вы хотите прочитать, отобранных в первом цикле транзакции. rd_len сигнал указывается словами.

rd_avalid: Управляющий сигнал, указывающий, является ли запрос на чтение действительным.

На входном интерфейсе DUT выполните команду rd_aready сигнал. Этот сигнал является частью Read Slave to Master bus и указывает, когда принимать запросы на чтение. Вы можете контролировать rd_aready сигнал для определения, может ли DUT посылать последовательные пакетные запросы. Когда rd_aready становится высоким, это указывает на то, что DUT может послать запрос на чтение в следующем такте.

Упрощенный AXI4 Master Protocol поддерживает конвейерные запросы, поэтому не требуется ждать завершения ответа на считывание перед выдачей последующего запроса на считывание. Интерфейс поддерживает до 4 транзакций чтения перед остановкой конвейера и rd_aready сигнал падает.

Ответ на чтение

На входном интерфейсе DUT смоделируйте Data и Read Slave to Master bus сигналы.

Data: Данные, возвращенные из запроса на чтение.

Read Slave to Master bus который состоит из:

rd_dvalidУправляющий сигнал, указывающий, что Data возвращено из запроса на чтение.

rd_rvalid (дополнительный сигнал): ответный сигнал от ведомого IP-ядра, который можно использовать для диагностики.

rd_rresp (необязательный сигнал): Ответный сигнал от ведомого IP-ядра, который указывает состояние транзакции считывания.

На выходном интерфейсе DUT можно дополнительно реализовать rd_dready сигнал. Этот сигнал является частью Read Master to Slave bus и указывает, когда DUT может начать прием данных. По умолчанию, если этот сигнал не сопоставлен с интерфейсом чтения AXI4 Master, сгенерированные IP-соединения HDL rd_dready на высокий логический уровень.

Канал памяти | Создатель шины SoC