SoC Blockset™ позволяет моделировать и оценивать транзакции памяти в Simulink ® без необходимости развертывания модели на устройстве SoC. Эта диагностическая информация используется для анализа производительности моделей и корректировки в соответствии с требуемыми требованиями к производительности системы. Моделирование создает два типа визуализации трафика памяти :

Графики производительности моделирования - обеспечивает высокоуровневую диагностику производительности системы памяти модели. Пропускная способность памяти, количество пакетов и задержки транзакций вычисляются на основе моделирования модели. Можно просмотреть эту информацию для каждого хозяина памяти в модели или общий вид с контроллера памяти.

Буферные и пакетные формы сигналов - предоставляет информацию отладки пакетных транзакций из моделирования, включая использование буферных областей.

Можно также зафиксировать фактическую пропускную способность, количество пакетов и измерения задержки при проектировании, выполняемом на FPGA, а также просмотреть информацию об отдельных транзакциях пакетов. Эта информация фиксируется путем включения IP-адреса монитора межсоединений AXI в конструкцию FPGA и запроса данных через главное соединение JTAG AXI от хоста. См. раздел Информация о производительности памяти при выполнении FPGA.

SoC Blockset позволяет регистрировать сигналы моделирования и визуализировать регистрируемые сигналы с помощью Logic Analyzer. Для включения регистрации сигналов установите уровень диагностики памяти в значение Basic diagnostic signals в конфигурационных параметрах модели по пути Hardware Implementation > Target hardware resources > FPGA design (debug).

После моделирования модели найдите Logic Analyzer в верхней части окна Simulink.

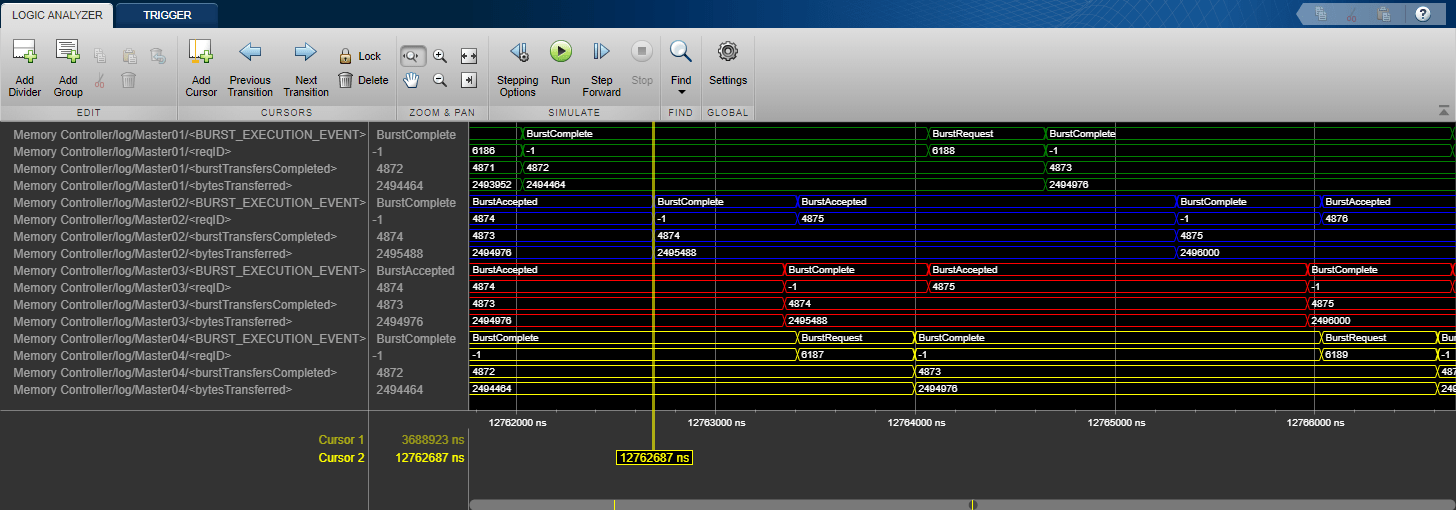

Инструмент Logic Analyzer обеспечивает визуализацию форм сигналов для отображения синхронизации различных событий модели памяти.

Логический анализатор отображает сигналы от контроллера памяти и от блоков канала памяти.

Формы пакетных сигналов

Формы сигналов от контроллера памяти включают в себя информацию для пакетов от ведущих в системе. Формы сигналов кодируются цветом для дифференциации различных основных сигналов. Эти формы сигнала дают представление о последовательности каждого из ведущих сигналов через общую память. Для каждого ведущего устройства просмотрите следующие сигналы:

BURST_EXECUTION_EVENT: Состояние текущего запроса пакета. Допустимыми состояниями являются: none (idle), request, executing, done. Дополнительные сведения о состоянии контроллера памяти см. в разделе Контроллер памяти.

ReqID: Идентификатор текущего запроса пакета. Инкрементное число, уникальное в процессе моделирования.

burstTransfersCompleted: Текущее количество переданных пакетов. Если в канале памяти не отбрасываются пакеты, счетчик переданных пакетов совпадает ReqID. Если пачки сброшены, ReqID становится больше этого числа.

BytesTransferred: Текущее число переданных байтов.

На следующем рисунке показаны сигналы после моделирования анализа пропускной способности памяти с использованием генераторов трафика.

Формы сигнала включают в себя информацию о пачке для четырех основных сигналов, отображаемых различными цветами. Эта информация коррелирует с графиками задержки контроллера памяти.

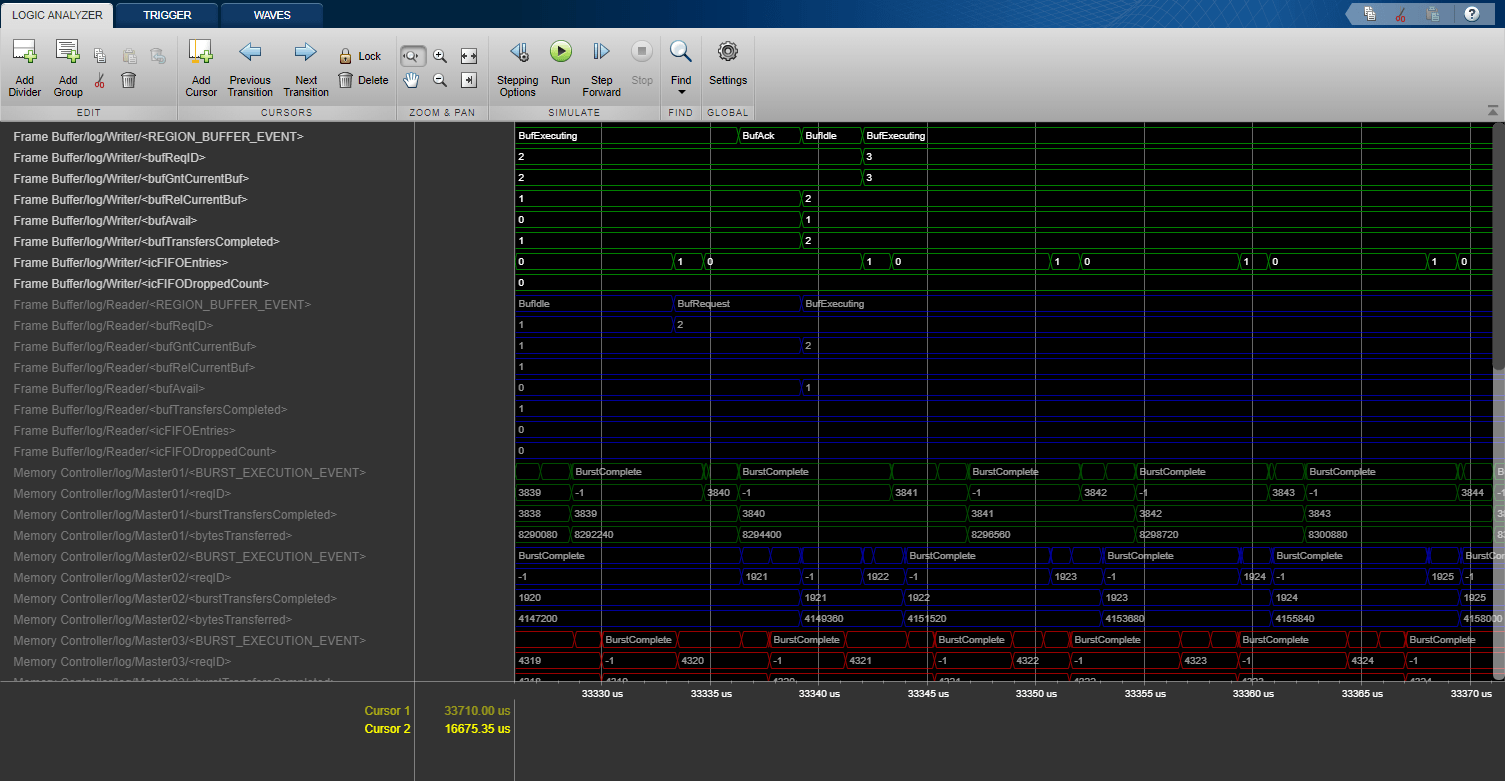

Буферные формы сигналов

Формы сигналов из канала памяти включают в себя информацию для транзакций считывания и записи буфера в канале. Каждая область памяти разделена на несколько буферов, заданных параметром Number of buffers блока Memory Channel. Устройство записи заполняет буферы, а устройство чтения очищает их. Эти формы сигнала дают представление о последовательности записи и считывания для данной области. Буферные сигналы включают в себя следующие сигналы:

REGION_BUFFER_EVENT: Состояние текущего запроса буфера. Допустимыми состояниями являются: none (idle), request, executing, done. Дополнительные сведения о состоянии канала памяти см. в разделе Канал памяти.

BufReqID: Идентификатор текущего запроса буфера. Инкрементное число, уникальное в процессе моделирования.

BufferAddress: Начальное смещение адреса текущего буфера. Адрес буфера повторяется, когда моделирование проходит через буферы, отражая адресные границы буферов.

BufGntCurrentBuf: Текущий активный буфер, указанный от 1 до количества буферов в канале. BufGntCurrentBuf указывает на буфер, записываемый в (на стороне устройства записи), или буфер, считываемый из (на стороне устройства чтения).

BufRelCurrentBuf: Буфер, в данный момент освобожденный устройством чтения или устройством записи, указан в диапазоне от 1 до количества буферов в канале. На стороне считывателя, когда буфер освобождается, он доступен для записи. На стороне устройства записи, когда буфер освобождается, он доступен считывателю для чтения.

BufAvail: Количество буферов, доступных читателю для чтения. Это значение идентично на стороне устройства чтения и устройства записи.

BufTransfersCompleted: Текущее количество переданных буферов. Если в области памяти буферы не отброшены, количество переданных буферов совпадает BufReqID. Если буферы отброшены, BufReqID больше этого числа.

icFIFOEntries: Количество пакетов, записанных в interconnect FIFO.

icFIFODroppedCount: Количество пакетов, отброшенных из межсоединения FIFO.

На следующем рисунке показаны буферные сигналы после моделирования выравнивания гистограммы с использованием буфера видеокадров.

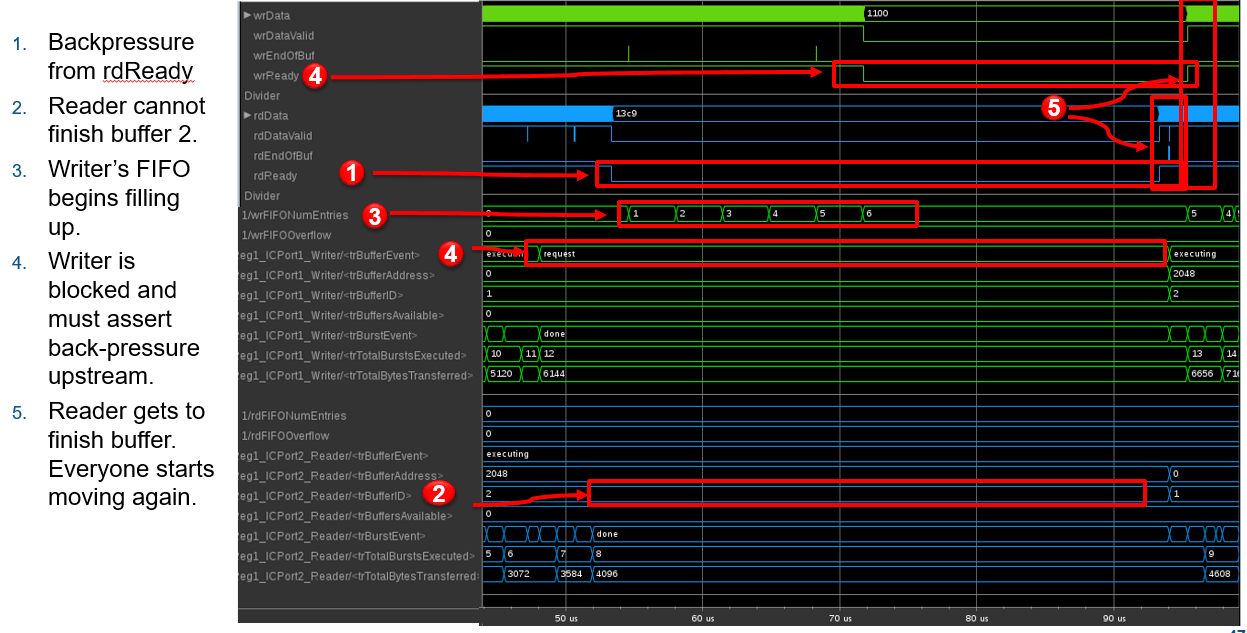

Можно связать работу модели памяти с интерфейсом протокола, чтобы понять производительность модели. На следующем рисунке показано, как связать работу модели памяти с интерфейсом протокола.

Логический анализатор | Канал памяти | Контроллер памяти