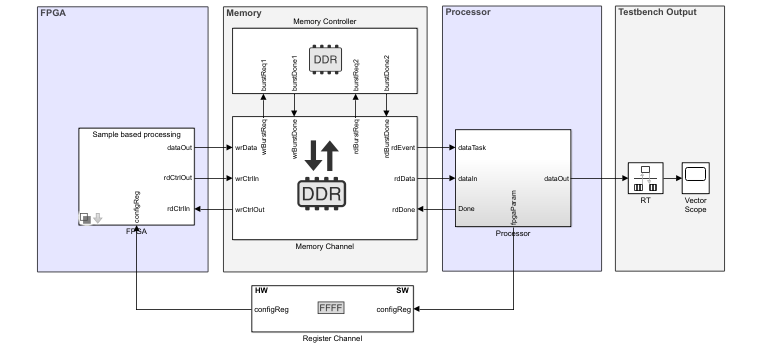

Модель SoC Blockset™ состоит из верхней модели, которая включает по крайней мере одну из этих ссылочных моделей.

Эталонная модель FPGA представляет часть FPGA устройства SoC. Верхняя модель может включать не более одной ссылочной модели FPGA. Сведения о настройке ссылочной модели FPGA см. в разделе Логика пользователя на FPGA.

Эталонная модель процессора представляет процессорную часть устройства SoC. Верхняя модель может включать в себя одну или несколько эталонных моделей процессора. Сведения о настройке эталонной модели процессора см. в разделе Управление программным обеспечением и задачами на процессоре.

Процессор и подсистемы FPGA взаимодействуют через канал памяти, канал регистрации или блок канала прерывания.

В дополнение к ссылочным моделям FPGA и процессоров, модель может включать дополнительные блоки SoC Blockset, такие как перечисленные здесь блоки, для моделирования интерфейсов и компонентов тестового стенда.

На следующем рисунке показана модель SoC Blockset с эталонной моделью FPGA, эталонной моделью процессора, взаимодействующей по каналу памяти.

Пример модели SoC Blockset см. в разделе Потоковая передача данных с оборудования на программное обеспечение.

SoC Blockset предоставляет шаблоны проектов для обычных сценариев использования SoC. Используйте их в качестве отправной точки для проектирования.