В этом примере проекта SoC FPGA генерирует тестовые данные и обрабатывает их в алгоритме FPGA перед передачей процессору с использованием общей памяти.

Откройте новую модель Simulink ®. Сохранить модель какsoc_hwsw_fpga_sample.slx в подпапку, с именем referencedmodels, в папке проекта.

На вкладке Модель (Modeling) щелкните Параметры модели (Model Settings). В окне Configuration parameters на панели Hardware Implementation установите для Hardware board значение None и установите для поставщика устройства значение ASIC/FPGA. На панели «Решатель» установите для параметра «Выбор решателя» > «Тип» значение Fixed-step. Нажмите кнопку ОК, чтобы применить изменения и закрыть параметры конфигурации.

Примечание

SoC Blockset™ требует, чтобы эталонные модели FPGA указывали предполагаемое аппаратное обеспечение развертывания, в данном случае FPGA.

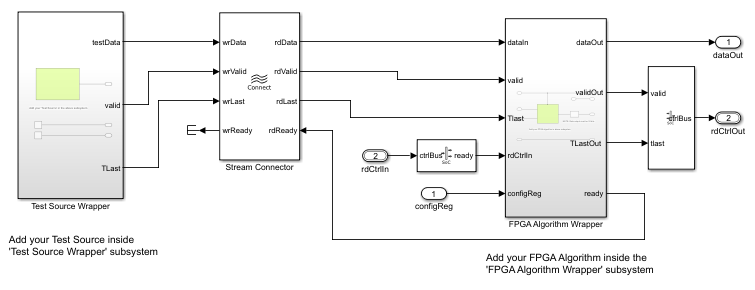

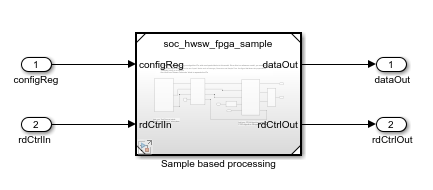

В новой модели с помощью блоков Stream Connector, SoC Bus Selector, SoC Bus Creator и Subsystem создайте следующую систему.

Примечание

Сигналы для rdCtrlIn и rdCtrlOut должны использовать типы сигналов шины, для которых установлено значение StreamS2MBusObj и StreamM2SBusObjсоответственно.

Совет

Если модель FPGA включает несколько IP-адресов, необходимо определить каждый IP-адрес как подсистему и подключить подсистемы с помощью блока Stream Connector или Video Stream Connector. Дополнительные сведения см. в разделе Рекомендации по использованию нескольких IP-адресов в модели FPGA.

В маске диалогового окна SoC Bus Creator установите для параметра Control type значение Valid.

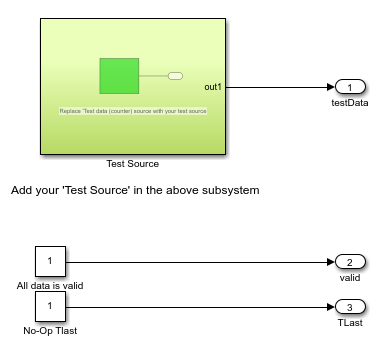

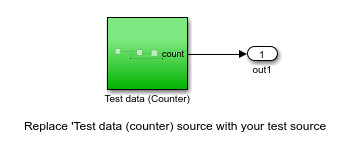

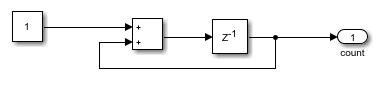

Test Source подсистема моделирует свободно работающий счетчик. Откройте окно Test Source и создайте следующую систему.

Примечание

Источники, All data is valid и No-Op Tlast, должен создать сигнал с boolean тип данных.

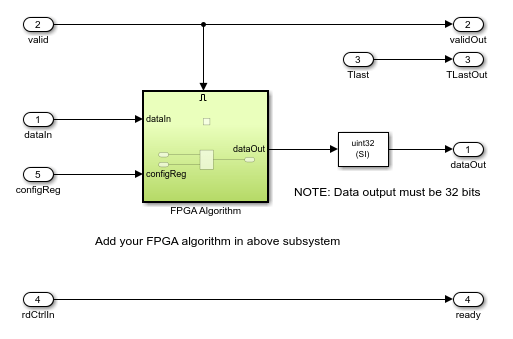

FPGA Algorithm подсистема моделирует умножение потоковых данных. Откройте окно FPGA Algorithm и используя блоки Enabled Subsystem, Logical Operator и Data Type Conversion, создайте следующую систему.

В папке проекта откройте модель soc_hwsw_top.slx.

Добавление блока подсистемы в FPGA площадь и маркировка блока FPGA.

В FPGA с помощью блока «Модель» создайте следующую систему.

Откройте маску диалогового окна «Блок модели» и задайте для параметра «Имя модели» значение soc_hwsw_fpga_sample.slx.

При передаче потока от FPGA к шаблону процессора подсистема FPGA использует вариант модели для выбора между моделью на основе образца, разработанной в этом разделе, и моделью на основе кадра. Модель на основе кадров позволяет быстрее моделировать, но не поддерживает генерацию кода.

Создатель шины SoC | Селектор шины SoC | Поточный соединитель