Используйте шаблон Поток от FPGA к процессору, чтобы создать модель SoC Blockset™ для проектирования пути данных от оборудования (FPGA) к программному обеспечению (процессору). Чтобы создать проект с использованием шаблона «Поток в процессор», выполните действия по созданию модели SoC с использованием шаблона набора блоков SoC.

Для обработки на основе проб дополнительные продукты не требуются.

Для обработки на основе кадров требуется Toolbox™ системы DSP.

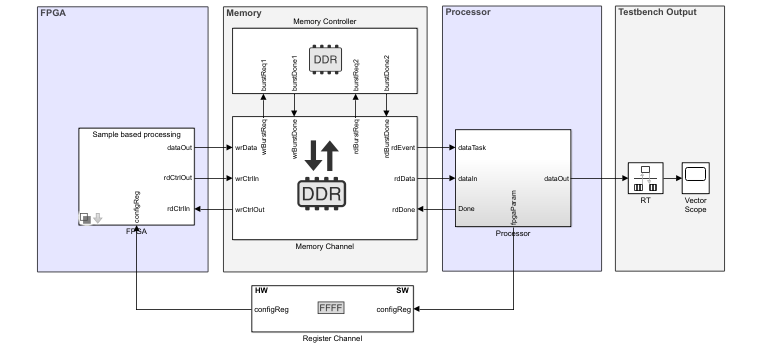

Этот шаблон моделирует счетчик как источник тестовых данных и минимальную логику для алгоритмов FPGA и процессора. Используйте этот шаблон в качестве руководства и замените алгоритм FPGA и алгоритм процессора собственными функциональными возможностями. Алгоритм FPGA представляет собой простое умножение входных данных из тестового источника и из параметра configReg. Процессор записывает файл configReg. Этот параметр моделируется с использованием блока Register Channel. Данные из алгоритма FPGA передаются процессору через блок канала памяти. Для параметра memory Channel Type установлено значение AXI4-Stream to Software via DMA, которая моделирует передачу данных DMA через общую внешнюю память.

Процессор считывает вычисленные данные из памяти и выполняет дополнительные вычисления, которые реализуются в шаблоне как проходной провод. Результаты моделирования можно просмотреть, дважды щелкнув блок «Vector Scope» в приемнике testbench.

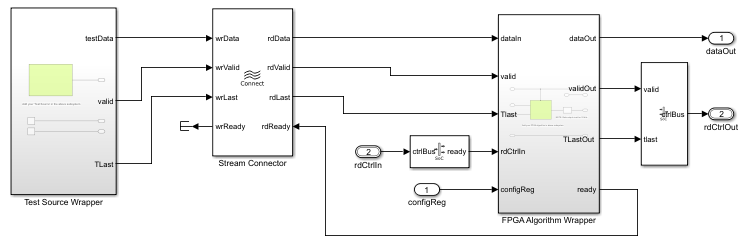

На панели инструментов MATLAB ® на вкладке «Ярлыки проекта» щелкните «Открыть образец модели FPGA», чтобы открыть модель FPGA. В модели выделены зеленым цветом две области, представляющие код пользователя: одна в блоке обертки алгоритма FPGA и одна в блоке обертки исходного кода теста.

Обертка алгоритма FPGA - дважды щелкните, чтобы открыть модель. Оболочка алгоритма содержит подсистему, выделенную зеленым цветом, с именем FPGA Algorithm. Этот блок имеет два входа и один выход и реализован как множитель. Замените этот блок собственным алгоритмом FPGA. При необходимости добавьте входные и выходные данные.

Оболочка тестового источника - этот блок включает тестовый источник и предназначен для генерации стимула в качестве входных данных алгоритма FPGA. Этот блок реализован как счетчик в данном шаблоне. Измените тестовый источник в соответствии с вашими потребностями или замените его альтернативным исходным блоком.

Совет

Если модель FPGA включает несколько IP-адресов, необходимо определить каждый IP-адрес как подсистему и подключить подсистемы с помощью блока Stream Connector или Video Stream Connector. Дополнительные сведения см. в разделе Рекомендации по использованию нескольких IP-адресов в модели FPGA.

Чтобы включить согласованное поведение моделирования, щелкните Открыть модель кадра FPGA (Open FPGA frame model) на вкладке Ярлыки проекта (Project Shortcuts) и повторите этот шаг. Для моделирования обработки кадров необходимо иметь лицензию DSP System Toolbox.

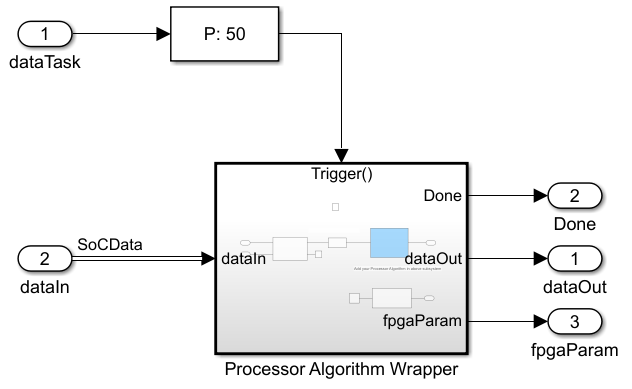

На панели инструментов MATLAB на вкладке «Ярлыки проекта» выберите «Открыть модель процессора». Оболочка процессора содержит подсистему, выделенную синим цветом и представляющую код пользователя для алгоритма процессора. Откройте оболочку Processor Algorithm и замените блок Processor Algorithm требуемым алгоритмом.

Верхняя модель шаблона также включает в себя канал регистрации для связи между процессором и моделью FPGA. Используйте канал регистрации для конфигурирования модели FPGA или для считывания и проверки регистров состояния. Блок канала регистрации в шаблоне включает в себя один регистр. Для добавления дополнительных регистров необходимо изменить параметры блока каналов регистров, алгоритм FPGA и алгоритм процессора:

Добавить регистры в канал регистров - дважды щелкните блок канала регистров, чтобы открыть маску блока и при необходимости добавить дополнительные регистры. Добавление регистров создает дополнительные порты в блоке канала регистрации. Дополнительные сведения см. в разделе Регистрация канала.

Добавление портов в модель процессора - переход к модели оболочки алгоритма процессора. Чтобы перейти к модели процессора, щелкните Открыть модель процессора (Open Processor model) на вкладке Ярлыки проекта (Project Shortcuts). Дважды щелкните обертку алгоритма процессора, чтобы изменить ее.

Для регистров записи добавьте выходной порт в модуль и добавьте логику для управления значением добавленного выходного порта. Для регистров считывания добавьте входной порт и логику для обработки информации, возвращаемой из регистра считывания. Из верхней модели подключите порт к блоку Register Channel.

Добавление портов в модель FPGA - переход к модели оболочки алгоритма FPGA. Для перехода к модели обработки FPGA/Frame щелкните Открыть образец модели FPGA (Open FPGA sample model) на вкладке Быстрые ссылки на проект (Project Shortcuts). Дважды щелкните обертку алгоритма FPGA, чтобы изменить ее.

Для регистров записи добавьте входной порт к модулю и логику для обработки информации, возвращаемой из регистра считывания. Для чтения регистров добавьте выходной порт и логику для управления значением добавленного выходного порта.

Для эквивалентного поведения при использовании варианта на основе образца Simulink ® повторите этот шаг для модели обработки на основе образца в оболочке FPGA.

Из верхней модели подключите новый порт к блоку Register Channel.