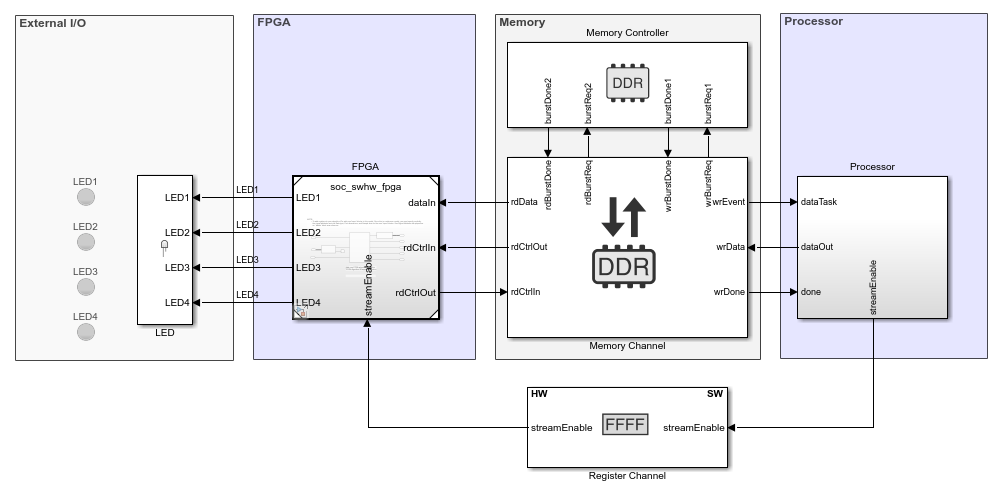

Используйте шаблон Поток от процессора к FPGA, чтобы создать модель SoC Blockset™ для проектирования пути данных от программного обеспечения (процессор) к аппаратному обеспечению (FPGA). Чтобы создать проект с использованием шаблона «Поток от процессора к FPGA», выполните действия, описанные в разделе Создание модели SoC с помощью шаблона набора блоков SoC. Затем добавьте алгоритм FPGA в подсистему FPGA и алгоритм процессора в подсистему процессора.

Шаблон Stream from Processor to FPGA включает три модели: модель Top, модель FPGA и модель Processor. Этот шаблон моделирует счетчик как источник тестовых данных и минимальную логику для алгоритмов FPGA и процессора. Используйте этот шаблон в качестве руководства, заменив алгоритм FPGA и алгоритм процессора собственными функциональными возможностями.

Процессор управляет выходным сигналом готовности в подсистеме оболочки алгоритма FPGA с помощью порта streamEnable. Процессор передает данные в FPGA через блок канала памяти. Параметр Channel Type в блоке Memory Channel имеет значение Software to AXI4-Stream via DMA для моделирования передачи данных прямого доступа к памяти (DMA) через совместно используемую внешнюю память.

Процессор генерирует тестовые данные и выполняет дополнительные вычисления. Дополнительные вычисления реализуются в шаблоне как проходной провод. Затем процессор записывает вычисленные данные в память.

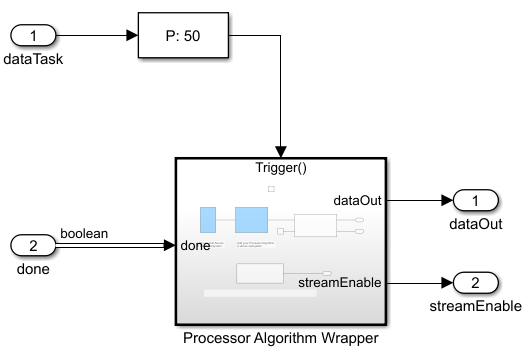

В окне MATLAB ® Toolstrip на вкладке Ярлыки проекта (Project Shortcuts) щелкните Открыть модель процессора (Open Processor model), чтобы открыть модель процессора. В подсистеме оболочки алгоритма процессора две области выделены синим цветом (который представляет код пользователя), как показано на этом рисунке. Одна выделенная область появляется в блоке «Алгоритм процессора», а другая выделенная область - в блоке «Тестовый источник».

Блок алгоритма процессора - замените блок внутреннего алгоритма процессора (выделен синим цветом) на требуемый алгоритм.

Блок тестового источника (Test Source block) - этот блок генерирует сигнал изменения скорости. Измените тестовый источник на необходимый или замените его альтернативным исходным блоком.

Включение потока для блока DUT - этот блок содержит управляющую логику, обеспечивающую загрузку памяти до начала непрерывной потоковой передачи. В логике управления сигнал streamEnable устанавливается высоким только после полного заполнения доступных буферов в канале памяти.

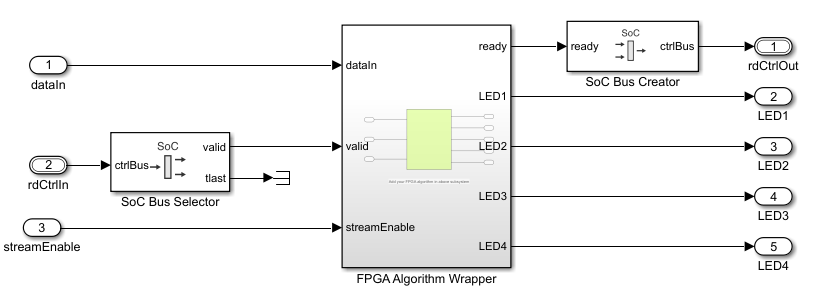

На панели инструментов MATLAB на вкладке «Ярлыки проекта» щелкните «Открыть модель FPGA», чтобы открыть модель FPGA. В подсистеме обертки алгоритма FPGA блок алгоритма FPGA выделяется зеленым цветом (который представляет код пользователя).

Дважды щелкните подсистему обертки алгоритма FPGA, чтобы открыть модель. Алгоритм FPGA извлекает четыре бита из входных данных для возбуждения светодиодов на аппаратных средствах. Состояние этих светодиодных индикаторов указывает на то, что процессор записывает данные потока в FPGA. Замените этот блок собственным алгоритмом FPGA. При необходимости добавьте входные и выходные данные.

Совет

Если модель FPGA включает несколько IP-адресов, определите каждый IP-адрес как подсистему и подключите подсистемы с помощью блока Stream Connector или Video Stream Connector. Дополнительные сведения см. в разделе Рекомендации по использованию нескольких IP-адресов в модели FPGA.

Чтобы включить согласованное поведение моделирования, на вкладке «Ярлыки проекта» перейдите на вкладку «Открыть модель FPGA» и повторите этот шаг.

Верхняя модель шаблона включает в себя канал регистрации для связи между процессором и моделью FPGA. Используйте канал регистрации для конфигурирования модели FPGA или считывания и проверки регистров состояния. Блок канала регистрации в шаблоне включает в себя один регистр. Чтобы добавить дополнительные регистры, измените параметры блока канала регистрации, алгоритм FPGA и алгоритм процессора, выполнив следующие действия.

Добавить регистры в канал регистров - дважды щелкните блок канала регистров, чтобы открыть маску блока и при необходимости добавить дополнительные регистры. Добавление регистров создает дополнительные порты в блоке канала регистрации. Дополнительные сведения см. в разделе Регистрация канала.

Добавление портов в модель процессора - переход к подсистеме оболочки алгоритма процессора. Чтобы перейти к модели процессора, щелкните Открыть модель процессора (Open Processor model) на вкладке Ярлыки проекта (Project Shortcuts). Дважды щелкните подсистему Processor Algorithm Wrapper, чтобы изменить ее.

Для регистров записи добавьте выходной порт и логику для управления значением добавленного выходного порта. Для регистров считывания добавьте входной порт и логику для обработки информации, возвращаемой из регистра считывания. Из верхней модели подключите порт к блоку Register Channel.

Добавление портов в модель FPGA - переход к подсистеме оболочки алгоритма FPGA. Чтобы перейти к модели FPGA, щелкните Открыть модель FPGA (Open FPGA model) на вкладке Ярлыки проекта (Project Shortcuts). Дважды щелкните подсистему FPGA Algorithm Wrapper, чтобы изменить ее.

Для регистров записи добавьте входной порт и логику для обработки информации, возвращаемой из регистра считывания. Для чтения регистров добавьте выходной порт и логику для управления значением добавленного выходного порта.

Из верхней модели подключите новый порт к блоку Register Channel.

Использование шаблона для создания модели SoC