Демодулируйте BPSK-модулированные данные

Communications Toolbox/Модуляция/Цифровая модуляция основной полосы/PM

Поддержка HDL-кода Communications Toolbox/Модуляция/PM

Блок BPSK Demodulator Baseband демодулирует сигнал, который был модулирован с помощью метода двоичной фазы сдвига манипуляции. Вход является представлением модулированного сигнала в основной полосе частот. Этот блок принимает скаляр или вектор-столбец входной сигнал. Входной сигнал должен быть комплексным сигналом в дискретном времени. Блок-диаграммы точки exp (jθ) и-exp (jθ) к 0 и 1, соответственно, где θ - Phase offset параметр.

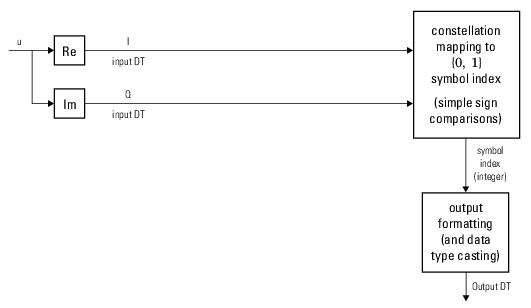

Диаграмма сигнала демодулятора BPSK с жестким решением для тривиального смещения фазы (кратного

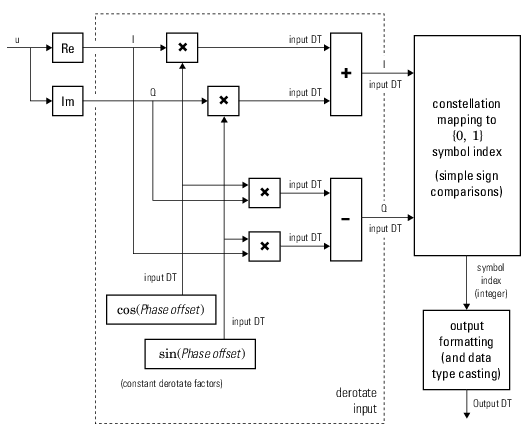

Схема сигнала демодулятора BPSK с плавающей точкой с жестким решением для смещения нетривиальной фазы

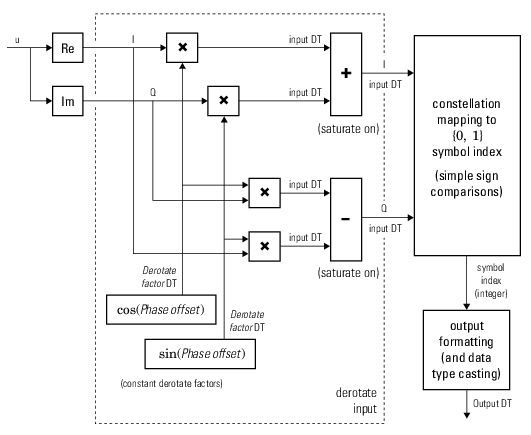

Схема сигнала фиксированной точки демодулятора BPSK с жестким решением для смещения нетривиальной фазы

Для получения дополнительной информации о точном LLR и приблизительных случаях LLR (мягкое решение), смотрите Точный алгоритм LLR и Аппроксимация алгоритма LLR в Руководстве пользователя Communications Toolbox.