Демодулируйте модулированные QPSK данные

PM, в цифровой поддиапазоне базовых частот модуляции

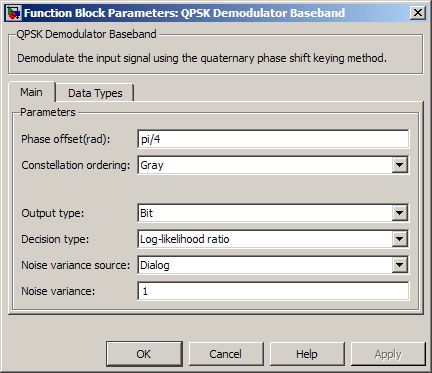

Блок Baseband демодулятора QPSK демодулирует сигнал, который был модулирован с помощью квадратурной фазы сдвига метода манипуляции. Вход является представлением модулированного сигнала в основной полосе частот.

Входной вход должен быть комплексным сигналом. Этот блок принимает скаляр или вектор-столбец входной сигнал. Дополнительные сведения о типах данных, которые поддерживает каждый порт блока см. в разделе Поддерживаемые типы данных.

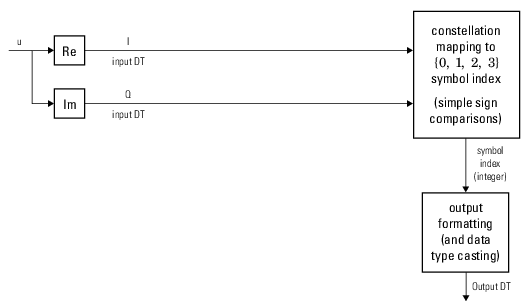

Схема сигнала демодулятора QPSK с жестким решением для тривиального смещения фазы (нечетное число, кратное

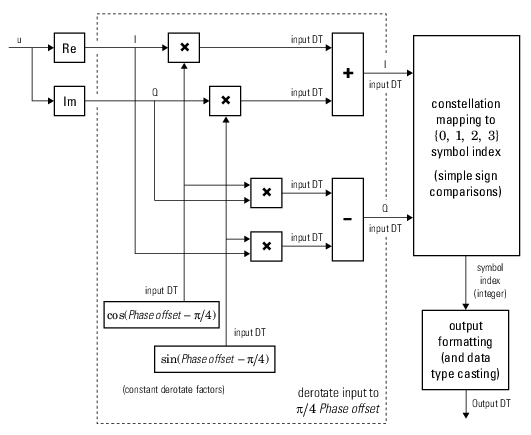

Схема сигнала с плавающей точкой демодулятора QPSK с жестким решением для смещения нетривиальной фазы

Схема сигнала фиксированной точки демодулятора QPSK с жестким решением для смещения нетривиальной фазы

Точные LLR и приблизительные случаи LLR (мягкое решение) описаны в Точном алгоритме LLR и аппроксимационном алгоритме LLR.

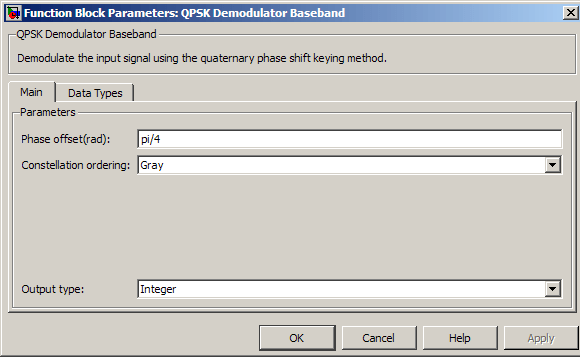

Фаза нулевой точки сигнального созвездия.

Определяет, как блок сопоставляет каждое целое число с парой выхода бит.

Определяет, состоит ли выход из целых чисел или бит.

Если для параметра Output type задано значение Integer и Constellation ordering установлено на Binary, затем блок сопоставляет точку

exp (j

к m, где и является Phase offset параметром, и m равно 0, 1, 2 или 3.

На странице с описанием для блока QPSK Modulator Baseband показаны сигнальные созвездия для случаев, когда Constellation ordering установлено на Binary или Gray.

Если для Output type задано значение Bit, тогда выход содержит пары двоичных значений, если Decision type задано значение Hard decision. Самый значительный бит (то есть самый левый бит в векторе), является первым битом, который выводит блок.

Если для Decision type задано значение Log-likelihood ratio или Approximate log-likelihood ratioзатем выход содержит побитовые LLR или приблизительные значения LLR, соответственно.

Задает использование жесткого решения, LLR или приблизительного LLR во время демодуляции. Этот параметр появляется, когда вы выбираете Bit из раскрывающегося списка Output type. Значения выхода для типов принятия решений Отношение логарифмической вероятности и Аппроксимация логарифмической вероятности совпадающего типа данных как вход значения. Для целочисленного выхода блок всегда выполняет демодуляцию жесткого решения.

Смотрите Точный Алгоритм LLR и Аппроксимация Алгоритма LLR для подробностей алгоритма.

Это поле появляется при Approximate log-likelihood ratio или Log-likelihood ratio выбран для Decision type.

Когда установлено значение Dialog, отклонение шума может быть задано в поле Noise variance. Когда установлено значение Portна блоке появляется порт, через который может быть введена отклонение шума.

Этот параметр появляется, когда для Noise variance source задано значение Dialog и задает отклонение шума в входном сигнале. Этот параметр настраивается в режиме normal mode, режим Accelerator и Rapid Accelerator mode.

Если вы используете Simulink® Coder™ быстрой симуляции (RSIM), чтобы создать исполняемый файл RSIM, тогда можно настроить параметр, не перекомпилируя модель. Это полезно для симуляций Монте-Карло, в которых вы запускаете симуляцию несколько раз (возможно, на нескольких компьютерах) с разным количеством шума.

Алгоритм LLR включает вычисление экспоненциалов очень больших или очень малых чисел с помощью арифметики конечной точности и дал бы:

Inf на -Inf если Noise variance очень высока

NaN если Noise variance и степень сигнала очень малы

В таких случаях используйте приблизительный LLR, так как его алгоритм не включает вычисление экспоненциалов.

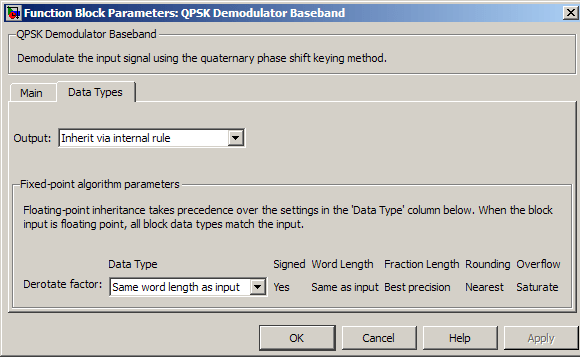

Панель типов данных для жесткого решения

Для битовых выходов, когда Decision type установлено в Hard decision, тип выходных данных может быть установлен на 'Inherit via internal rule', 'Smallest unsigned integer', double, single, int8, uint8, int16, uint16, int32, uint32, или boolean.

Для целочисленных выходов тип выходных данных может быть установлен на 'Inherit via internal rule', 'Smallest unsigned integer', double, single, int8, uint8, int16, uint16, int32, или uint32.

Когда этот параметр установлен в 'Inherit via internal rule' (настройка по умолчанию), блок наследует тип выходных данных от входного порта. Тип выходных данных будет таким же, как и тип входных данных, если вход является типом с плавающей точкой (single или double). Если входной тип входных данных является фиксированной точкой, тип выходных данных будет работать, как если бы этот параметр был установлен на 'Smallest unsigned integer'.

Когда этот параметр установлен в 'Smallest unsigned integer'тип выходных данных выбирается на основе настроек, используемых в панели Hardware Implementation диалогового окна Параметры конфигурации модели.

Если ASIC/FPGA выбран на панели Hardware Implementation, и Output type Bit, выход данных является идеальным минимальным однобитовым размером, т.е. ufix(1). Для всех других вариантов выбора это беззнаковое целое число с наименьшим доступным размером слова, достаточной для соответствия одному биту, обычно соответствующее размеру char (например uint8).

Если ASIC/FPGA выбран на панели Hardware Implementation, и Output type Integer, выход данных является идеальным минимальным двухбитовым размером, т.е. ufix(2). Для всех других вариантов выбора это беззнаковое целое число с наименьшим доступным размером слова, достаточной для соответствия двум битам, обычно соответствующее размеру char (например uint8).

Этот параметр применяется только, когда вход является фиксированной точкой и Phase offset не является даже произведением, кратным

Можно выбрать Same word length as input или Specify word length, в этом случае вы задаете размер слова используя поле входа.

Панель типов данных для мягкого решения

Для битовых выходов, когда Decision type установлено в Log-likelihood ratio или Approximate log-likelihood ratioтип выходных данных наследуется от входа (например, если вход имеет тип данных doubleвыходные выходы также имеют тип данных double).

| Порт | Поддерживаемые типы данных |

|---|---|

Вход |

|

Вар |

|

Выход |

|