Вычислите величину и угол фазы комплексного сигнала - оптимизировано для генерации HDL-кода с помощью алгоритма CORDIC

DSP System Toolbox Поддержка HDL/математические функции

Блок Complex to Magnitude-Angle HDL Optimized вычисляет величину и угол фазы комплексного сигнала и обеспечивает аппаратно удобные сигналы управления. Чтобы достичь эффективной реализации HDL, блок использует конвейерный алгоритм вращения координат цифрового компьютера (CORDIC).

Можно использовать этот блок для реализации таких операций, как atan2 в оборудовании.

dataIn - Комплексный входной сигналКомплексный входной сигнал, заданный как скаляр, вектор-столбец, представляющий выборки во времени или векторе-строке, представляющий каналы. Использование векторного входа увеличивает пропускную способность данных при использовании большего количества аппаратных ресурсов. Блок реализует логику преобразования параллельно для каждого элемента вектора. Вектор входа может содержать до 64 элементов.

double и single типы данных поддерживаются для симуляции, но не для генерации HDL-кода.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixed point

validIn - Валидность входных данныхBoolean скалярКогда validIn trueблок захватывает данные от dataIn входного порта. Сигнал validIn применяется ко всем выборкам в векторном входном сигнале.

Типы данных: Boolean

Magnitude - Величина входного сигналаВеличину входного сигнала, возвращенного в виде скаляра, вектора-столбца, представляющего выборки во времени или векторе-строке, представляющую каналы. Размерности этого порта совпадают с размерностями порта dataIn.

Чтобы включить этот порт, установите параметр Output format равным Magnitude and Angle или Magnitude.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

Angle - Угол входного сигналаУгол входного сигнала, возвращаемый как скаляр, вектор-столбец, представляющая выборки во времени или векторе-строке, представляющая каналы. Размерности этого порта совпадают с размерностями порта dataIn.

Чтобы включить этот порт, установите параметр Output format равным Magnitude and Angle или Angle.

Типы данных: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | fixdt([],N,0)

validOut - Валидность выходных данныхBoolean скалярБлок устанавливает validOut на true с каждым действительным данным, возвращаемым на Magnitude или Angle выходных портах. Сигнал validOut применяется ко всем выборкам в векторном выходном сигнале.

Типы данных: Boolean

Number of iterations source - Источник количества итерацийAuto (по умолчанию) | Property Чтобы задать количество итераций, чтобы ввести WL − 1, выберите Auto. Если вход имеет тип данных double или singleколичество итераций по умолчанию устанавливается равным 16.

Чтобы задать количество итераций при помощи Number of iterations параметра, выберите Property.

Number of iterations - Количество итераций CORDICКоличество итераций должно быть меньше или равно входным WL − 1. Задержка блока зависит от количества выполненных итераций. Для получения информации о задержках смотрите Latency.

Чтобы включить этот параметр, установите Number of iterations source равным Property.

Output format - Формат выходного сигналаMagnitude and Angle (по умолчанию) | Magnitude | AngleИспользуйте этот параметр, чтобы указать, какие выходные порты включены.

Чтобы включить Magnitude и Angle выходные порты, выберите Magnitude and Angle (по умолчанию).

Чтобы включить Magnitude выходной порт и отключить Angle выходной порт, выберите Magnitude.

Чтобы включить Angle выходной порт и отключить Magnitude выходной порт, выберите Angle.

Angle format - Выход углаNormalized (по умолчанию) | RadiansЧтобы вернуть выход Angle как значение с фиксированной точкой, которое нормализует углы в области значений [-1,1], выберите Normalized. Для получения дополнительной информации смотрите Нормированный формат угла.

Чтобы возвратить Angle выход как значение фиксированной точки в области значений [-π, π], выбирают Radians. При использовании этого блока для реализации atan2 function, установите этот параметр равным Radians.

Scale output - Вывод шкалon (по умолчанию) | offВыберите этот параметр, чтобы умножить вывод Angle на обратный коэффициент усиления CORDIC. Блок реализует этот коэффициент усиления, используя архитектуру shift-and-add для умножителя. Эта реализация может увеличить длину критического пути в вашем проекте.

Примечание

Если вы очистите этот параметр и примените коэффициент усиления CORDIC в другом месте вашего проекта, вы должны исключить термин Поскольку алгоритм квадрантного отображения заменяет первую итерацию CORDIC, отображая входы на область значений угла [0, Коэффициент усиления является продуктом cos (atan (2-n)), для n от 1 до Number of iterations - 1.

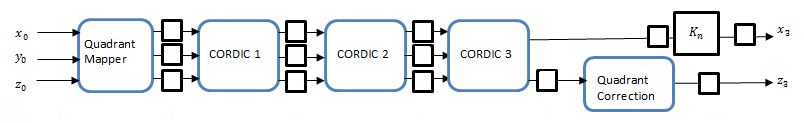

Алгоритм CORDIC является аппаратно-удобным методом для выполнения тригонометрических функций. Это итерационный алгоритм, который аппроксимирует решение, сходясь к идеальной точке. Блок использует режим векторизации CORDIC, чтобы итерационно повернуть вход на действительную ось.

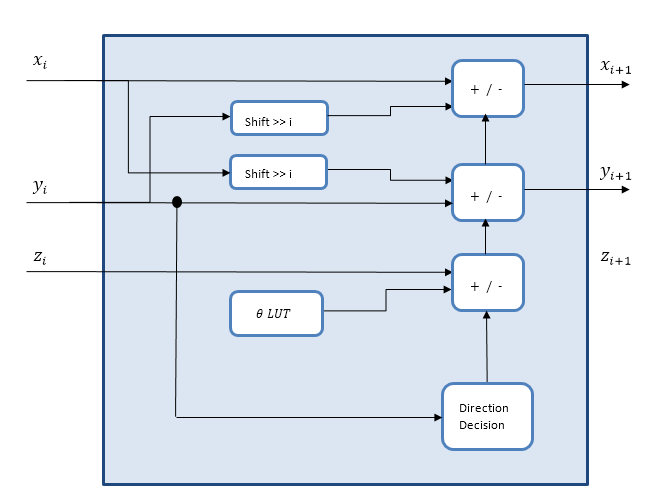

Метод Гивенса для поворота комплексного числа x + iy на угол Направление вращения d составляет + 1 для против часовой стрелки и − 1 для по часовой стрелке.

Для аппаратной реализации выделите cos

Чтобы повернуть вектор на действительную ось, выберите серию поворотов, так что . Удалите член cos, чтобы каждое итерационное вращение использовало только сдвиги и add.

Объедините отсутствующие условия cosв из каждой итерации в константу и примените его с одним умножителем к результату окончательного вращения. Выход величины является масштабированным конечным значением x. Угол выхода, z, является суммой углов поворота.

Область сходимости для стандартного вращения CORDIC составляет ≈ ± 99,7 °. Чтобы обойти это ограничение, прежде чем делать любое вращение, блок преобразует вход в область значений [0 ,

if abs(x) > abs(y) input_mapped = [abs(x), abs(y)]; else input_mapped = [abs(y), abs(x)]; end

Квадрант отображения экономит оборудование ресурсы и уменьшает задержки, уменьшая количество этапов CORDIC на единицу. Коэффициент усиления CORDIC, Kn, поэтому не включает в себя член n = 0, или cos (в/4).

После того, как итерации CORDIC завершены, блок корректирует угол назад в его исходное положение. Сначала он корректирует угол к правильной стороне

if abs(x) > abs(y) angle_unmapped = CORDIC_out; else angle_unmapped = (pi/2) - CORDIC_out; end

if (x < 0)

if (y < 0)

output_angle = - pi + angle_unmapped;

else

output_angle = pi - angle_unmapped;

else

if (y<0)

output_angle = -angle_unmapped;

Блок генерирует конвейерную архитектуру HDL для максимизации пропускной способности. Каждая итерация CORDIC выполняется на одной стадии конвейера. Множитель усиления, если он включен, реализован с помощью канонической логики со знаком (CSD).

Если вы используете векторный вход, этот блок наследует эту архитектуру параллельно для каждого элемента вектора.

В следующей таблице показана Magnitude и Angle длина выходного слова (WL) для конкретной длины входного слова (WL). FL обозначает дробную длину, используемую в представлении с фиксированной точкой.

| Вход Размера слова | Выход Величины Размера слова |

|---|---|

| fixdt (0,WL,FL) | fixdt (0,WL + 2,FL) |

| fixdt (1,WL,FL) | fixdt (1,WL + 1,FL) |

| Вход Размера слова | Выход угла Размера слова | |

|---|---|---|

| fixdt ([], WL, FL) | Радианы | fixdt (1,WL + 3,WL) |

| Нормализованный | fixdt (1, WL + 3, WL + 2) | |

Логика CORDIC на каждом этапе конвейера реализует одну итерацию. Для каждой ступени трубопровода сдвиг и поворот угла являются постоянными.

Когда вы задаете Output format Magnitudeблок не генерирует HDL-код для логики накопления углов и квадрантной коррекции.

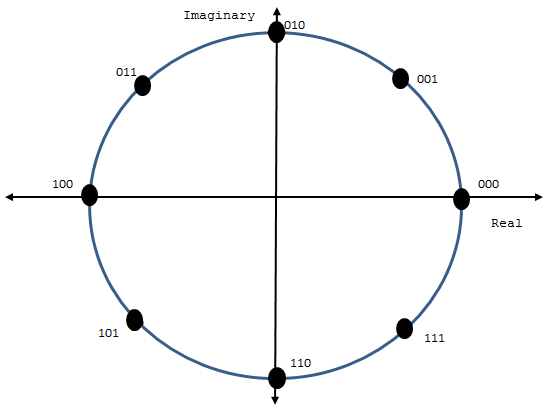

Этот формат нормализует значения радиального угла с фиксированной точкой вокруг модуля круга. Это использование бит может быть более эффективным, чем использование радианов области значений [0, 2в]. Кроме того, этот нормированный формат угла позволяет обернуть угол на 0 или 2, без дополнительного обнаружения и правильной логики.

Для примера, представление угла с 3 битами результатов в этих нормированных значениях.

Блок нормализует углы через [0, π/4] и наносит на карту их к правильному октанту в конце вычисления.

Когда применяется допустимый вход, допустимый выход приходит после Number of iterations + 4 циклов.

Когда вы устанавливаете параметр Number of iterations source равным Propertyблок немедленно показывает задержку. Когда вы задаете Number of iterations source Autoблок вычисляет задержку на основе типа данных входного порта и отображает задержку при обновлении модели.

Когда вы устанавливаете параметр Number of iterations source равным Auto, количество итераций является входным WL − 1, а задержка - входным WL + 3. Если вход имеет тип данных double или single, количество итераций 16, и задержка 20.

Эффективность была измерена для строения по умолчанию, с отключенным масштабированием выхода и fixdt(1,16,12) вход. Когда сгенерированный HDL-код синтезируется в Xilinx® Virtex®-6 (XC6VLX240T-1FFG1156) FPGA, проект достигает тактовой частоты 260 МГц. Он использует следующие ресурсы.

| Ресурс | Используемое число |

|---|---|

| LUT | 882 |

| FFS | 792 |

Xilinx LogiCORE® DSP48 | 0 |

| Блокируйте ОЗУ (16K) | 0 |

Эффективность синтезированного HDL-кода варьируется в зависимости от вашей цели и опций синтеза. Когда вы используете векторный вход, использование ресурса примерно в VectorSize раз превышает использование скалярного ресурса.

Этот блок поддерживает генерацию кода C/C + + для Simulink® режимы Accelerator и Rapid Accelerator и для генерации компонентов DPI.

HDL Coder™ предоставляет дополнительную опцию строения, которая влияет на реализацию HDL и синтезированную логику.

Этот блок имеет одну архитектуру HDL по умолчанию.

| ConstrainedOutputPipeline | Количество регистров для размещения на выходах путем перемещения существующих задержек в рамках вашего проекта. Распределённая конвейеризация не перераспределяет эти регистры. Значение по умолчанию является |

| InputPipeline | Количество входных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

| OutputPipeline | Количество выходных этапов конвейера для вставки в сгенерированный код. Распределённая конвейеризация и ограниченная выходная конвейеризация могут перемещать эти регистры. Значение по умолчанию является |

Этот блок поддерживает генерацию кода для сложных сигналов.

atan2 | dsp.HDLComplexToMagnitudeAngle | Complex to Magnitude-Angle (Simulink)

1. Если смысл перевода понятен, то лучше оставьте как есть и не придирайтесь к словам, синонимам и тому подобному. О вкусах не спорим.

2. Не дополняйте перевод комментариями “от себя”. В исправлении не должно появляться дополнительных смыслов и комментариев, отсутствующих в оригинале. Такие правки не получится интегрировать в алгоритме автоматического перевода.

3. Сохраняйте структуру оригинального текста - например, не разбивайте одно предложение на два.

4. Не имеет смысла однотипное исправление перевода какого-то термина во всех предложениях. Исправляйте только в одном месте. Когда Вашу правку одобрят, это исправление будет алгоритмически распространено и на другие части документации.

5. По иным вопросам, например если надо исправить заблокированное для перевода слово, обратитесь к редакторам через форму технической поддержки.