Сигналы синхроимпульса состоят из синхроимпульсов, сбросов и синхроимпульсов. Во время генерации кода HDL- Coder™ создает тактовые сигналы на основе последовательных элементов, таких как постоянные переменные или Delay блоки, которые вы используете в проекте. По умолчанию один главный синхроимпульс и один главный сброс управляют всеми последовательными элементами в проекте.

Если вы используете стойкие переменные в MATLAB®HDL Coder генерирует сигналы пакета синхроимпульсов. Постоянная переменная является локальной переменной в функции MATLAB, которая сохраняет свое значение в памяти между вызовами функции. Для генерации кода функции должны инициализировать постоянную переменную, если она пуста. Для получения дополнительной информации см. persistent.

Допустим, этот код MATLAB, который использует постоянную переменную n.

function y = persist_fcn(u) persistent n if isempty(n) n = 1; end y = n; n = n + u; end

Когда вы генерируете код, HDL Coder создает сигналы времени, сброса и включения синхроимпульса. Эти сигналы названы как clk, reset, и clk_enable в HDL-коде. Чтобы узнать, как сгенерировать HDL-код, смотрите Basic HDL Code Generation и FPGA Synthesis из MATLAB.

Этот код показывает сгенерированный код Verilog для модели. Чтобы соответствовать поведению постоянной переменной MATLAB, HDL-код использует всегда блок. На положительном ребре синхросигнала, когда сброс низок и сигнал включения высок, значение tmp присваивается переменной n после задержки 1 ns.

`timescale 1 ns / 1 ns

module persist_fcn_fixpt

(clk, reset, clk_enable,

u, ce_out, y);

input clk, reset, clk_enable;

input u; // ufix1

output ce_out;

output y; // ufix1

..

assign enb = clk_enable;

assign p4tmp_1 = {1'b0, u};

assign tmp = n + p4tmp_1;

always @(posedge clk or posedge reset)

begin : n_reg_process

if (reset == 1'b1) begin

n <= 2'b01;

end

else begin

if (enb) begin

n <= tmp;

end

end

end

assign y = n[0];

assign ce_out = clk_enable;

endmodule // persist_fcn_fixpt

См. также «Постоянные переменные и переменные стойкого массива».

Чтобы смоделировать последовательные элементы в Simulink® и сгенерировать синхросигналы, вы можете использовать различные виды блоков Delay, Stateflow® графики или стойкие переменные в блоках MATLAB Function или MATLAB System блоках. Генератор кода отображает шаги расчета, которые вы задаете в своей модели, чтобы синхронизировать циклы в HDL- проекта. По умолчанию модель является одной скоростью, что означает, что один шаг расчета модуля в Simulink преобразуется в один такт в HDL-коде.

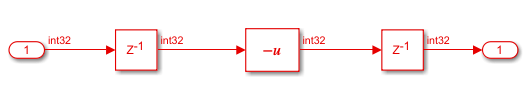

Например, рассмотрите эту модель, которая выводит унарный минус входа после двух модулей шага расчета. Вход имеет int32 как тип выходных данных.

Когда вы генерируете код, HDL Coder создает сигналы времени, сброса и включения синхроимпульса. Эти сигналы названы как clk, reset, и clk_enable в HDL-коде. Чтобы узнать, как сгенерировать код, см. «Генерация HDL-кода из Simulink».

Этот код показывает сгенерированный код Verilog для модели. Чтобы соответствовать поведению блоков Delay Simulink, HDL-код использует всегда блок для каждого блока Delay. При положительном ребре синхросигнала, когда сброс низок и сигнал включения высок, вход передается на выход после модуля задержки. Один блок всегда задерживает вход по 1 ns перед вычислением унарного минуса. Другой блок всегда вычисляет унарный минус после 1 ns.

`timescale 1 ns / 1 ns

module unary_minus

(clk, reset, clk_enable,

In1, ce_out, Out1);

input clk, reset, clk_enable;

input signed [31:0] In1; // int32

output ce_out;

output signed [31:0] Out1; // int32

...

assign enb = clk_enable;

always @(posedge clk or posedge reset)

begin : Delay_process

if (reset == 1'b1) begin

Delay_out1 <= 32'sb0;

end

else begin

if (enb) begin

Delay_out1 <= In1;

end

end

end

...

always @(posedge clk or posedge reset)

begin : Delay2_process

if (reset == 1'b1) begin

Delay2_out1 <= 32'sb0;

end

else begin

if (enb) begin

Delay2_out1 <= Unary_Minus_out1;

end

end

end

...

endmodule // unary_minus

Если вы используете различные шаги расчета в модели или активируете оптимизацию скорости и площади, модель становится многоразовой. Чтобы узнать о генерации пакета синхроимпульсов из многоскоростных моделей, смотрите Генерацию кода из многоскоростных моделей.