В этом примере показано, как можно сгенерировать HDL-код для модели простого счетчика в Simulink®. Эта модель совместима с генерацией HDL-кода. Чтобы создать эту модель счетчика, смотрите Создание HDL-совместимой модели Simulink.

Можно либо создать свою собственную HDL-совместимую модель, такую как модель счетчика, либо выбрать из:

HDL Coder™ примеры моделей, доступных в hdlcoderdemos папка.

cd (fullfile(matlabroot,'toolbox','hdlcoder','hdlcoderdemos'))

Эти модели доступны в MATLAB® путь. Для примера можно выбрать симметричную модель конечной импульсной характеристики Filter Model. Чтобы использовать эту модель, введите:

sfir_fixed

Шаблоны Simulink для генерации HDL-кода. Можно использовать шаблоны для моделирования регистров, ПЗУ, базовых арифметических операций, комплексных умножителей, регистров сдвига и так далее.

Чтобы выбрать шаблон, на панели инструментов MATLAB нажмите![]() кнопку и перейдите к разделу HDL Coder. См. Использование шаблонов Simulink для генерации HDL-кода.

кнопку и перейдите к разделу HDL Coder. См. Использование шаблонов Simulink для генерации HDL-кода.

Перед генерацией HDL-кода можно проверить и обновить модель на совместимость с HDL с помощью HDL Code Advisor. См. «Проверка совместимости HDL-файлов модели Simulink с использованием HDL-код Advisor».

Откройте эту модель, чтобы увидеть простой счетчик. Модель отсчитывает от нуля до порогового значения, а затем оборачивается назад к нулю. Значение порога установлено в 15. Чтобы изменить пороговое значение, измените значение входа на count_threshold порт. Сигнал Enable определяет, отсчитывается ли счетчик вверх или содержит предыдущее значение. Значение 1 указывает, что счетчик пересчитывается вверх постоянно.

Для модели счетчика, HDL_DUT подсистема является DUT. Чтобы сгенерировать код для DUT:

На вкладке Apps выберите HDL Coder.

Выберите Подсистему DUT в модели и убедитесь, что это имя Subsystem появится в опции Code for на вкладке HDL Code. Чтобы запомнить выбор, закрепите эту опцию. Нажмите Generate HDL Code.

По умолчанию HDL Coder генерирует VHDL- кода в целевой hdlsrc папка.

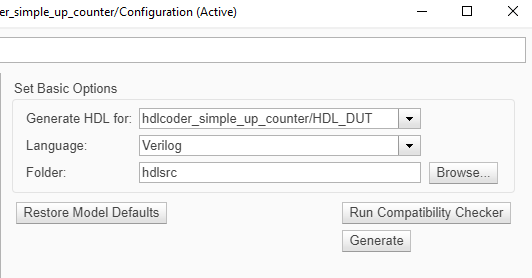

Чтобы сгенерировать код Verilog для модели счетчика:

На вкладке HDL Code нажмите Settings.

На панели HDL Code Generation для Language выберите Verilog. Щелкните Apply и затем щелкните Generate.

HDL Coder компилирует модель перед генерацией кода. В зависимости от параметров отображения модели, таких как типы данных портов, модель может измениться во внешнем виде после генерации кода. Когда генерация кода продолжается, HDL Coder отображает сообщения о прогрессе в командной строке MATLAB со ссылками на конфигурацию модели и сгенерированные файлы. Чтобы просмотреть файлы в редакторе MATLAB, щелкните ссылки.

Процесс завершен и отобразит сообщение:

### HDL Code Generation Complete.

Значок папки для hdlsrc папка появится в текущей папке. Чтобы просмотреть сгенерированные коды и скриптов, дважды кликните hdlsrc папка, а затем дважды кликните папку, имя которой совпадает с именем модели, для которой вы сгенерированными HDL-кодами.

HDL_DUT.vhd: VHDL® код, который содержит определение сущности и архитектуру RTL, реализуя счетчик, который вы проектировали. Если вы сгенерировали код Verilog, вы получите HDL_DUT.v файл.

HDL_DUT_compile.do: Менторская графика® ModelSim® скрипт компиляции.

HDL_DUT_map.txt: Отображение файла, который сопоставляет сгенерированные сущности или модули в HDL-коде с подсистемами в модели, которая их сгенерировала. См. «Трассировка кода с использованием файла отображения».

HDL_DUT_report.html: Отчет о проверке HDL отображает состояние генерации HDL-кода и предупреждения или сообщения.

gm_hdlcoder_simple_up_counter.slxСгенерированная модель, которая поведенчески представляет HDL-код в среде моделирования Simulink.

HDL Coder создает поведенческую модель HDL-кода, называемую generated model. Имя сгенерированной модели совпадает с именем исходной модели и имеет префикс gm_. Сгенерированная модель является bit-true и циклически точной к сгенерированному HDL-коду. Эта модель показывает эффект реализации блоков и оптимизации скорости и площади, которые вы задали. Смотрите также Оптимизация скорости и площади в HDL Coder.

Чтобы открыть сгенерированную модель для счетчика, введите:

gm_hdlcoder_simple_up_counter

Для модели счетчика, когда оптимизации отключены, сгенерированная модель идентична исходной модели.

Чтобы легче идентифицировать отображение между исходной моделью и сгенерированным HDL-кодом, сгенерируйте отчет о трассируемости. Используйте отчет для перехода от блока в модели к сгенерированному коду для этого блока и от кода к блоку в вашей модели.

Чтобы сгенерировать отчет о трассируемости:

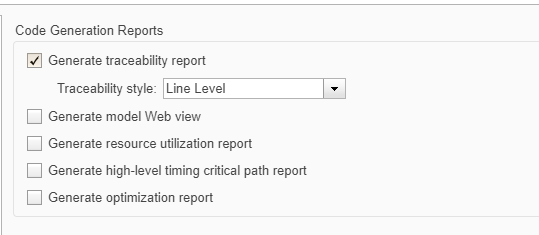

На вкладке HDL Code щелкните Settings > Report Options.

На панели HDL Code Generation > Report выберите Generate traceability report, а затем сгенерируйте HDL-код для HDL_DUT подсистема

После генерации кода откроется окно Отчет генерации кода. HDL Coder записывает файлы отчетов генерации кода в hdlsrc\html\ папка папки сборки. При закрытии отчета можно перейти в эту папку для повторного открытия отчета.

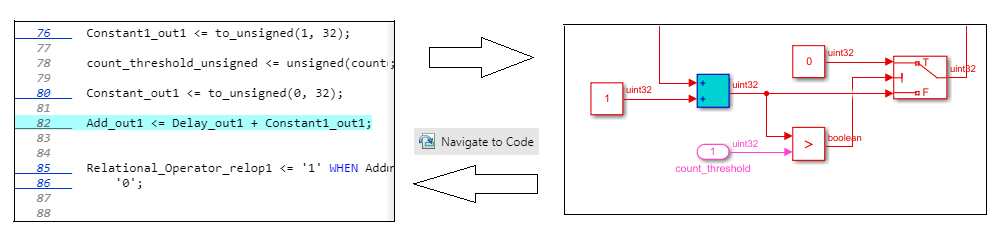

Для перехода от HDL-кода к модели:

В отчете генерации кода перейдите к разделу Traceability Report, а затем щелкните по ссылкам в разделе Code Location.

Выберите гиперссылку на строку кода, чтобы подсветить соответствующий блок в вашей модели.

Чтобы перейти от блока в модели к HDL-коду, выберите этот блок, а затем нажмите кнопку Navigate to Code в Review Results разделе вкладки HDL Code.

Смотрите Навигация между моделью Simulink и HDL-кодом при помощи трассируемости и создания и использования отчетов генерации кода.

В Generated Source Files разделе, если вы нажимаете HDL- файла HDL_DUT, вы видите сигналы clk, reset, и clk_enable. Эти сигналы являются тактовыми, сбросными и тактовыми сигналами, которые управляют триггерами на целевом компьютере. HDL Coder генерирует эти сигналы в коде в зависимости от последовательных элементов, таких как блоки Delay, которые вы используете в своей модели. Смотрите Генерацию сигналов набора синхроимпульсов в HDL Coder.

Чтобы подтвердить поведенческую модель HDL-кода с помощью вашей исходной модели, сгенерируйте модель валидации. Модель валидации содержит и исходную модель, и сгенерированную модель. Он сравнивает выходы обеих моделей с помощью тестовых векторов, которые вы предоставили в исходной модели.

Чтобы сгенерировать модель валидации:

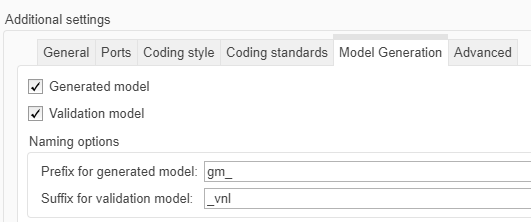

На вкладке HDL Code нажмите Settings.

На вкладке HDL Code Generation > Global Settings > Model Generation выберите Validation model, а затем сгенерируйте HDL-код для HDL_DUT подсистема.

В журналах генерации кода отображается ссылка на модель валидации. Модель валидации имеет тот же префикс, что и сгенерированная модель, а также имеет суффикс _vnl. Для модели счетчика модель валидации имеет имя gm_hdlcoder_simple_up_counter_vnl.slx. Вы можете найти эту модель в той же папке, что и сгенерированная модель. Чтобы открыть эту модель, введите:

gm_hdlcoder_simple_up_counter_vnl

После моделирования модели дважды кликните Compare подсистема, а затем перейдите внутрь Assert_Out подсистема. Если вы открываете блок Scope, вы видите, что err сигнал имеет значение нуля, что означает, что выход сгенерированной модели совпадает с исходной моделью.

Перед развертыванием проекта на целевом компьютере проверьте сгенерированный HDL-код. Из hdlsrc папка, перейдите к текущей рабочей папке. Смотрите Проверьте сгенерированный HDL-код из модели Simulink.

hdlset_param | hdlsetup | makehdl