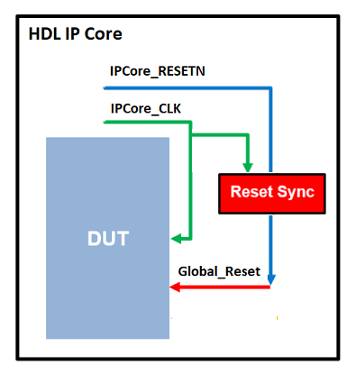

IP-ядро HDL DUT и логика декодера адресов в оболочке AXI4 Slave интерфейса ядра HDL управляются глобальным сигналом сброса. Если вы генерируете HDL-ядро IP без каких-либо AXI4 ведомых интерфейсов, HDL- Coder™ не генерирует AXI4 подчиненного оболочки интерфейса. Глобальный сигнал сброса становится таким же, как и сигнал сброса ядра IP и управляет ядром IP HDL для DUT. Чтобы узнать, как можно сгенерировать IP-ядро без AXI4 ведомых интерфейсов, смотрите Generate Board-Independent HDL IP Core из модели Simulink.

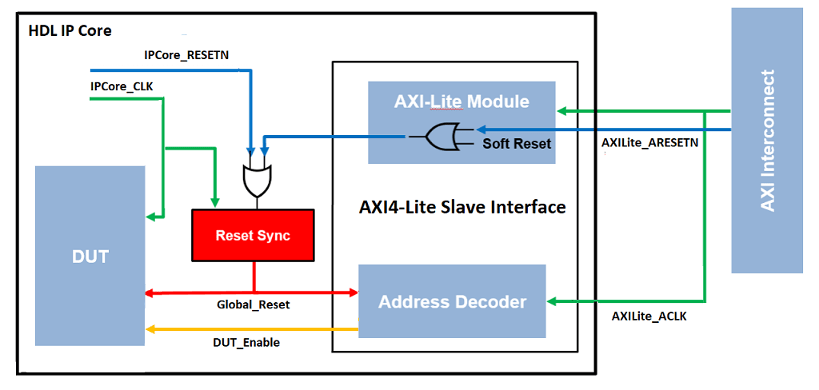

Когда вы генерируете AXI4 подчиненные интерфейсы в IP-ядре HDL, сигнал глобального сброса управляется тремя сигналами сброса: внешним сбросом ядра IP, сигналом сброса соединения AXI и мягким сбросом для ядра процессора ARM. Глобальный сигнал сброса в этом случае управляет ядром IP HDL для DUT и логикой декодера адресов в AXI4 подчиненной оболочке.

The IPCore_Clk и AXILite_ACLK должен быть подключен к тому же источнику синхроимпульса. The IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса.

Эти сигналы сброса могут быть синхронными или асинхронными. Использование сигналов асинхронного сброса может быть проблематичным и привести к потенциальным проблемам метастатичности в триггерах, когда сброс отменяет утверждения в фиксирующем окне синхроимпульса. Чтобы избежать генерации возможных метастабельных значений при объединении сигналов сброса, HDL Coder автоматически вставляет логику синхронизации сброса, как обозначено Reset Sync блок. Логика синхронизации сброса синхронизирует глобальный сигнал сброса в области основного синхроимпульса IP. Эта логика вставляется, когда вы открываете HDL Workflow Advisor и запускаете Generate RTL Code and IP Core задачу IP Core Generation рабочий процесс.

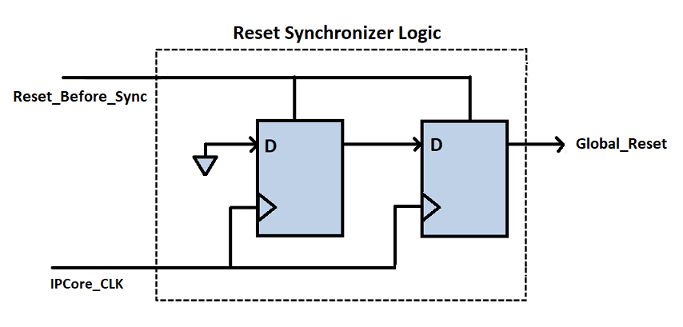

Логика синхронизации сброса содержит два обратных триггера, которые синхронны с IPCore_CLK сигнал. Триггеры гарантируют, что снятие значения сигнала сброса происходит после двух тактов, когда IPCore_CLK сигнал становится высоким. Это синхронное отклонение избегает генерации сигнала глобального сброса, который имеет возможные метастаблируемые значения.

Логика работает по-разному в зависимости от того, задаете ли вы Reset type как Synchronous или Asynchronous на модели. Если ваш Reset type AsynchronousЛогика синхронизации утверждает сигнал сброса асинхронно и снимает сигнал сброса синхронно. Для примера этот код иллюстрирует сгенерированный Verilog® код для логики синхронизации сброса при генерации ядра IP с асинхронным сбросом.

...

...

reg_reset_pipe_process : PROCESS (clk, reset_in)

BEGIN

IF reset_in = '1' THEN

reset_pipe <= '1';

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

reset_pipe <= const_0;

END IF;

END IF;

END PROCESS reg_reset_pipe_process;

reg_reset_delay_process : PROCESS (clk, reset_in)

BEGIN

IF reset_in = '1' THEN

reset_out <= '1';

ELSIF clk'EVENT AND clk = '1' THEN

IF enb = '1' THEN

reset_out <= reset_pipe;

END IF;

END IF;

END PROCESS reg_reset_delay_process;

END rtl;

Если ваш Reset type SynchronousЛогика синхронизации устанавливает и отключает сигнал сброса синхронно. Для примера этот код иллюстрирует сгенерированный код Verilog для логики синхронизации сброса, когда вы генерируете ядро IP с синхронным сбросом.

...

...

reg_reset_pipe_process : PROCESS (clk)

BEGIN

IF clk'EVENT AND clk = '1' THEN

IF reset_in = '1' THEN

reset_pipe <= '1';

ELSIF enb = '1' THEN

reset_pipe <= const_0;

END IF;

END IF;

END PROCESS reg_reset_pipe_process;

reg_reset_delay_process : PROCESS (clk)

BEGIN

IF clk'EVENT AND clk = '1' THEN

IF reset_in = '1' THEN

reset_out <= '1';

ELSIF enb = '1' THEN

reset_out <= reset_pipe;

END IF;

END IF;

END PROCESS reg_reset_delay_process;

END rtl;