Когда вы открываете HDL Workflow Advisor и запускаете IP Core Generation рабочий процесс для вашего Simulink® модель, можно задать типовой Xilinx® платформа или типовая Intel® платформы. Затем рабочий процесс генерирует типовое IP-ядро, которое можно интегрировать в любую целевую платформу по своему выбору. Для IPцентрального интегрирования определите и зарегистрируйте пользовательский исходный проект для целевой платы при помощи hdlcoder.ReferenceDesign класс. Для получения дополнительной информации см.:

Чтобы сгенерировать независимое от платы пользовательское IP-ядро для использования в встраиваемой системе интегрирования окружения, таких как Intel Qsys, Xilinx EDK или Xilinx IP Integrator:

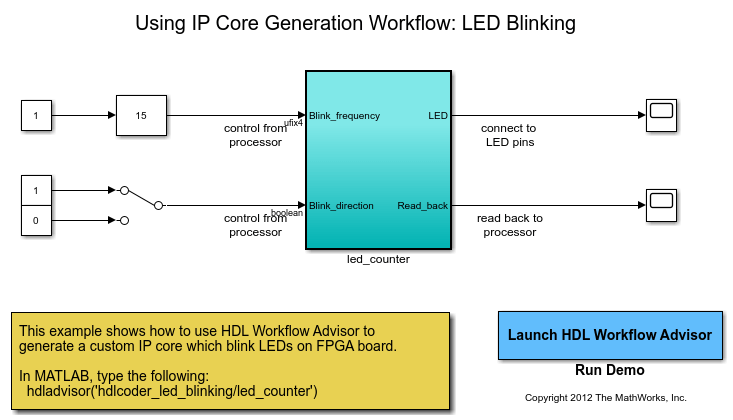

Выберите DUT в модели Simulink и откройте HDL Workflow Advisor. Для примера откройте модель hdlcoder_led_blinking.

open_system('hdlcoder_led_blinking')

Установите путь к установленному инструменту синтеза для целевого устройства при помощи hdlsetuptoolpath функция. Для примера, если Xilinx Vivado® - инструмент синтеза, используйте команду:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2018.2\bin\vivado.bat');

Последнюю поддерживаемую версию средства синтеза см. в разделах Поддержка языка HDL и Поддерживать Сторонних программах и оборудование.

Откройте HDL Workflow Advisor для подсистемы DUT. Для модели LED-мигания, led_counter Подсистема является DUT. В задаче Set Target > Set Target Device and Synthesis Tool:

Для Target workflow выберите IP Core Generation.

Для Target platform, в зависимости от инструмента синтеза и устройства, на которое вы нацелены, выберите Generic Altera Platform или Generic Xilinx Platform. Нажмите Run This Task.

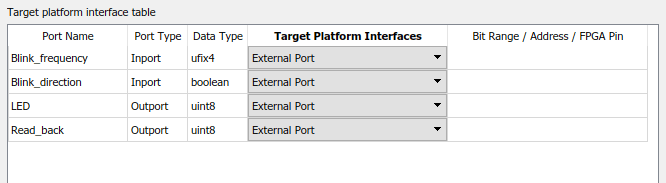

В задаче Set Target > Set Target Interface выберите Target Platform Interface для каждого порта и нажмите Apply. Вы можете сопоставить каждый порт DUT с одним из следующих интерфейсов: AXI4-Lite, AXI4, AXI4-Stream, AXI4-Stream Video, External Port, или FPGA Data Capture - JTAG. Дополнительные сведения об этих интерфейсах см. в разделе Интерфейсы целевой платформы.

Можно также сопоставить порты с несколькими целевыми интерфейсами платформы. Дополнительные сведения см. в разделе Генерация IP-ядра HDL с несколькими AXI4-Stream и AXI4 главными интерфейсами.

Если вы не хотите сопоставлять порты DUT с AXI4 ведомыми интерфейсами, можно сопоставить их с External Port интерфейсов.

Разверните Set Code Generation Options задачу. Щелкните правой кнопкой мыши Set Optimization Options задачу и выберите Run to Selected Task.

В задаче HDL Code Generation > Generate RTL Code and IP Core можно задать:

Хотите ли вы подключить ядро IP DUT к нескольким интерфейсам AXI Master. По умолчанию AXI4 Slave ID Width значение 12, что позволяет подключить HDL-ядро IP к одному интерфейсу AXI Master. Для подключения IP-ядра DUT к нескольким интерфейсам AXI Master можно увеличить AXI4 Slave ID Width. Когда вы запускаете эту задачу, эта политика сохраняется в DUT как AXI4SlaveIDWidth свойства блока.

Дополнительные сведения см. в разделе «Определение нескольких основных интерфейсов AXI в исходных проектах» для доступа к интерфейсам DUT AXI4 Slave.

Хотите ли вы сгенерировать интерфейс по умолчанию AXI4 slave. По умолчанию HDL- Coder™ генерирует AXI4 подчиненных интерфейсов для таких сигналов, как часы, сброс, готовность, временная метка и так далее. Если вы не хотите генерировать какие-либо AXI4 подчиненные интерфейсы, снимите флажок Generate default AXI4 slave interface.

Примечание

Если вы сопоставили любой из портов DUT с AXI4 ведомыми интерфейсами в Set Target Interface задаче, генератор кода сопоставляет порты с AXI4 ведомыми интерфейсами, независимо от того, снят ли флажок Generate default AXI4 slave interface.

Нажмите Run This Task. Когда вы снимаете флажок и запускаете задачу, генератор кода сохраняет эту настройку в Подсистеме DUT как GenerateDefaultAXI4Slave свойства блоков.

После выполнения задачи HDL Coder генерирует файлы ядра IP в папке выхода, показанной на IP core folder поле, включая документацию HTML. Чтобы просмотреть отчет ядра IP, щелкните ссылку в окне сообщения.

Когда вы запускаете IP Core Generation рабочий процесс, вы также можете сгенерировать HDL IP ядро без каких-либо AXI4 ведомых интерфейсов в вашем исходном проекте.

Чтобы запустить этот рабочий процесс, откройте HDL Workflow Advisor, задайте Generic Xilinx Platform или Generic Altera Platform в качестве целевой платформы и сопоставить порты DUT только внешнему порту или AXI4-Stream интерфейсу с отображением TLAST. В сложение, когда вы генерируете HDL-ядро IP, в Generate RTL Code and IP Core задаче снимите флажок Generate default AXI4 slave interface, а затем выберите Запуск Эта задача.

Используйте эту возможность, когда:

Вы не хотите настраивать параметры ядра IP с помощью AXI4 ведомых интерфейсов.

Вы хотите создать пользовательский исходный проект без AXI4 ведомых интерфейсов, таких как автономные платы FPGA.

В сложение, избегание генерации AXI4 ведомых интерфейсов в таких случаях уменьшает использование оборудования ресурсов и проекта сложность.

Примечание

Внешние интерфейсы ввода-вывода и внутренние интерфейсы ввода-вывода соединяют IP-ядро HDL с другими существующими IP-адресами в пользовательских исходных проектах. Чтобы определить эти интерфейсы, вы используете addInternalIOInterface и addExternalIOInterface методы hdlcoder.ReferenceDesign класс.

Чтобы интегрировать HDL-ядро IP, можно создать пользовательский исходный проект без AXI4 ведомых интерфейсов. В пользовательском исходном проекте можно использовать только внешний ввод-вывод, внутренний ввод-вывод или AXI4-Stream интерфейс с отображением TLAST. Для примеров смотрите:

Когда вы генерируете ядро IP HDL без AXI4 ведомых интерфейсов, применяются определенные ограничения. Смотрите IP-ядро без ограничений AXI4 ведомых интерфейсов.

DUT должен быть атомарной системой.

Одно и то же IP-ядро не может использовать и AXI4 интерфейс, и AXI4-Lite интерфейс.

DUT не может содержать блоки Xilinx System Generator или блоки Intel DSP Builder Advanced.

Если ваш целевой язык является VHDL®, и ваш инструмент синтеза Xilinx ISE или Intel Quartus Prime, DUT не может содержать модель-ссылку.

Входной и выходной порты должны иметь битовую ширину, меньшую или равную 32 битам.

Входной и выходной порты должны быть скалярными.

Порты должны иметь 32-разрядную ширину.

Порты должны быть скалярными.

Вы можете иметь не более одного входного видеопорта и одного выходного видеопорта.

Интерфейс AXI4-Stream Video не поддерживается в Coprocessing – blocking режим. Processor/FPGA synchronization должно быть установлено в Free running режим.

Можно сопоставить порты только с интерфейсами внешнего/внутреннего ввода-вывода или AXI4-Stream интерфейсом с отображением TLAST. Другие интерфейсы, требующие AXI4 подчиненных интерфейсов, такие как AXI4 Master, AXI4-Stream и AXI4-Stream Video, не поддерживаются.

Вы должны использовать Free running режим для Processor/FPGA synchronization. Coprocessing – blocking режим не поддерживается.