Для целевых платформ, поддерживающих IP Core Generation рабочий процесс с Xilinx® Vivado®можно использовать кэширование IP. IP-кэширование сокращает время синтеза исходных проектов, которые имеют много IP-модулей или имеют IP-модули со значительным временем синтеза запуска. Когда вы включаете кэширование IP, проект Vivado использует вне контекста (OOC) рабочий процесс. Этот рабочий процесс синтезирует IP-адрес в исходный проект вне контекста из проекта верхнего уровня. Рабочий процесс OOC ускоряет запуски проекта, поскольку инструмент синтеза повторно использует кэш и не должен повторно синтезировать IP при запуске рабочего процесса.

Если вы не включите IP-кэширование, по умолчанию проект Vivado использует глобальный поток синтеза. Этот поток синтезирует IP-модули в исходный проект вместе с дизайном верхнего уровня. В последующих запусках проекта этот рабочий процесс повторно синтезирует IP-модули в исходный проект.

Target workflow:

IP Core Generation

Simulink Real-Time FPGA I/O для плат Speedgoat, которые используют Xilinx Vivado

Synthesis tool: Xilinx Vivado

IP- кэша является папкой, которая состоит из подпапок, соответствующих IP-модулям в исходный проект. Каждая подпапка организована хеш- индекс, которая соответствует имени файла. Для каждого IP-модуля подпапка состоит из файлов Xilinx Core Instance (XCI), файлов Design Checkpoint (DCP) и файлов журнала синтеза. DCP является файлом контейнера, который содержит синтезированные списки сетей, файлы заглушки черного ящика HDL и ограничения выходного синхроимпульса.

Чтобы повторно использовать IP- кэша при запуске рабочего процесса, синтез IP должен соответствовать хеш- индекс в IP- кэша. Соответствие хеш- индекс соответствует удару по IP- кэша. Чтобы поразить IP- кэша в последующих запусках, используйте то же самое:

Настройки части, языка и целевой платформы

Исходный проект

Целевая частота

hdl_prj папка при создании IP- кэша

Когда вы включаете кэширование IP, проект Xilinx Vivado использует внеконтекстовый рабочий процесс (OOC). Проект OOC является рабочим процессом снизу вверх, который:

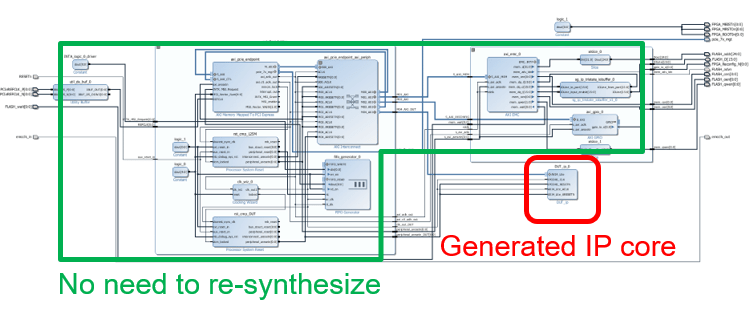

Синтезирует IP-модули в исходный проект отдельно от проекта верхнего уровня. Синтез- выход является файлом Проекта Контрольной точки (DCP).

Синтезирует дизайн верхнего уровня при обработке IP в исходный проект как черного ящика с помощью HDL-заглушки файлов поставляемой с DCP.

Реализует ваш проект на целевом устройстве путем связывания списков сетей из файлов контрольных точек IP-проекта с вашим списком сетей верхнего уровня.

Для больших исходных проектов поток OOC улучшает время запуска синтеза, потому что вы не должны ресинтезировать IP, когда вы изменяете проект и запускаете рабочий процесс. Дополнительные сведения о рабочем процессе OOC и опциях синтеза IP см. в документации Xilinx.

Прежде чем включать кэширование IP, задайте IP Core Generation в качестве целевого рабочего процесса, а затем укажите настройки целевой платформы. Чтобы включить кэширование IP-адресов:

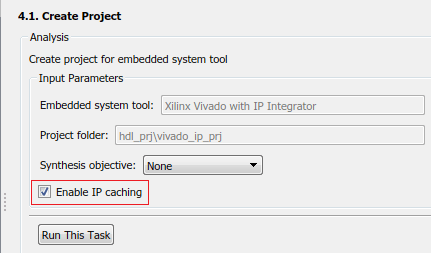

В HDL Workflow Advisor в Create Project задаче установите флажок Enable IP caching.

Из командной строки используйте EnableIPCaching свойство hdlcoder.WorkflowConfig класс. Чтобы использовать это свойство, создайте объект hdlcoder.WorkflowConfig Класс или экспорт настройки HDL Workflow Advisor в скрипт.

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx Vivado','TargetWorkflow','IP Core Generation'); % ... % ... hWC.EnableIPCaching = true;

Используйте IP-кэширование для больших исходных проектов, которые имеют значительное время синтеза. Например, исходный проект HDL Coder™ Default video system (requires HDMI FMC module) является потенциальным кандидатом для кэширования IP.

Примечание

The Speedgoat IO333-325K плата, которую вы используете с Simulink Real-Time FPGA I/O рабочий процесс поставляется с IP- кэша. В первый раз, когда вы запускаете рабочий процесс, генератор кода повторно использует этот IP- кэша, который улучшает время синтеза исходного проекта.

Чтобы включить кэширование IP-адресов, в HDL Workflow Advisor задайте IP Core Generation в качестве целевого рабочего процесса, а затем укажите настройки целевой платформы. Прежде чем вы запустите рабочий процесс в первый раз:

В Create Project задаче установите флажок Enable IP caching.

Когда вы запускаете эту задачу, рабочий процесс создает пустую папку кэша IP. Вы можете увидеть ipcache папка в hdl_prj/vivado_ip_prj путь.

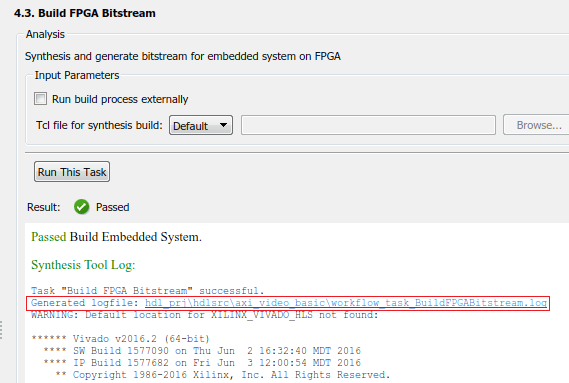

Запустите Build FPGA Bitstream задачу.

Эта задача заполняет папку кэша IP журналами синтеза и проектирует файлы контрольных точек, сгенерированные для ядра IP HDL и других блоков IP в исходном проекте. Когда эта задача успешно запущена, вы можете увидеть сгенерированные файлы в ipcache папка.

Когда вы запускаете IP Core Generation рабочий процесс второй раз, в Build FPGA Bitstream задаче можно увидеть улучшение во времени запуска задачи. Убедитесь, что вы используете одни и те же настройки IP и hdl_prj папка как первый раз, когда вы запускали рабочий процесс. Когда эта задача будет успешно запущена, чтобы увидеть, повторно ли ваш рабочий процесс использовал кэш, откройте workflow_task_buildFPGABitstream.log файл.

Этот фрагмент кода показывает, что проект Vivado запускает максимальное количество заданий, чтобы синтезировать проект и повторно использовать IP-модули в папке кэша IP. Вы можете увидеть, что cacheID IP-модулей совпадают с именами файлов подпапок в ipcache папка.

... # reset_run impl_1 # reset_run synth_1 # launch_runs -jobs 4 synth_1 ... ... ... INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_RGBtoYCbCr_0_0, cacheID = 3575924730488800 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_YCbCrtoRGB_0_0, cacheID = e71459f41e26e141 INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_xbar_0, cacheID = d0f0971cb77bcaed INFO: [IP_Flow 19-4760] Using cached IP synthesis design for IP system_top_axis2hdmi_0_0, cacheID = 7601a322f9fd0ec4 ...

Если вы используете свои собственные пользовательские исходные проекты, кэширование IP-адресов может ускорить синтез исходного проекта при первом запуске рабочего процесса. Чтобы повторно использовать кэш IP, создайте zip-файл кэша IP, а затем убедитесь, что файл определения исходного проекта указывает на этот zip-файл.

Чтобы создать IP- кэша zip файла:

Откройте HDL Workflow Advisor для любого Simulink® модель, которая имеет подсистему DUT, а затем запускает рабочий процесс IP Core Generation к Generate RTL Code and IP Core задаче.

В Create Project задаче установите флажок Enable IP caching и нажмите Run This Task. Эта задача создает пустую папку кэша.

Запустите рабочий процесс к Build FPGA Bitstream задаче. Эта задача заполняет IP- кэша ядром HDL и исходного проекта модулями IP.

В папке кэша удалите файлы ядра IP, сгенерированные для DUT. Извлеките оставшиеся файлы из этой папки в zip-файл, назовите его ipcache.zip, а затем сохраните файл в папке исходного проекта.

Чтобы повторно использовать IP- кэша, в файле определения исходного проекта plugin_rd.m, используйте IPCacheZipFile свойство hdlcoder.ReferenceDesign класс. Используя это свойство, вы добавляете ipcache.zip файл к проекту Xilinx Vivado.

function hRD = plugin_rd() % Reference design definition hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); % ... % ... hRD.IPCacheZipFile = 'ipcache.zip';

hdlcoder.Board | hdlcoder.ReferenceDesign