Кодер поддерживает генерацию Simulink® Блоки косимуляции HDL. Можно использовать сгенерированные блоки HDL Cosimulation для косимуляции создания фильтра с помощью Simulink с Симулятором HDL. Для использования этой функции необходимо иметь лицензию HDL- Verifier™.

Сгенерированные блоки HDL Cosimulation сконфигурированы так, чтобы соответствовать интерфейсу порта и типа данных фильтра, выбранного для генерации кода. Соединяя блок HDL Cosimulation с моделью Simulink вместо фильтра, можно косимулировать свой проект с помощью нужных Симуляторов HDL.

Чтобы сгенерировать блоки HDL-косимуляции:

Выберите панель Test Bench в диалоговом окне Генерация HDL.

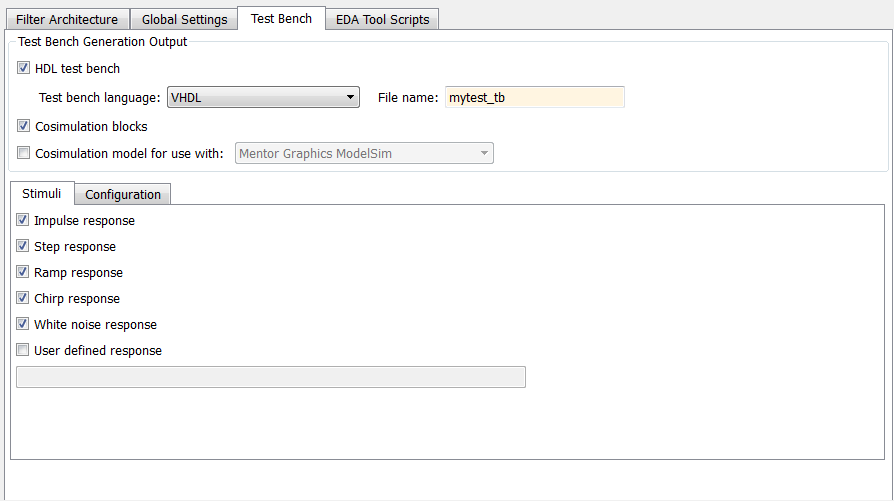

Выберите опцию Cosimulation blocks.

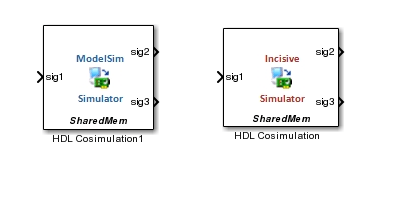

Когда эта опция выбрана, кодер генерирует и открывает модель Simulink, которая содержит блок HDL Cosimulation для каждого поддерживаемого Симулятора HDL.

Если вы хотите сгенерировать только блоки HDL Cosimulation (не генерируя HDL- испытательного стенда код), очистите HDL test bench.

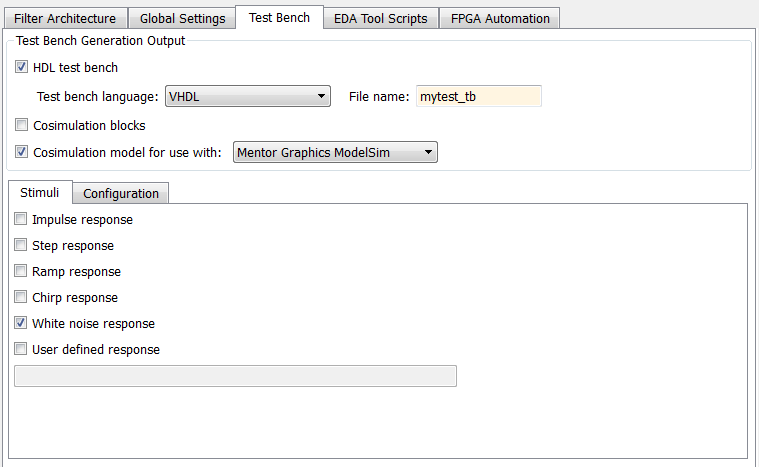

Следующий рисунок показывает HDL test bench и Cosimulation blocks выбранные.

В диалоговом окне «Генерация HDL» нажмите кнопку Generate, чтобы сгенерировать HDL и испытательный стенд.

В сложение к обычным файлам кода кодер генерирует модель Simulink, содержащую блок HDL Cosimulation для каждого Симулятора HDL, поддерживаемого HDL Verifier.

Сгенерированная модель без названия и существует только в памяти. Обязательно сохраните его в целевой папке, если хотите сохранить модель и блоки для использования в будущих сеансах.

Для настройки параметров блоков HDL Cosimulation, таких как время, задержка и типы данных, смотрите Define HDL Cosimulation Block Interface (HDL Verifier).

Альтернатива командной строки: используйте generatehdl функция со свойством GenerateCosimBlock для генерации блоков HDL-косимуляции.

Примечание

Для использования этой функции необходимо иметь лицензию HDL Verifier.

Кодер генерирует модель Simulink, которая запускает симуляцию Simulink вашего создания фильтра, а также косимуляцию вашего проекта с Симулятором HDL. Модель сравнивает выходы фильтра Simulink с результатами симуляции HDL.

Сгенерированная модель включает в себя:

Поведенческая модель создания фильтра, реализованная в подсистеме Simulink. Подсистема реализует создание фильтра, используя основные блоки, такие как сумматоры и задержки.

Соответствующий блок HDL-косимуляции. Кодер конфигурирует этот блок, чтобы косимулировать создание фильтра с помощью Simulink с одним из следующих:

Менторская графика® ModelSim®

Каденция Incisive®

Тестовые воздействия, рассчитанные из указанного вами стимула испытательного стенда. Кодер сохраняет тестовые данные в переменном рабочем пространстве модели inputdata. Блок From Workspace направляет тестовые данные в подсистему фильтра и блоки HDL Cosimulation.

Блок Scope, который позволяет вам наблюдать и сравнивать сигнал тестового воздействия с выходами блока Filter и HDL-косимуляции. Область возможностей также показывает различие (ошибку) между этими двумя выходами.

Генерация модели косимуляции требует зарегистрированных входных и/или выходов (см. Ограничения). Прежде чем генерировать модель, убедитесь, что ваша модель соответствует этому требованию, следующим образом:

Выберите панель Global Settings диалогового окна Генерация HDL.

На панели Global Settings перейдите на вкладку Ports. Появляются опции порта.

Выберите обе из следующих опций:

Add input register

Add output register

Чтобы сгенерировать модель:

В диалоговом окне Generate HDL сконфигурируйте другие параметры генерации кода и испытательного стенда в соответствии с требованиями вашего проекта.

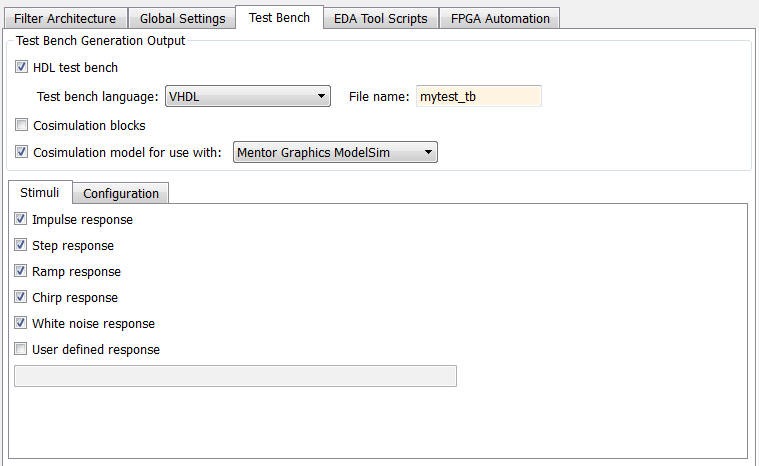

Выберите панель Test bench диалогового окна Генерация HDL.

Выберите опцию Cosimulation model for use with:. Выбор этой опции включает соседнее раскрывающееся меню, где можно выбрать Mentor Graphics ModelSim или Cadence Incisive.

Используя раскрывающееся меню, выберите тип блока HDL Cosimulation, который необходимо использовать в сгенерированной модели. Выберите один из Mentor Graphics ModelSim (по умолчанию) или Cadence Incisive.

На следующем рисунке тип модели косимуляции Mentor Graphics ModelSim, и сигнал стимула White noise response.

В диалоговом окне «Генерация HDL» нажмите кнопку Generate, чтобы сгенерировать HDL и испытательный стенд.

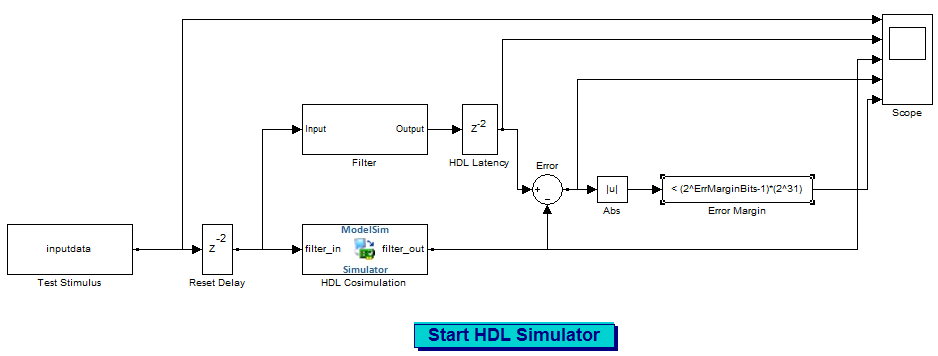

В дополнение к обычным файлам кода кодер генерирует и открывает модель Simulink. Следующий рисунок показывает модель, сгенерированную из строения кодера, показанной на предыдущем шаге.

Сгенерированная модель без названия и существует только в памяти. Обязательно сохраните его в целевой папке, если хотите сохранить модель и блоки для использования в будущих сеансах.

Для настройки параметров блоков HDL Cosimulation, таких как время, задержка и типы данных, смотрите Define HDL Cosimulation Block Interface (HDL Verifier).

Сгенерированная модель содержит следующие блоки:

Test Stimulus: Это From Workspace блока маршруты тестовых данных в переменном рабочем пространстве модели inputdata в подсистему фильтра и блоки HDL Cosimulation.

Filter: Эта подсистема реализует поведенческую модель создания фильтра.

HDL Cosimulation: Этот блок косимулирует сгенерированный HDL-код. Таблица HDL Параметры блока косимуляции описывает, как кодер конфигурирует параметры блоков косимуляции.

Reset Delay: Команды Tcl, заданные в HDL Cosimulation блок применить сигнал сброса. Сброс высокий на 0 нс и низкий на 22 нс (перед третьим поднимающимся ребром синхроимпульса). Симуляция Simulink начинает подавать вход с 0, 10, 20 нс. Reset Delay блок добавляет задержку, так что первая выборка доступна для симуляции RTL, когда она готова после применения сброса.

HDL Latency: Эта задержка представляет различие между задержкой симуляции RTL и поведенческим блоком Simulink.

Error: Вычисляет различие между выходами Filter блок и HDL Cosimulation блок.

Abs: Абсолютное значение расчета ошибки.

Error margin:: Индикатор сравнения абсолютного значения ошибки с испытательным стендом значением запаса ошибки (см. «Установка запаса ошибки для оптимизированного кода фильтра»).

Scope: Отображает входной сигнал, выходы от Filter блок и HDL Cosimulation блоки и различие (если она существует) между ними.

Start HDL Simulator кнопка: Запускает программное обеспечение для косимуляции HDL.

Настройки блоков косимуляции HDL

| Панель | Настройки |

|---|---|

Ports | Имена портов: те же, что и имена в сгенерированном коде для фильтра. Типы данных ввода/вывода: Входной шаг расчета: Выходной шаг расчета: Тот же, что и Simulink фиксированный размер шага. |

Clocks | Имя порта синхроимпорта: то же, что и имя в сгенерированном коде для фильтра. Активное ребро синхроимпульса: Период: тот же, что и шаг расчета Simulink. |

Timescales | 1 секунда в Simulink соответствует 1 такту в симуляторе HDL |

Connection | Режим подключения: Метод соединения: |

Tcl (Команды предварительной симуляции) | force /Hlp/clk_enable 1; force /Hlp/reset 1 0 ns, 0 22 ns; puts ----------------------------------------- puts "Running Simulink Cosimulation block."; puts [clock format [clock seconds]] |

Tcl (Постсимуляции) | force /Hlp/reset 1 puts [clock format [clock seconds]] |

Сгенерированные настройки модели. Сгенерированная модель имеет следующие настройки без ограничений:

Solver: Discrete (no continuous states).

Type решателя: Fixed-step.

Stop Time: Ts * StimLen, где Ts - это шаг расчета и StimLen Simulink - длина стимула.

Sample Time Colors: включено

Port Data Types: включено

Hardware Implementation: ASIC/FPGA

Косимуляция, которая запускается, не сталкиваясь с ошибками, требует, чтобы выходы из сгенерированного HDL-кода были синхронными с часами. Перед генерацией кода убедитесь, что выбраны обе из следующих опций:

Add input register

Add output register

Если вы не выбираете одну из этих опций, кодер завершает генерацию модели с ошибкой. Однако генерация испытательного стенда кода завершена.

Кодер не поддерживает генерацию модели косимуляции, когда целевой язык является Verilog, и генерируются данные типа double.

Используйте generatehdl function, передающая одно из следующих значений для свойства GenerateCosimModel.

generatehdl(filtSysObj,'InputDataType',numerictype(1,16,15), ... 'GenerateCosimModel','Incisive');

generatehdl(filtSysObj,'InputDataType',numerictype(1,16,15), ... 'GenerateCosimModel','ModelSim');