Можно создать часы нарастающего или падающего края, сбросы или сигналы включения синхроимпульса, которые применяют внутренние раздражители к вашей модели под косимуляцией. Вы можете добавить эти сигналы:

Создание необязательных часов с панелью часов блока косимуляции HDL

Реализация этих сигналов непосредственно в HDL-коде. Если ваша модель является частью намного большей HDL- проекта, вы (или более крупный дизайнер моделей) можете принять решение реализовать эти сигналы в Verilog® или VHDL® файлы. Однако эта реализация превышает возможности этой документации; для получения дополнительной информации см. ссылку на HDL.

Добавьте часы нарастающего или падающего края, сбросы или сигналы включения синхроимпульса к Simulink® моделировать с использованием блоков Simulink. Смотрите Руководство пользователя Simulink и Ссылки для получения инструкций по добавлению блоков к модели.

В следующем примере выписки затененная область показывает часы, сброс и сигнал включения синхроимпульса в качестве входа в модель с несколькими HDL Cosimulation блоками. Эти сигналы создаются с использованием двух блоков преобразования типа данных Simulink и постоянного исходного блока, которые соединяются с блоком HDL Cosimulation, помеченным как «Подсистема приемника манчестерского кода».

Примечание

Для ModelSim® и резьбовое® Только пользователи

Когда вы задаете часы в определении блока, Simulink создает часы с приподнимающим или падающим фронтом, которые управляют указанным HDL-сигналом.

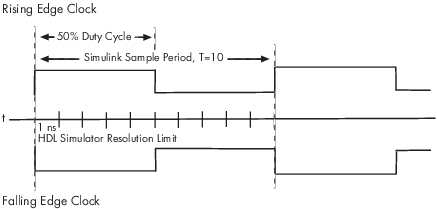

Simulink пытается создать часы, которые имеют 50% коэффициент заполнения и предопределенную фазу, которая инвертируется для случая падающего ребра. Если применимо, Simulink ухудшает коэффициент заполнения, чтобы учесть нечетные шаги расчета Simulink с наихудшим случаем коэффициента заполнения 66% для шага расчета T=3.

Независимо от того, сконфигурировали ли вы панель Timescales для относительного режима синхронизации или абсолютного режима синхронизации, к тактовым периодам применяются следующие ограничения:

Если вы задаете явный период времени, необходимо ввести шаг расчета, равное или больше 2 единиц разрешения ( такта).

Если период времени (явным образом заданный или по умолчанию) не является четным целым числом, Simulink не может создать 50% коэффициент заполнения, и поэтому программное обеспечение HDL Verifier™ создает падающее ребро в

(округлено до ближайшего целого числа).

Для получения дополнительной информации о вычислении относительных и абсолютных режимов синхронизации, смотрите Определение отношений синхронизации Simulink и Симулятор HDL.

Следующий рисунок показывает временную диаграмму, которая включает часы повышения и падения ребра с шагом расчета Simulink T=10 и предел разрешения симулятора HDL, равный 1 нс. Рисунок также показывает, что, учитывая эти параметры синхронизации, коэффициент заполнения синхроимпульса составляет 50%.

Чтобы создать часы, выполните следующие шаги:

В симуляторе HDL определите имена путей синхросигнала, которые вы планируете задать в своем блоке. Для этого можно использовать тот же метод, объясненный для определения имен пути сигнала для портов на шаге 1 «Map HDL Signals to Block Ports».

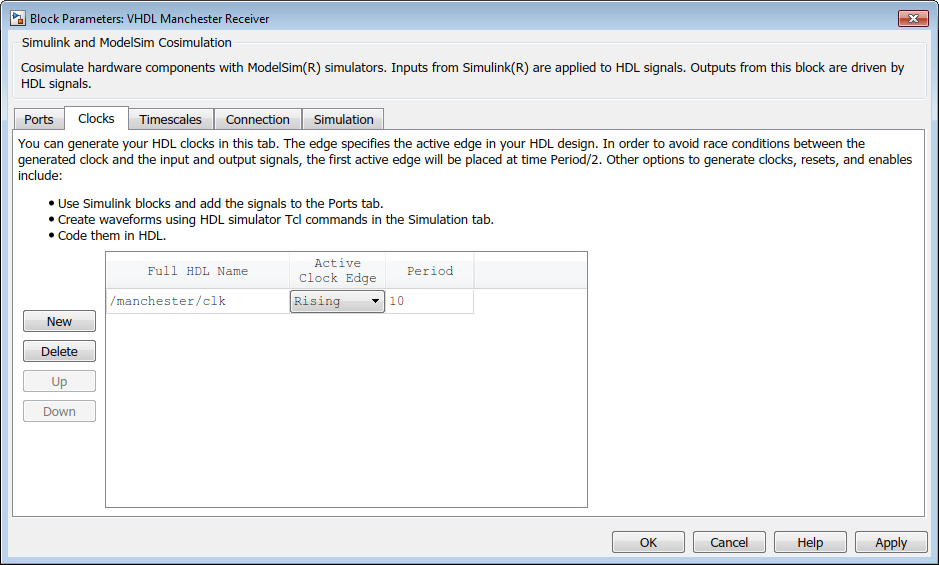

Выберите вкладку Clocks диалогового окна Параметров блоков. Simulink отображает диалоговое окно как показано на следующем рисунке (пример показан для использования с Incisive).

Нажмите New, чтобы добавить новый синхросигнал.

Отредактируйте имя пути синхросигнала непосредственно в таблице под столбцом Full HDL Name, дважды кликнув имя синхросигнала по умолчанию (/top/clk). Затем укажите свои новые часы, используя синтаксис Симулятора HDL пути. Смотрите Specify HDL Signal/Port and Module Path для Simulink Test Bench Cosimulation.

Симулятор HDL не поддерживает векторные сигналы в панели Clocks. Сигналы должны быть логическими типами с 1 и 0 значениями.

Чтобы указать, генерирует ли синхроимпульс сигнал нарастающего или падающего ребра, выберите Rising или Falling из списка Active Clock Edge.

Поле Period задает тактовый период. Примите значение по умолчанию (2), или переопределите его путем явного ввода необходимого тактового периода двойным щелчком мыши в поле Period.

Задайте Period поле как четное целое число с минимальным значением 2.

Когда вы закончите редактировать синхросигналы, нажмите Apply, чтобы зарегистрировать изменения в Simulink.

Следующее диалоговое окно задает часы приподнимающего края clk для блока HDL Cosimulation с периодом по умолчанию 2 (пример показан для использования с Incisive).

Можно вращать часы, сбрасывать и включать сигналы любым из двух способов:

Путем добавления команд силы к панели Simulation (только для пользователей ModelSim и Incisive)

По управляемым сигналам с одной из команд запуска HDL-симулятора HDL Verifier (vsim или nclaunch) и команду force

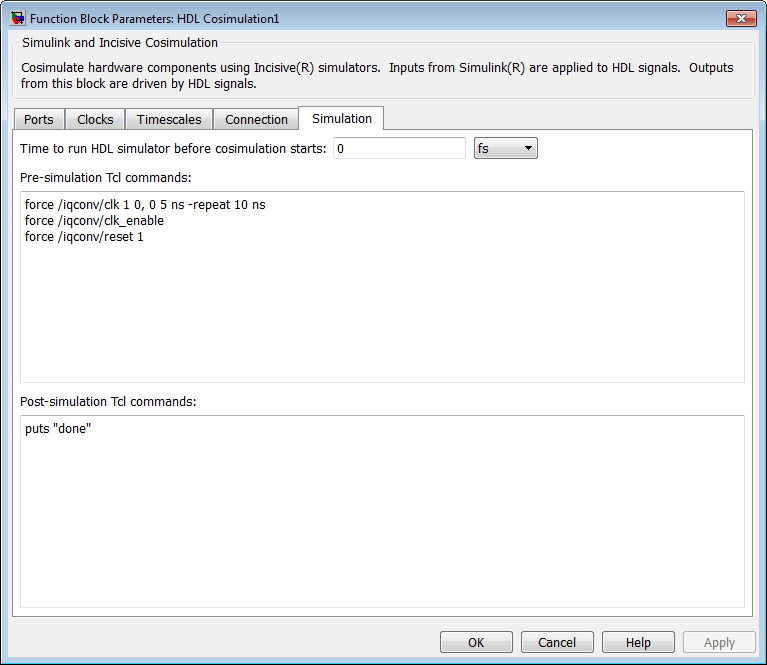

Следующий пример является примером ввода команд силы в панели Simulation блока HDL Cosimulation для использования с Incisive:

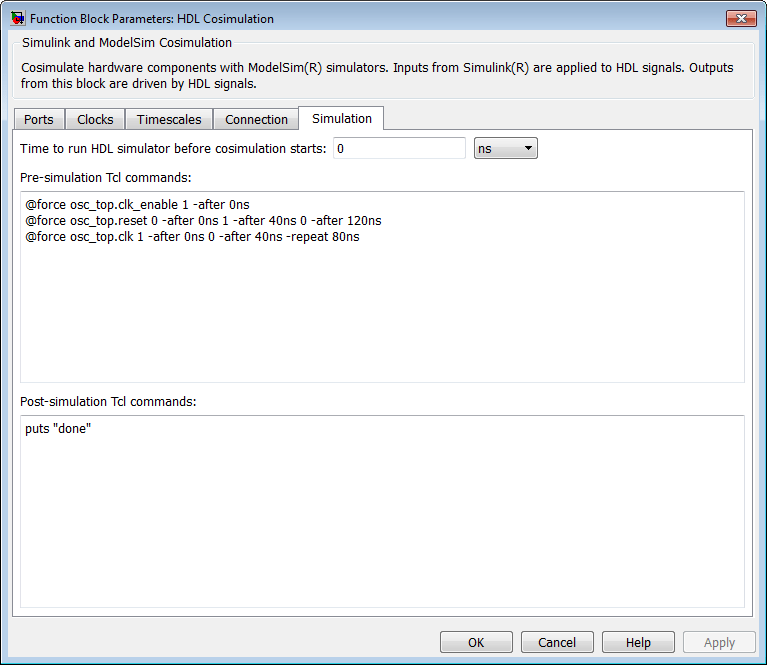

Следующий пример является примером ввода команд силы в панели Simulation блока HDL Cosimulation для использования с ModelSim:

vsim function and force command (пользователи ModelSim):

vsim('tclstart', {'force /iqconv/clk 1 0, 0 5 ns -repeat 10 ns ',

'force /iqconv/clk_enable 1', 'force /iqconv/reset 1'});nclaunch function and force command (Incisive users):

nclaunch('tclstart',['-input "{@force osc_top.clk_enable 1 -after 0ns}"',

'-input "{@force osc_top.reset 0 -after 0ns 1 -after 40ns 0 -after 120ns}"',

'-input "{@force osc_top.clk 1 -after 0ns 0 -after 40ns -repeat 80ns}"']);