Эти шаги описывают, как косимулировать HDL- проекта с помощью Simulink® программное обеспечение как испытательный стенд.

Создайте тестовую модель Simulink путем добавления блоков Simulink из библиотек блоков Simulink. Запустите и протестируйте свою модель тщательно, прежде чем заменять или добавлять компоненты аппаратной модели в качестве блоков косимуляции.

Кодируйте HDL модуль. Компилируйте, разрабатывайте и симулируйте свой модуль в своем Симуляторе HDL. См. раздел «Код HDL- Компонента».

Запустите симулятор HDL для использования с MATLAB® и Simulink и загрузка HDL Verifier™ библиотек. Смотрите Start HDL Simulator для косимуляции в Simulink.

Добавьте блок HDL Cosimulation к своей тестовой модели Simulink. См. раздел «Вставка блока косимуляции HDL».

Задайте HDL Cosimulation интерфейс блока. См. «Конфигурирование интерфейса блока косимуляции HDL».

(Необязательно) Добавьте блок To VCD File, чтобы записать изменения в значения переменных во время сеанса симуляции. См. раздел «Добавление файла дампа изменений значений» (VCD).

Сначала запустите симуляцию в Симулятор HDL, затем запустите модель Simulink. См. «Запуск сеанса косимуляции Simulink».

Задайте режимы направления портов в HDL- Компонента для Испытательного стенда использования

Укажите типы данных портов в компоненте для использования в испытательном стенде

Компилируйте и разрабатывайте проект HDL для использования на испытательном стенде

Интерфейс HDL Verifier передает все данные между Симулятором HDL и Simulink как данные порта. Программное обеспечение HDL Verifier работает с любым существующим HDL-модулем. Однако, когда вы кодируете HDL-модуль, предназначенный для верификации Simulink, необходимо учитывать типы данных, которые будут использоваться совместно между двумя окружениями и режимами направления.

В операторе модуля необходимо задать каждый порт с режимом направления (вход, вывод или двунаправленный). Следующая таблица определяет эти три режима.

| Использование VHDL® Режим... | Использование Verilog® Режим... | Для портов, которые... |

|---|---|---|

IN | input | Представление сигналов, которые могут управляться функцией MATLAB |

OUT | output | Представление значений сигналов, которые передаются в функцию MATLAB |

INOUT | inout | Представление двунаправленных сигналов, которые могут управляться или передавать значения в функцию MATLAB |

В этом разделе описывается, как задать типы данных, совместимые с MATLAB для портов в модулях HDL. Дополнительные сведения о том, как интерфейс HDL Verifier преобразует типы данных для окружения MATLAB, см. в разделе Поддерживаемые типы данных.

Примечание

При использовании неподдерживаемых типов программа HDL Verifier выдает предупреждение и игнорирует порт во время выполнения. Например, если вы задаете свой интерфейс с пятью портами, один из которых является портом доступа VHDL, во время выполнения, то интерфейс выводит предупреждение и ваш код видит только четыре порта.

Инструкции по компиляции и разработке HDL- Симулятора HDL см. в проект документации.

После того, как вы кодируете один из компонентов вашей модели в VHDL или Verilog и моделируете его в Симулятор HDL окружения, интегрируйте представление HDL в модель Simulink как блок HDL Cosimulation путем выполнения следующих шагов:

Откройте свою модель Simulink, если она еще не открыта.

Удалите компонент модели, который должен заменить HDL Cosimulation блок.

В браузере библиотеки Simulink выберите библиотеку блоков HDL Verifier. Затем можно выбрать библиотеку блоков для поддерживаемых Симуляторов HDL. Выберите Mentor Graphics® ModelSim® HDL Cosimulation блок или Cadence Incisive® HDL Cosimulation блок, как показано ниже.

![]()

![]()

Скопируйте HDL Cosimulation блок из браузера библиотек в модель.

Соедините любые HDL Cosimulation блочные порты с применимыми блочными портами в вашей модели Simulink.

Чтобы смоделировать приемное устройство, сконфигурируйте блок только с входами.

Чтобы смоделировать исходное устройство, сконфигурируйте блок только с выходами.

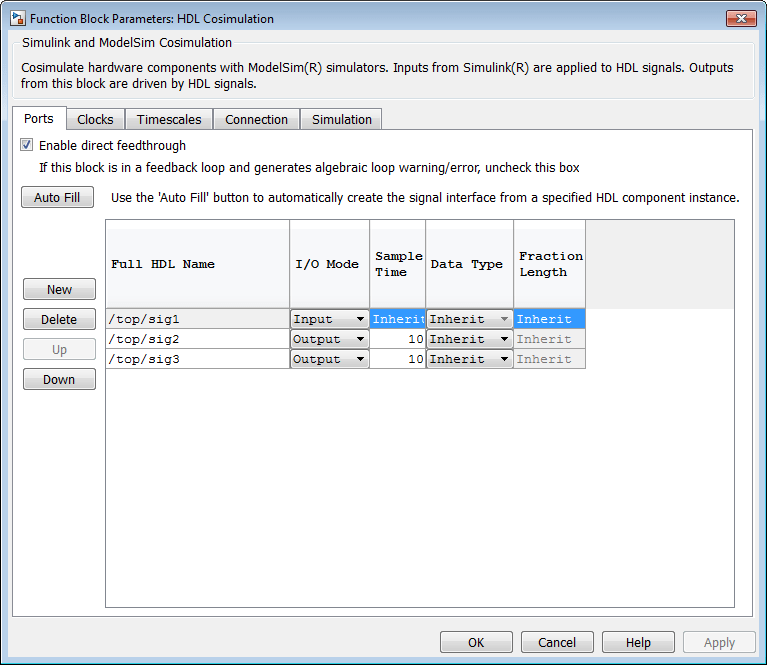

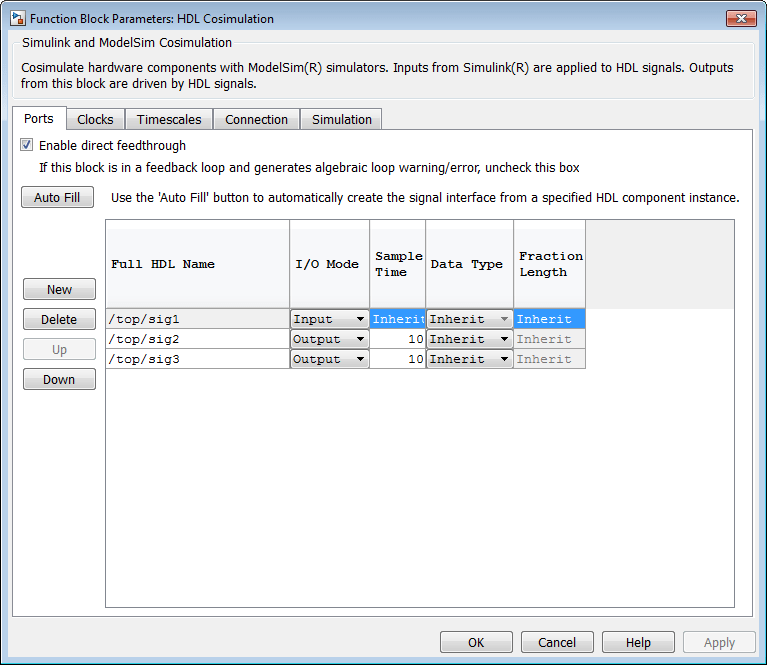

Чтобы открыть диалоговое окно параметров блоков для HDL Cosimulation блока, дважды кликните значок блока. Simulink отображает следующее Параметрам блоков диалоговое окно (в качестве примера, диалоговое окно для блока HDL Cosimulation для использования с ModelSim показано ниже).

Задайте пути HDL-сигнала/порта и модуля для Simulink Test косимуляции стенда

Управляйте Выход портом непосредственно по значению Input port

Первым шагом к настройке блока HDL Cosimulation HDL Verifier является сопоставление сигналов и образцов сигналов вашего HDL- проекта с определениями портов в вашем блоке HDL Cosimulation. В дополнение к идентификации входных и выходных портов, можно задать шаг расчета для каждого выходного порта. Можно также задать тип данных с фиксированной точкой для каждого выходного порта.

Сигналы, которые вы отображаете, могут быть на любом уровне иерархии проекта.

Для отображения сигналов можно выполнить одно из следующих действий:

Введите информацию о сигнале вручную в панель Ports диалогового окна параметров блоков. Этот подход может быть более эффективным, когда вы хотите подключить небольшое количество сигналов от вашего HDL- модели к Simulink.

Используйте кнопку Auto Fill, чтобы HDL Cosimulation блок получил информацию о сигнале для вас, передав запрос в Симулятор HDL. Этот подход может сэкономить значительные усилия, когда вы хотите косимулировать HDL-модель, которая имеет много сигналов, которые вы хотите соединить с вашей моделью Simulink. Однако в некоторых случаях вам нужно будет отредактировать данные сигнала, возвращенные запросом.

Примечание

Проверьте, что сигналы, используемые в косимуляции, имеют доступ для чтения/записи. Для более высокой эффективности вы хотите предоставить доступ только к тем сигналам, которые используются в косимуляции. Это правило применяется ко всем сигналам на Ports, Clocks и Simulation панелях, а также ко всем сигналам, добавленным любым другим способом.

Задайте пути HDL-сигнала/порта и модуля для Simulink Test косимуляции стенда. Эти правила относятся к спецификациям сигнала/порта и пути модуля в Simulink. Другие спецификации могут работать, но не поддерживаются явно или косвенно в этом или будущих релизах.

HDL- проектов обычно имеют иерархию; это является причиной этого синтаксиса. Эта спецификация не представляет иерархию имен файлов.

Спецификации пути для верхнего уровня Verilog

Спецификации пути для верхнего уровня Verilog

Спецификации пути для верхнего уровня VHDL

Спецификации пути для верхнего уровня VHDL

Получите информацию о сигнале от Симулятор HDL. Кнопка Auto Fill позволяет вам начать запрос Симулятора HDL и задать путь к компоненту или модулю в HDL- модели под симуляцией в Симулятор HDL. Как правило, после завершения запроса требуется некоторое изменение информации о порте. Для работы Симулятора HDL необходимо загрузить Auto Fill с HDL-модулем.

Следующий пример описывает необходимые шаги.

Примечание

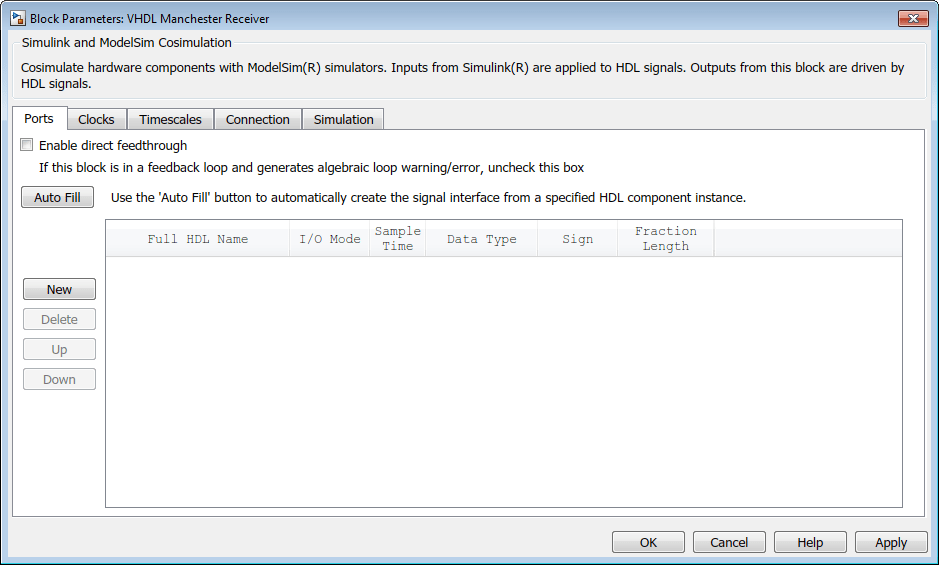

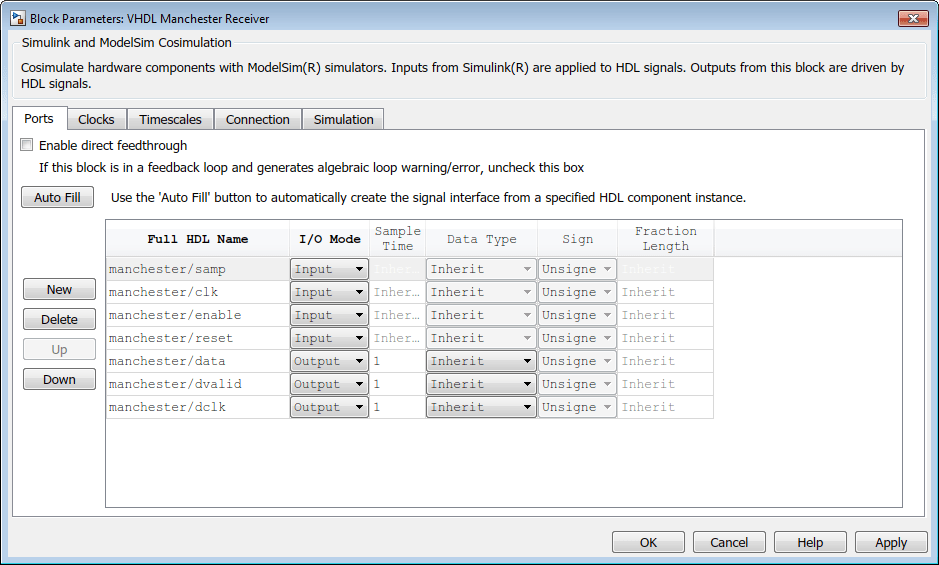

Пример основан на измененной копии модели Приемник Манчестерского Кода, в которой все сигналы были сначала удалены из панелей Ports и Clocks.

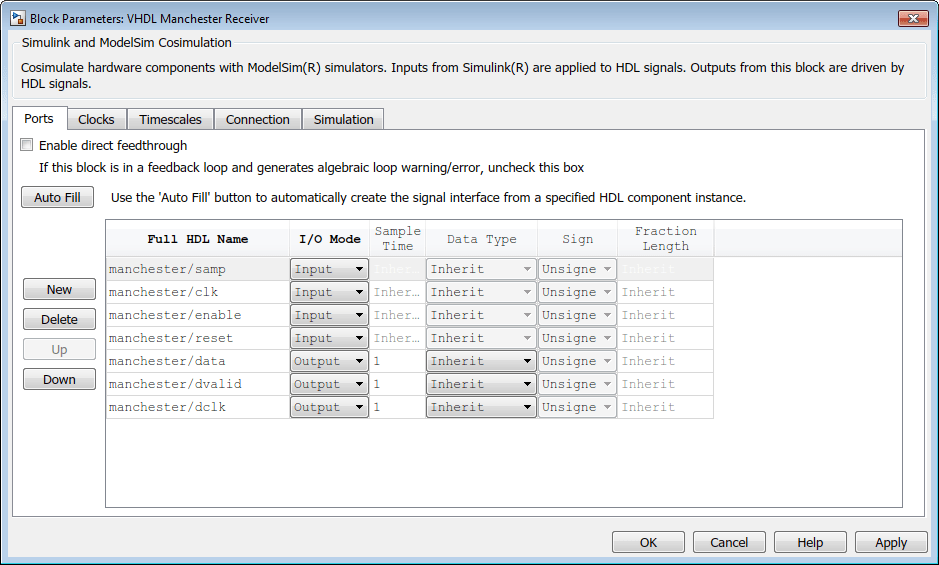

Откройте диалоговое окно параметров блоков для блока HDL Cosimulation. Перейдите на вкладку Ports. Откроется Ports панель (в качестве примера, панель Ports для блока HDL Cosimulation для использования с ModelSim показана на рисунках ниже).

Совет

Удалите все порты перед выполнением Auto Fill, чтобы убедиться, что неиспользованный сигнал не остается в списке Ports в любое время.

Нажмите кнопку Auto Fill. Откроется диалоговое окно Auto Fill.

Это модальное диалоговое окно запрашивает образец путь к компоненту или модулю в вашем HDL- модели; здесь вы вводите явный HDL- пути в поле редактирования. Путь, который вы вводите, не является файловым путем и не имеет никакого отношения к исходным файлам.

В этом примере функция автоматической заливки получает данные портов для компонента, называемого manchester. HDL- пути задается как /top/manchester. Пути спецификации будут варьироваться в зависимости от вашего Симулятора HDL, см. «Задание сигнала/порта HDL и Путей модуля» для Simulink косимуляции компонента.

Нажмите Fill, чтобы закрыть диалоговое окно, и запрос будет передан.

После того, как симулятор HDL вернет данные порта, функция автозаполнения вводит его в панель Ports, как показано на следующем рисунке (примеры показаны для использования с Cadence Incisive).

Щелкните Apply, чтобы зафиксировать сложения портов.

Удалите неиспользованные сигналы из панели Ports и добавьте сигнал Clock.

Предыдущий рисунок показывает, что запрос ввел порты clock, clock enable и reset (маркирован clk, enable, и reset соответственно) в список портов.

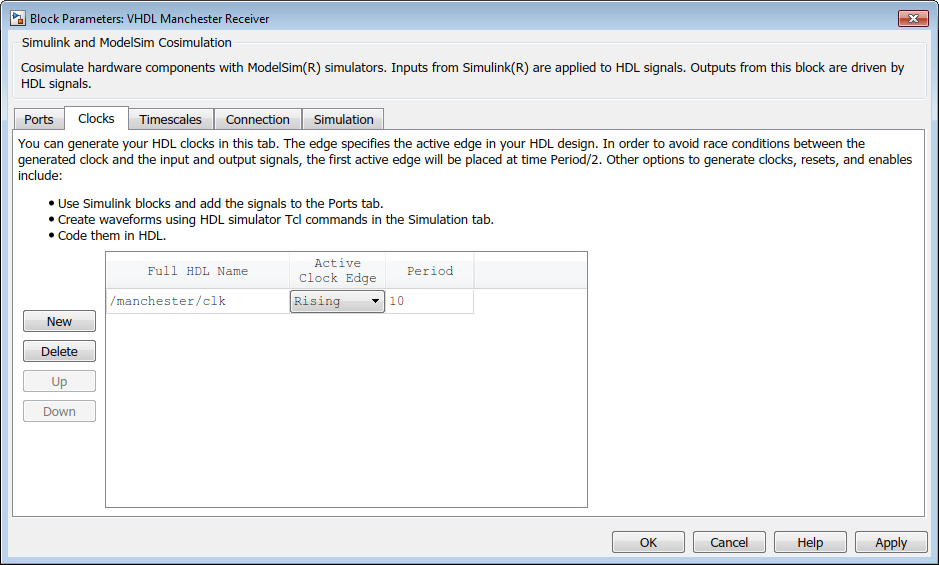

Удалите clk, enable и reset сигналы с панели Ports и добавить clk сигнал на панели Clocks.

Эти действия приводят к сигналам, показанным на следующих рисунках.

Auto Fill возвращает значения по умолчанию для выходных портов:

Sample time: 1

Data type: Inherit

Fraction length: Inherit

Вам, возможно, потребуется изменить эти значения по требованию вашей модели. В этом примере Sample time должно быть установлено на 10 для всех выходов. См. «Определение типов данных сигналов».

Прежде чем закрывать диалоговое окно параметров блоков, нажмите кнопку Apply, чтобы зафиксировать все внесенные изменения.

Заметьте, что Auto Fill возвращена информация обо всех входах и выходах для целевого компонента. Во многих случаях это будет включать сигналы, которые функционируют в симуляторе HDL, но не могут быть подключены в модели Simulink. Можно удалить все такие записи из списка на панели Ports, если они нежелательны. Можно управлять сигналами от Simulink; вы просто должны задать их значения путем сложения блоков Simulink.

Обратите внимание, что Auto Fill не возвращает информацию для внутренних сигналов. Если вашей модели Simulink нужен доступ к таким сигналам, вы должны ввести их в панель Ports вручную. Для примера в случае модели Приемника манчестерского кода необходимо добавить выход записи портов для top/manchester/sync_i, top/manchester/isum_i, и top/manchester/qsum_i, как показано на шаге 8.

Острый® и пользователи ModelSim: Обратите внимание, что clk, сброс и clk_enable могут находиться в панелях Clocks и Simulation, но они не должны быть. Эти сигналы могут быть портами, если вы решите вести их явно от Simulink.

Примечание

Когда вы импортируете VHDL-сигналы, используя Auto Fill, Симулятор HDL возвращает имена сигналов во всех столицах.

Введите информацию о сигнале вручную. Чтобы ввести информацию о сигнале непосредственно в панели Ports, выполните следующие шаги:

В симуляторе HDL определите имена пути сигнала для сигналов HDL, которые вы планируете задать в своем блоке. Для примера в симуляторе ModelSim следующее волновое окно показывает, что все сигналы подчинены модулю верхнего уровня manchester.

В Simulink откройте диалоговое окно параметров блоков для HDL Cosimulation блока, если он еще не открыт.

Перейдите на вкладку Ports панели. Simulink отображает следующее диалоговое окно (пример показан для использования с Incisive).

На этой панели вы задаете HDL-сигналы своего проекта, которые хотите включить в блок Simulink, и задаете шаг расчета и тип данных для выходных портов. Параметры, которые вы должны задать на панели Ports, зависят от типа устройства, которое блок моделирует следующим образом:

Для устройства, имеющего как входы, так и выходы: задайте входные порты блоков, выходные порты блоков, время вывода и типы выходных данных.

Для выходных портов примите значение по умолчанию или введите явный шаг расчета. Типы данных могут быть заданы явным образом или установлены на Inherit (значение по умолчанию). В случае по умолчанию тип данных выходного порта наследуется либо от сигнала, подключенного к порту, либо от модели HDL.

Для приемного устройства: задайте выходные порты блоков.

Для исходного устройства: задайте входные порты блоков.

Введите имена пути сигнала в столбце Full HDL name, дважды кликнув по существующему сигналу по умолчанию.

Используйте синтаксис имени Симулятора HDL пути (как описано в Specify HDL Signal/Port and Module Paths for Simulink Test Bench Cosimulation).

Если вы добавляете сигналы, нажмите New, а затем отредактируйте значения по умолчанию. Выберите один из Input или Output из столбца I/O Mode.

Если вы хотите, установите параметры Sample Time, Data Type и Fraction Length для сигналов явно, как обсуждается на остальных шагах.

Когда вы закончите редактировать синхросигналы, нажмите Apply, чтобы зарегистрировать изменения в Simulink.

В следующем диалоговом окне показаны определения портов для блока HDL Cosimulation. Имена пути сигнала совпадают с именами путей, которые появляются в окне Симулятора HDL wave (Приведенный пример).

Примечание

Когда вы задаете вход порт, убедитесь, что только один источник настроен, чтобы принудительно вход к этому порту. Если несколько источников управляют сигналом, ваша модель Simulink может привести к непредсказуемым результатам.

Необходимо задать шаг расчета для портов выхода. Simulink использует заданное значение и текущие настройки панели Timescales, чтобы вычислить фактический шаг расчета симуляции.

Для получения дополнительной информации о шагах расчета в среде косимуляции HDL Verifier, смотрите Simulation Timescales.

При необходимости можно явным образом сконфигурировать тип данных с фиксированной точкой каждого выходного порта или использовать тип по умолчанию (Inherited). В случае по умолчанию Simulink определяет тип данных для порта выходов следующим образом:

Если Simulink может определить тип данных сигнала, подключенного к порту выхода, он применяет этот тип данных к порту выходов. Для примера тип данных соединенного блока Signal Спецификации известен обратным распространением. В противном случае Simulink запрашивает Симулятор HDL, чтобы определить тип данных сигнала от HDL-модуля.

Чтобы назначить явный тип данных с фиксированной точкой сигналу, выполните следующие шаги:

Выберите один из Signed или Unsigned из столбца Data Type.

Если сигнал имеет дробную часть, введите Fraction Length.

Для примера, если модель имеет 8-битный сигнал с Signed тип данных и Fraction Length 5блок HDL Cosimulation присваивает ему тип данных sfix8_En5. Если у модели есть Unsigned 16-битный сигнал без дробной части (a Fraction Length из 0), блок HDL Cosimulation присваивает ему тип данных ufix16.

Перед закрытием диалогового окна нажмите кнопку Apply, чтобы зарегистрировать изменения.

Управление Выходным Портом Непосредственно по Значению Input port. Включение прямого сквозного соединения позволяет входу изменениям значений портов распространяться на выходные порты за ноль времени, таким образом устраняя возможную задержку на выходе выборки в HDL- проектов с чистой комбинационной логикой. Задайте опцию для включения прямого сквозного соединения на панели Ports, как показано на следующем рисунке.

Параметры Data Type и Fraction Length применяются только к выходным сигналам. См. Data Type и Fraction Length на панели Ports описания блока HDL Cosimulation.

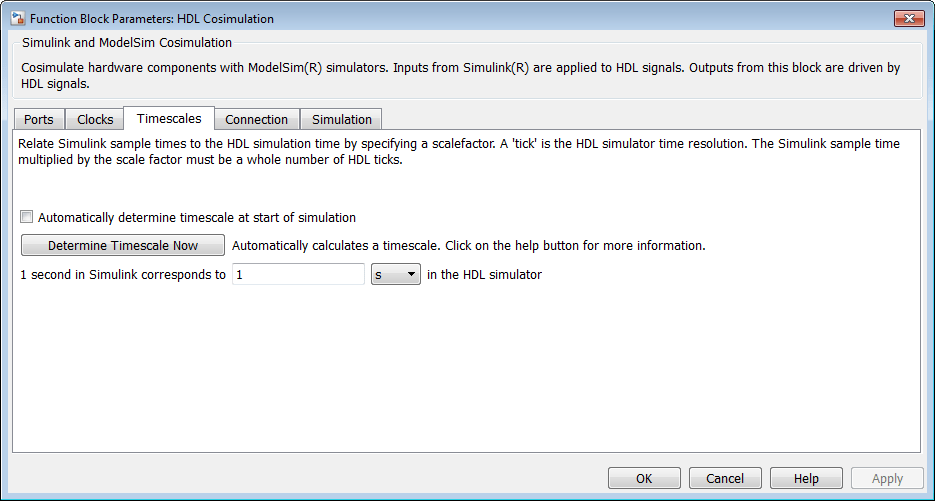

Отношения синхронизации между Simulink и Симулятором HDL конфигурируются с помощью панели Timescales диалогового окна параметров блоков. Прежде чем устанавливать параметры Timescales, прочитайте Simulation Timescales, чтобы понять поддерживаемые режимы синхронизации и проблемы, которые определят ваш выбор режима синхронизации.

Можно задать относительное или абсолютное отношение времени между Simulink и Симулятором HDL на панели Timescales, как описано в HDL Cosimulation ссылке на блок.

Отношения Simulink и Симулятора HDL Timing. Различия в представлении времени симуляции могут быть согласованы одним из двух способов с помощью интерфейса HDL Verifier:

Путем определения отношения синхронизации вручную (с Timescales панелью)

Когда вы задаете отношение вручную, вы определяете, сколько фемтосекунд, пикосекунд, наносекунд, микросекунд, миллисекунд, секунд или тактов в симуляторе HDL представляют 1 секунду в Simulink.

![]()

Такое количество времени симулятора HDL может быть выражено одним из следующих способов:

В относительных терминах (т.е. как некоторое количество Симулятора HDL тактов). В этом случае, называется, что косимуляция работает в относительном временном режиме. Блок HDL Cosimulation по умолчанию переходит в относительный режим синхронизации для косимуляции. Для получения дополнительной информации об относительном режиме синхронизации см. Раздел «Относительный режим синхронизации».

В абсолютных модулях (таких как миллисекунды или наносекунды). В этом случае называется, что косимуляция работает в абсолютном временном режиме. Для получения дополнительной информации об абсолютном режиме синхронизации см. «Абсолютный режим синхронизации».

Для получения дополнительной информации об относительном и абсолютном времени смотрите Simulation Timescales.

Путем разрешения HDL Verifier определять шкалу времени (с Timescales панелью)

Когда вы позволяете программному обеспечению ссылки задать отношение времени, он пытается задать коэффициент времени между Симулятором HDL и Simulink как можно ближе к 1 секунде при Симуляторе HDL = 1 секунде в Simulink. Если эта настройка невозможна, продукт звена пытается установить скорость сигнала на порте модели Simulink на самое низкое возможное количество меток HDL-симулятора.

Прежде чем вы начнете, проверьте, что Симулятор HDL работает. Программное обеспечение HDL Verifier может получить разрешение по пределу Симулятора HDL только при запуске этого симулятора.

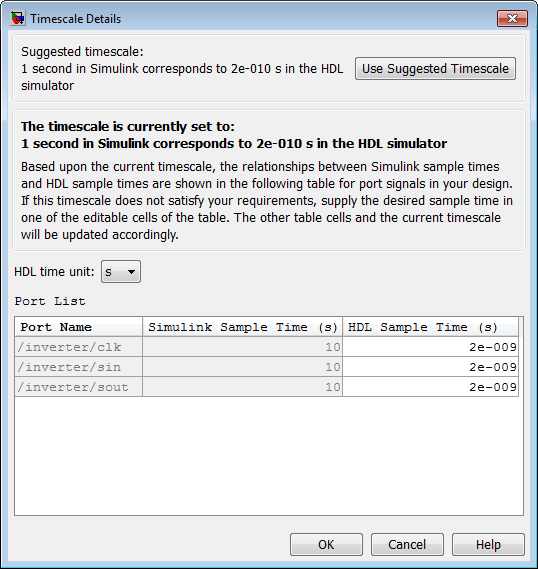

Можно выбрать, чтобы HDL Verifier вычислял шкалу времени во время установки параметров в диалоговом окне блока, нажав на опцию Timescale, затем щелкнув Determine Timescale Now или можно получить HDL Verifier вычислить шкалу времени, когда симуляция начинается путем выбора Automatically determine timescale at start of simulation.

При нажатии кнопки Determine Timescale Now HDL Verifier соединяет Simulink с Симулятором HDL, чтобы он мог использовать разрешение Симулятора HDL для вычисления оптимального временного шкалы. Вы можете принять предложения HDL Verifier во временной шкале или внести изменения в список портов непосредственно. Если необходимо вернуться к первоначально рассчитанным настройкам, нажмите кнопку Use Suggested Timescale. Если необходимо просмотреть шаги расчета для всех портов в HDL- проекта, выберите Show all ports and clocks.

Если вы выбираете Automatically determine timescale at start of simulation, вы получаете то же диалоговое окно, когда симуляция начинается в Simulink. Внесите те же корректировки в то время, если применимо, что и если вы кликнули Determine Timescale Now при конфигурировании блока.

Необходимо выбрать общую память или связь с сокетом. Смотрите HDL-косимуляцию с MATLAB или Simulink.

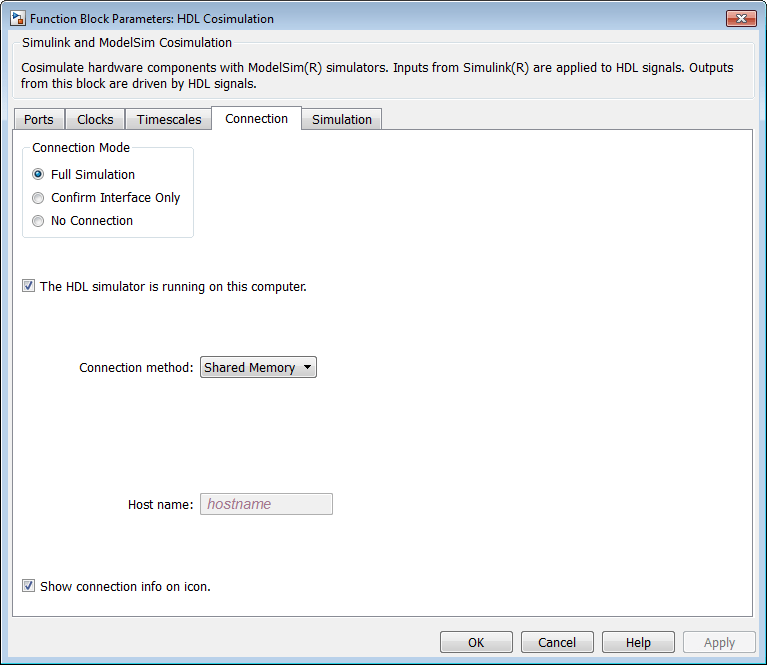

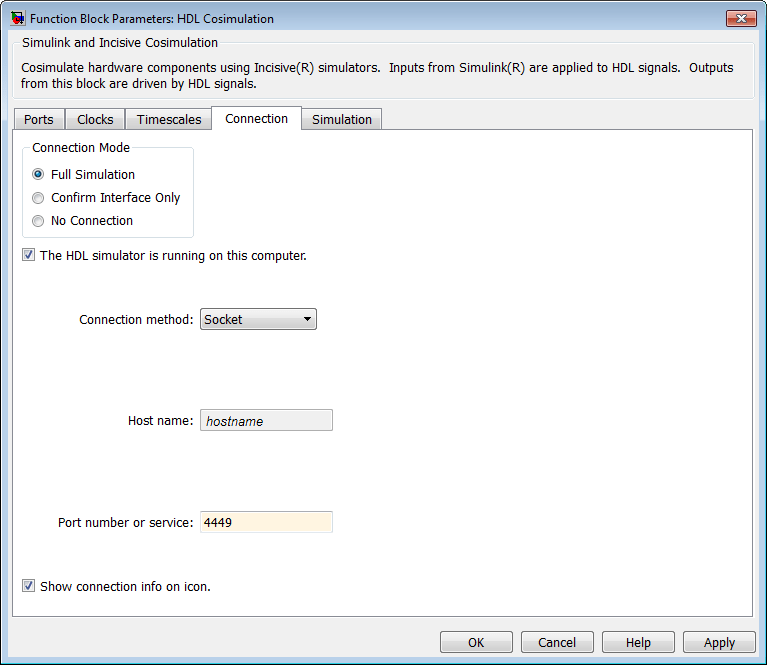

После того, как вы решите, какой тип связи, сконфигурируйте коммуникационную ссылку блока с Connection панелью диалогового окна параметров блоков (пример показан для использования с ModelSim).

Следующие шаги проведут вас через строение связи:

Определите, работают ли Simulink и Симулятор HDL на одном компьютере. Если они есть, перейдите к шагу 4.

Очистить The HDL simulator is running on this computer. (Этот флажок по умолчанию установлен.) Поскольку Simulink и Симулятор HDL работают на разных компьютерах, HDL Verifier устанавливает Connection method равным Socket.

Введите имя хоста компьютера, на котором выполняется симуляция HDL (в симуляторе HDL), в Host name текстовое поле. В Port number or service текстовом поле укажите допустимый номер порта или службы для вашей компьютерной системы. Для получения информации о выборе портов разъема TCP/IP см. раздел Порты разъема TCP/IP. Перейдите к шагу 5.

Если Симуляторы HDL и Simulink работают на одном компьютере, решите, будете ли вы использовать общую память или TCP/IP сокеты для канала связи. Для получения информации о различных режимах связи смотрите HDL-косимуляцию с MATLAB или Simulink.

Если вы выбираете коммуникацию TCP/IP сокетов, укажите действительный номер порта или услуги для вашей компьютерной системы в Port number or service текстовом поле. Для получения информации о выборе портов разъема TCP/IP см. раздел Порты разъема TCP/IP.

Если вы выбираете связь с общей памятью, установите флажок Shared memory.

Если вы хотите обойти симулятор HDL, когда вы запускаете симуляцию Simulink, используйте опции Connection Mode, чтобы указать, какой тип соединения симуляции вы хотите. Выберите один из следующих опций:

Full Simulation: Подтвердите интерфейс и запустите симуляцию HDL (по умолчанию).

Confirm Interface Only: Проверьте Симулятор HDL на ожидаемые имена сигналов, размерности и типы данных, но не запускайте HDL- симуляции.

No Connection: Не общайтесь с симулятором HDL. Запуск Симулятора HDL не требуется.

При помощи вторых и третьих опций программное обеспечение HDL Verifier не взаимодействует с симулятором HDL во время симуляции Simulink.

Нажмите Apply.

В следующем примере диалогового окна показаны определения связи для блока HDL Cosimulation. Блок сконфигурирован для Simulink и симулятора HDL, работающего на том же компьютере, взаимодействуя в режиме сокета TCP/IP через TCP/IP порт 4449.

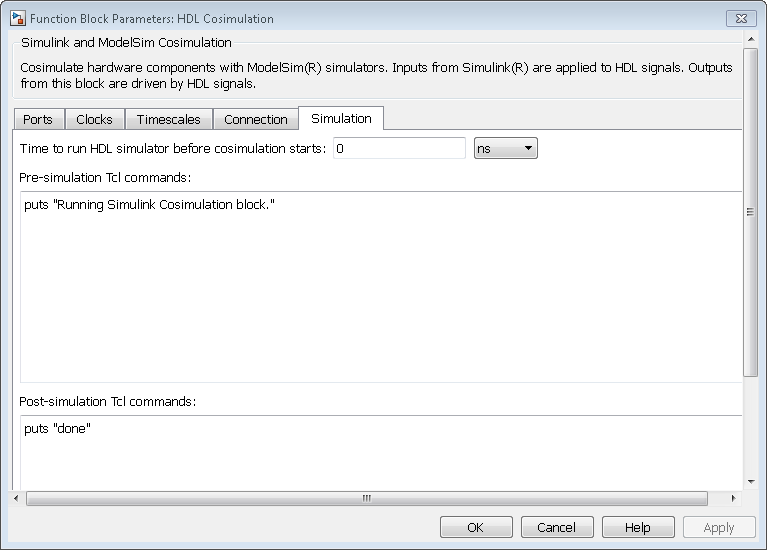

У вас есть опция задать команды Tcl для выполнения до и после того, как Симулятор HDL симулирует HDL- компонента вашей модели Simulink. Tcl является программируемым языком скриптов, поддерживаемым большинством сред симуляции. Использование Tcl может варьироваться от чего-то такого простого, как однолинейное puts команда, чтобы подтвердить, что симуляция выполняется или так же завершена как комплексный скрипт, который выполняет обширную последовательность инициализации и запуска симуляции. Например, можно использовать поле Post- simulation command на панели Simulation Pane, чтобы дать указание симулятору HDL перезапустить в конце запуска симуляции.

Примечание для пользователей ModelSim

После каждой симуляции требуется время ModelSim, чтобы обновить результат покрытия. Чтобы предотвратить потенциальный конфликт между этим процессом и следующим сеансом косимуляции, добавьте короткую паузу между каждой последующей симуляцией.

Можно задать команды Tcl до и постсимуляция путем ввода команд Tcl в команды Pre-simulation или Post-simulation текстовые поля команд в панели Simulation диалогового окна параметров блоков HDL Cosimulation.

Чтобы задать команды Tcl, выполните следующие шаги:

Выберите вкладку Simulation диалогового окна параметров блоков. Диалоговое окно появляется следующим образом (пример показан для использования с ModelSim).

Текстовое поле Pre-simulation commands содержит puts команда в ссылочных целях.

Введите одну или несколько команд в текстовые поля Pre-simulation command и Post-simulation command. Можно задать одну команду Tcl для линии в текстовом поле или ввести несколько команд для линии, добавив каждую команду с точкой с запятой (;), которая является стандартным оператором конкатенации Tcl.

Нажмите Apply.

Один из способов управления параметрами блоков - это графическое диалоговое окно HDL Cosimulation блоков. Однако можно также управлять блоками, программно управляя значениями параметров маски и выполнением симуляций. Значения параметров могут быть считаны с помощью Simulink get_param функция и запись с помощью Simulink set_param функция. Все параметры блоков имеют атрибуты, которые указывают, являются ли они:

Настраиваемый - атрибуты могут измениться во время запуска симуляции.

Рассчитано - значение параметров подвергается оценке, чтобы определить его фактическое значение, используемое S-Функцией.

Блок HDL Cosimulation не имеет никаких настраиваемых параметров; таким образом, вы получите ошибку, если попытаетесь изменить значение во время симуляции. Однако у него есть несколько оцененных параметров.

Список параметров и их атрибутов можно увидеть, выполнив щелчок правой кнопкой мыши по блоку, выбрав View Mask, а затем вкладку Parameters. В Variable столбце показаны имена программных параметров. Также можно получить имена программно, выбрав блок HDL Cosimulation и затем набрав следующие команды в подсказке MATLAB:

>> get_param(gcb, 'DialogParameters')

Ниже приведены некоторые примеры использования MATLAB для управления симуляциями и значениями параметров маски. Обычно команды помещаются в скрипт или файл функции и вызываются несколькими крюками коллбэка, доступными разработчику модели. Вы можете поместить код в любое из следующих предлагаемых местоположений Simulink:

В рабочем пространстве модели. На вкладке Modeling, в разделе Design, нажмите Model Explorer. В диалоговом окне Model Explorer, на панели Model Hierarchy, выберите Simulink Root > model_name > Model Workspace. На панели Model Workspace из списка Data source. Выберите Model File.

В модели коллбэка. На вкладке Modeling, в разделе Setup, нажмите Model Settings > Model Properties. В диалоговом окне Свойства модели задайте функцию обратного вызова на вкладке Callbacks.

В обратном коллбэке подсистемы. Щелкните правой кнопкой мыши по пустой подсистеме и выберите Properties > Callbacks. Многие демонстрации HDL Verifier используют этот метод, чтобы запустить симулятор HDL, поместив код MATLAB в OpenFcn коллбэк.

В HDL Cosimulation блокируйте коллбэк. Щелкните правой кнопкой мыши по HDL Cosimulation блоку и выберите Properties > Callbacks.

Пример: Создание скрипта значения номера сокета для Симулятора HDL связи. В регрессионном окружении, возможно, вам потребуется определить номер сокета для подключения симулятора Simulink/HDL во время симуляции, чтобы избежать столкновений с другими запусками симуляции. В этом примере показан код, который мог бы обработать эту задачу. Скрипт предназначен для 32-битного Linux® платформы.

ttcp_exec = [matlabroot '/toolbox/shared/hdllink/scripts/ttcp_glnx'];

[status, results] = system([ttcp_exec ' -a']);

if ~s

parsed_result = textscan(results,'%s');

avail_port = parsed_result{1}{2};

else

error(results);

end

set_param('MyModel/HDL Cosimulation', 'CommPortNumber', avail_port);