Если у вас есть Simulink® Coder™ лицензии можно сгенерировать компоненты DPI SystemVerilog одним из двух методов.

HDL Verifier™ интегрируется с Simulink Coder, чтобы экспортировать подсистему в качестве сгенерированного кода C внутри компонента SystemVerilog с интерфейсом прямого программирования (DPI). Можно интегрировать этот компонент в HDL- симуляции как поведенческую модель. Кодер предоставляет опции для настройки сгенерированной структуры SystemVerilog. Генератор компонентов поддерживает доступ к тестовым точкам и настраиваемые параметры. Кодер опционально генерирует испытательный стенд SystemVerilog, который проверяет сгенерированный компонент DPI на соответствие векторам данных из подсистемы Simulink. Эта функция доступна в диалоговом окне Параметры конфигурации модели (Model Configuration Parameters) под Code Generation. См. «Генерация компонента DPI SystemVerilog».

Из HDL- Coder™ можно сгенерировать испытательный стенд SystemVerilog DPI. Используйте испытательный стенд, чтобы проверить ваш сгенерированный HDL-код с помощью кода C, сгенерированного из всей вашей модели Simulink, включая DUT и источники данных. Чтобы использовать эту функцию, вся ваша модель должна поддерживать генерацию кода C с Simulink Coder. Вы можете получить доступ к этой функции в HDL Workflow Advisor по пути HDL Code Generation > Set Testbench Options или в диалоговом окне Параметры конфигурации модели (Model Configuration Parameters) по пути HDL Code Generation > Test Bench. Кроме того, для доступа из коммандной строки установите GenerateSVDPITestBench свойство makehdltb (HDL Coder). См. раздел Проверка HDL- Проекта с использованием DPI- Испытательного стенда SystemVerilog (HDL Coder).

Поддерживаемые типы данных Simulink преобразуются в типы данных SystemVerilog, как показано в этой таблице.

Можно выбрать битовый вектор, логический вектор или совместимый тип C. Выберите в Параметры конфигурации окне, в разделе Code Generation > SystemVerilog DPI, под SystemVerilog Ports > Ports data type.

Сгенерированные типы SystemVerilog

| MATLAB® | SystemVerilog | ||

|---|---|---|---|

| Совместимый тип C | Логический вектор | Битовый вектор | |

uint8 | byte unsigned | logic [7:0] | bit [7:0] |

uint16 | shortint unsigned | logic [15:0] | bit [15:0] |

uint32 | int unsigned | logic [31:0] | bit [31:0] |

uint64 | longint unsigned | logic [63:0] | bit [63:0] |

int8 | byte | logic signed [7:0] | bit signed [7:0] |

int16 | shortint | logic signed [15:0] | bit signed [15:0] |

int32 | int | logic signed [31:0] | bit signed [31:0] |

int64 | longint | logic signed [63:0] | bit signed [63:0] |

boolean | byte unsigned | logic [0:0] | bit [0:0] |

| фиксированная точка | Порт расширен до встроенного типа C, такого как |

Логическая длина вектора ( |

Длина вектора бита ( |

single | shortreal | ||

double | real | ||

complex | Можно выбрать между SystemVerilog | ||

| векторы, матрицы | Можно выбрать между массивами SystemVerilog или скалярными портами. Чтобы выбрать между этими опциями, в левой панели диалогового окна Параметры конфигурации выберите Code Generation > SystemVerilog DPI, а затем выберите параметр Scalarize matrix and vector ports. Для примера - двухэлементный вектор типа input logic [31:0] vecInput [0:1] Когда вы выбираете Scalarize matrix and vector ports, сгенерированный SystemVerilog включает эти два порта, каждый из которых имеет тип input logic [31:0] vecInput_0, input logic [31:0] vecInput_1 При генерации портов вектора и массива кодер уплощает матрицы в основном порядке. | ||

| невиртуальная шина | Можно выбрать между SystemVerilog | ||

| перечисленные типы данных | enum | ||

Весь код SystemVerilog, сгенерированный генератором DPI SystemVerilog, содержит эти сигналы управления:

clk - синхроимпульс

clk_enable - включение синхроимпульса

reset - асинхронный сброс

Выберите между списком портов или объявлением интерфейса. Установите эту опцию в параметрах конфигурации в разделе Code Generation > SystemVerilog ports > Connection.

Список портов - генерирует модуль SystemVerilog со списком портов в заголовке, представляющим его интерфейс.

Для примера:

module MyMod_dpi(

input bit clk,

input bit clk_enable,

input bit reset,

/* Simulink signal name: 'in1' */

input real in1 ,

/* Simulink signal name: 'out1' */

output real out1

);

...

endmoduleИнтерфейс - генерирует модуль SystemVerilog с именем интерфейса в заголовке и отдельным объявлением интерфейса.

Для примера:

interface simple_if;

bit clk;

bit clk_enable;

bit reset;

/* Simulink signal name: 'in1' */

real in1 ;

/* Simulink signal name: 'out1' */

real out1 ;

endinterface

module MyMod_dpi(

simple_if vif

);

...

endmodule

Альтернатива командной строки: используйте set_param (Simulink) и установите DPIPortConnection параметр к любому из 'Interface' или 'Port List'.

Для примера:

set_param(bdroot, 'DPIPortConnection','Interface')

Код SystemVerilog, сгенерированный генератором DPI SystemVerilog, содержит следующие функции:

// Declare imported C functions

import "DPI" function chandle DPI_subsystemname_initialize(chandle existhandle);

import "DPI" function chandle DPI_subsystemname_reset(input chandle objhandle,...

input real In1, inout real Out1);

import "DPI" function void DPI_subsystemname_output(input chandle objhandle, ...

input real In1, inout real Out1);

import "DPI" function void DPI_subsystemname_update(input chandle objhandle, input real In1);

import "DPI" function void DPI_subsystemname_terminate(input chandle objhandle);

Здесь, subsystemname - имя подсистемы, для которой вы сгенерировали код.

Если ваша модель также содержит настраиваемые параметры, см. «Настройка параметра».

Функция Initialize - The Initialize функция вызывается в начале симуляции.

Для примера - для подсистемы с названием dut:

initial begin

objhandle = DPI_dut_initialize(objhandle);

end

Функция сброса - Вызов reset функция, когда вы хотите сбросить симуляцию в известное состояние сброса.

Для примера - для подсистемы с названием dut:

initial begin

objhandle = DPI_dut_reset(objhandle, 0, 0);

end

Выходная функция - При положительном ребре часов, если clk_enable высоко, сначала вызывается выходная функция, далее следует функция обновления.

Для примера - для подсистемы с названием dut:

if(clk_enable) begin

DPI_dut_output(objhandle, dut_In1, dut_Out1);

DPI_dut_update(objhandle, dut_In1);

end

Функция обновления

На положительном ребре синхроимпульса, если clk_enable высоко, функция обновления вызывается после выходной функции.

Для примера - для подсистемы с названием dut:

if(clk_enable) begin

DPI_dut_output(objhandle, dut_In1, dut_Out1);

DPI_dut_update(objhandle, dut_In1);

end

Функция завершения

Установите конкретные условия для раннего прекращения симуляции.

Для примера - для подсистемы с названием dut:

if (condition for termination) begin DPI_dut_terminate(objhandle); end

Подробные данные функции в коде SystemVerilog, сгенерированном из вашей системы, варьируются. Можно изучить сгенерированный код на предмет специфики. Пример сгенерированных функций в контексте смотрите в Запуск с SystemVerilog Генерация компонентов DPI.

Можно запустить различные симуляции с различными значениями параметров в модели Simulink. Если ваша система имеет настраиваемые параметры, сгенерированный код SystemVerilog также содержит функцию Set Parameter для каждого настраиваемого параметра.

Генератор компонента DPI генерирует функцию Set Parameter для каждого настраиваемого параметра в формате DPI_<reservedrangesplaceholder0 >_setparam_<reservedrangesplaceholder0 >

В этом примере настраиваемый параметр усиления имеет свое setparam_gain функция.

import "DPI" function void DPI_dut_setparam_gain(input chandle objhandle, input real dut_P_gain);

Сгенерированный код SystemVerilog не вызывает эту функцию. Вместо этого используются параметры по умолчанию. Чтобы изменить эти параметры во время симуляции, явным образом вызовите конкретный setparam функция. Для примера в подсистеме под названием dut, можно изменить коэффициент усиления во время симуляции на значение 6 путем вставки следующего вызова:

DPI_dut_setparam_gain(objhandle, 6);

Чтобы сделать параметр настраиваемым, создайте объект данных из подсистемы перед генерацией кода SystemVerilog. См. «Настройка параметра усиления во время симуляции».

Эта функция позволяет вам получить доступ к внутренним сигналам компонента DPI SystemVerilog в симуляторе HDL. Можно назначить внутренние сигналы в модели в качестве тестовых точек и сконфигурировать генератор DPI SystemVerilog, чтобы создать отдельные или сгруппированные функции доступа.

Можно также включить вход в тестовые точки. С включенным логгированием можно использовать сгенерированный испытательный стенд для сравнения записанных данных из Simulink со значениями, наблюдаемыми при запуске компонента SystemVerilog.

См. SystemVerilog DPI Component Test Point Access и Запуск с SystemVerilog DPI Генерация.

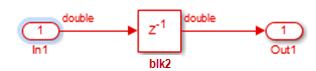

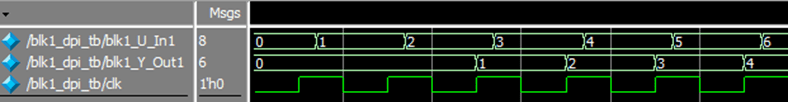

По сравнению с исходной моделью Simulink сгенерированный модуль SystemVerilog вводит одну дополнительную задержку выборки на выходе. Для примера в следующей модели Simulink выход представляет собой задержанную версию входного сигнала с одной выборкой.

Сгенерированный код C сохраняет это поведение, и выход содержит задержанную версию входного сигнала с одной выборкой. Однако в файле обертки SystemVerilog синхросигнал используется для синхронизации входа и выходных сигналов:

always @(posedge clk) begin

DPI_blk2_output(blk2_In1, blk2_Out1);

DPI_blk2_update();

endВыход модуля SystemVerilog может обновляться только на переднем фронте синхроимпульса. Это требование вводит дополнительную задержку выборки.

По умолчанию подсистемы Simulink имеют фундаментальный переменный шаг расчета (FundST), которая указывает, когда во время симуляции подсистема производит выходы и обновляет свое внутреннее состояние. С мультирейт-системами можно задать различные шаги расчета для различных портов. Для получения дополнительной информации смотрите Что такой Шаг расчета? (Simulink).

Когда мультирациональная подсистема генерирует компонент DPI, компонент DPI запускается во времени расчета, которое равно наибольшему общему делителю всех шагов расчета в подсистеме.

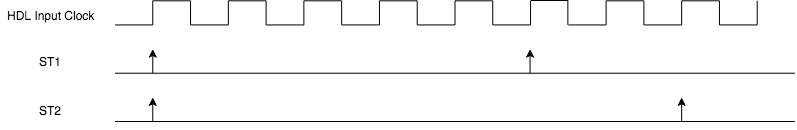

Для примера предположим, что подсистема имеет основной шаг расчета 0,01 (то есть FundST является 0.01) и шаги расчета ST1 и ST2 0,5 и 0,7, соответственно.

ST1=0.5, ST2=0.7. Компонент DPI запускается во шаге расчета 0,1 (потому что 0,1 является наибольшим общим делителем 0,5 и 0,7). Чтобы успешно получить сигнал со шаг расчета 0,5 (ST1) или 0,7 (ST2), синхросигнал HDL должен переключаться пять или семь раз, соответственно.

Когда компонент DPI генерируется с верхнего уровня, компонент выполняется с основным шагом расчета.

Эта схема показывает связь между входным синхроимпульсом HDL и шагами расчета ST1 и ST2.

Можно настроить сгенерированный упаковщик SystemVerilog, изменив шаблон, включенный в HDL Verifier (svdpi_grt_template.vgt). Кроме того, можно создать свой собственный пользовательский шаблон. Укажите якоря для сгенерированного кода в шаблоне, чтобы убедиться, что шаблон генерирует действительный код SystemVerilog.

Шаблон SystemVerilog по умолчанию, предоставляемый HDL Verifier svdpi_grt_template.vgt. В этом шаблоне специальные clken_in и clken_out сигналы управления добавляются к интерфейсу модуля SystemVerilog.

Можно сгенерировать компоненты DPI SystemVerilog из нескольких подсистем и соединить их вместе в Симулятор HDL. Когда вы делаете это, эти сигналы управления определяют порядок выполнения этих компонентов. Они также минимизируют задержку между сигналом Simulink и сигналом SystemVerilog.

Можно также задать свой собственный файл шаблона со следующими условиями:

Файл должен быть указан в пути MATLAB и доступен для поиска.

Файл должен иметь .vgt расширение.

Можно использовать эти дополнительные лексемы для настройки сгенерированного кода путем вставки их в операторы комментариев на протяжении всего шаблона:

%<FileName>

%<PortList>

%<EnumDataTypeDefinitions>

%<ImportInitFunction>

%<ImportOutputFunction>

%<ImportUpdateFunction>

%<ImportSetParamFunction>

%<CallInitFunction>

%<CallUpdateFunction>

%<CallOutputFunction>

%<IsLibContinuous>

%<ObjHandle>

Инструкции по настройке кода см. в разделе Настройка сгенерированного кода SystemVerilog.

Примечание

Генератор компонентов DPI SystemVerilog не генерирует испытательные стенды для настраиваемых компонентов.

По умолчанию HDL Verifier преобразует матрицы и векторы в одномерные массивы в SystemVerilog. Для примера матрица 4 на 2 в Simulink преобразуется в одномерный массив из восьми элементов в SystemVerilog. Чтобы сгенерировать несколько скалярных портов в интерфейсе SystemVerilog, выберите Scalarize matrix and vector ports в параметрах конфигурации.

Генерация компонентов DPI SystemVerilog поддерживает следующие подсистемы только для генерации кода. Нет поддержки испытательных стендов для этих подсистем.

Триггируемая подсистема

Включенная подсистема

Подсистема с портом действия

Для достижения наилучших результатов избегайте экспорта нескольких подсистем отдельно, поскольку может быть трудно достичь правильного порядка выполнения. Вместо этого объедините несколько подсистем в одну и сгенерируйте код из вновь созданной, одной подсистемы.