В этой главе приведены основные шаги для настройки HDL Verifier™ сеанса, которая использует Simulink® и блок HDL Cosimulation для проверки HDL- модели. Блок HDL Cosimulation косимулирует оборудование компонент путем применения входных сигналов к и считывания выхода сигналов от HDL- модели под симуляцией в ModelSim®/ Questa®Сим. Блок HDL Cosimulation поддерживает симуляцию любого VHDL® или Verilog® модели. В руководстве в этом разделе вы косимулируете простую модель VHDL.

Примечание

Это руководство характерно для Mentor Graphics® пользователи симулятора; однако большая часть процесса будет такой же для Incisive® пользователей.

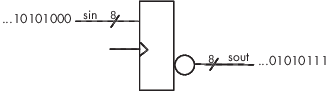

Типичный сценарий Simulink и ModelSim состоит в том, чтобы создать модель для определенного аппаратного компонента в ModelSim, который позже необходимо интегрировать в большую модель Simulink. Первым шагом является разработка и разработка модели VHDL в ModelSim. В этом руководстве вы используете ModelSim и VHDL, чтобы разработать модель, которая представляет следующий инвертор:

VHDL- сущности для этой модели будет представлять 8-битные потоки входа и выходных значений сигналов с IN порт и OUT порт типа STD_LOGIC_VECTOR. Сигнал входа тактового сигнала типа STD_LOGIC инициирует процесс инверсии битов при установке.

Выполните следующие шаги:

Запуск ModelSim

Измените папку с возможностью записи MyPlayArea, который вы, возможно, создали для другого руководства. Если вы не создали папку, создайте ее сейчас. Папка должна быть доступной для записи.

ModelSim>cd C:/MyPlayArea

Откройте новое окно редактирования исходного файла VHDL.

Добавьте следующий код VHDL:

---------------------------------------------------

-- Simulink and ModelSim Inverter Tutorial

--

-- Copyright 2003-2004 The MathWorks, Inc.

--

---------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY inverter IS PORT (

sin : IN std_logic_vector(7 DOWNTO 0);

sout: OUT std_logic_vector(7 DOWNTO 0);

clk : IN std_logic

);

END inverter;

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ARCHITECTURE behavioral OF inverter IS

BEGIN

PROCESS(clk)

BEGIN

IF (clk'EVENT AND clk = '1') THEN

sout <= NOT sin;

END IF;

END PROCESS;

END behavioral;

Сохраните файл в inverter.vhd.

В этом разделе описывается, как настроить библиотеку проектов и скомпилировать inverter.vhd, следующим образом:

Проверьте, что файл inverter.vhd находится в текущей папке путем ввода ls команда в командной строке ModelSim.

Создайте библиотеку проекта, чтобы сохранить результаты компиляции. Создание библиотеки и необходимых _info файл, введите vlib и vmap команды следующим образом:

ModelSim> vlib work ModelSim> vmap work work

Если библиотека проекта уже существует, ModelSim не перезаписывает текущую библиотеку, но отображает следующее предупреждение:

# ** Warning: (vlib-34) Library already exists at "work".

Примечание

Необходимо использовать меню File ModelSim или vlib команду, чтобы создать папку библиотеки так, чтобы необходимая _info создается файл. Не создавайте библиотеку с командами операционной системы.

Скомпилируйте файл VHDL. Один из способов компиляции файла - кликнуть имя файла в рабочей области проекта и выбрать Compile > Compile All. Другой альтернативой является указание имени файла VHDL с vcom команда, следующим образом:

ModelSim> vcom inverter.vhd

Если компиляции выполняются успешно, в командном окне появляются информационные сообщения, и компилятор заполняет рабочую библиотеку результатами компиляции.

Теперь создайте свою модель Simulink. Для этого руководства вы создаете простую модель Simulink, которая управляет входом в блок, представляющий VHDL-инвертор, который вы кодировали в Develope VHDL Code, и отображает инвертированный выход.

Начните с создания модели следующим образом:

Запуск MATLAB®, если он еще не запущен. Откройте новое окно модели. Затем откройте Library Browser Simulink.

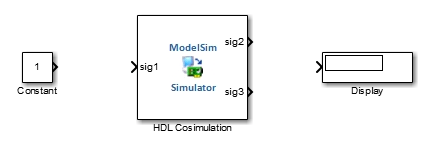

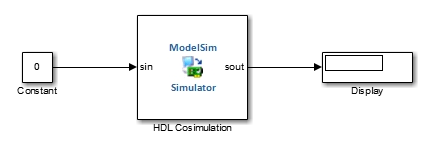

Перетащите следующие блоки из Library Browser Simulink в окно модели:

Constant блок из библиотеки Sources Simulink

HDL Cosimulation блок из библиотеки блоков HDL Verifier

Display блок из библиотеки Sinks Simulink

Расположите три блока в порядке, показанном на следующем рисунке.

Затем сконфигурируйте блок Constant, который является входным источником модели, выполнив следующие действия:

Дважды кликните значок Constant блока, чтобы открыть диалоговое окно Constant параметров блоков. Введите следующие значения параметров на панели Main:

Constant value: 0

Sample time: 10

Позже можно изменить эти начальные значения, чтобы увидеть эффект различных шагов расчета на различные запуски симуляции.

Теперь диалоговое окно должно появиться следующим образом.

Перейдите на вкладку Signal Attributes. Теперь в диалоговом окне отображается меню Output data type.

Выберите uint8 из Output data type меню. Эта спецификация типа данных поддерживается программным обеспечением HDL Verifier без необходимости преобразования типа. Он сопоставляется непосредственно с типом VHDL для порта VHDL sin, STD_LOGIC_VECTOR(7 DOWNTO 0).

Теперь диалоговое окно должно появиться следующим образом.

Нажмите OK. Диалоговое окно параметров Constant блоков закроется, и значение в значке Constant блока изменится на 0.

Затем сконфигурируйте блок HDL Cosimulation, который представляет модель инвертора, написанную на VHDL. Начните с панели Ports, выполнив следующие действия:

Дважды кликните значок HDL Cosimulation блока. Появится диалоговое окно Block Parameters для блока HDL Cosimulation. Перейдите на вкладку Ports.

На панели Ports выберите сигнал расчета /top/sig1 из списка сигналов в центре панели двойным щелчком мыши по нему.

Замените имя пути сигнала расчета /top/sig1 с /inverter/sin. Затем нажмите Apply. Имя сигнала на блоке HDL Cosimulation изменяется.

Точно так же выберите сигнал расчета /top/sig2. Измените Full HDL Name на /inverter/sout. Выберите Output из списка I/O Mode. Измените параметр Sample Time на 10. Затем нажмите Apply, чтобы обновить список.

Выберите сигнал расчета /top/sig3. Нажмите кнопку Delete. Теперь сигнал удаляется из списка.

Панель Ports должна появиться следующим образом.

Теперь сконфигурируйте параметры панели Connection, выполнив следующие действия:

Перейдите на вкладку Connection.

Оставьте Connection Mode как Full Simulation.

Выберите сокет из списка Connection method . Эта опция определяет, что Simulink и ModelSim будут взаимодействовать через назначенный порт сокета TCP/IP. Обратите внимание, что теперь видны два дополнительных поля, Port number or service и Host name.

Обратите внимание, что, поскольку The HDL simulator is running on this computer выбран по умолчанию, поле Host name отключено. В этом строении Simulink и ModelSim выполняются на одном компьютере, поэтому вам не нужно вводить имя удаленной системы хоста.

В Port number or service текстовом поле введите номер порта сокета 4449 или, если этот порт недоступен в вашей системе, другой допустимый номер порта или имя службы. Модель будет использовать коммуникацию TCP/IP сокета для связи с ModelSim. Обратите внимание, что вы вводите для этого параметра. Та же информация о порте сокета будет задана при настройке ModelSim для соединения с Simulink.

Панель Connection должна появиться следующим образом.

Нажмите Apply.

Теперь сконфигурируйте панель Clocks, выполнив следующие действия:

Перейдите на вкладку Clocks.

Нажмите кнопку New. В список сигналов добавляется новый синхросигнал с пустым именем сигнала.

Дважды кликните новое имя сигнала для редактирования. Введите путь сигнала /inverter/clk. Затем выберите Rising из списка Edge. Установите параметр Period равным 10.

Панель Clocks должна появиться следующим образом.

Нажмите Apply.

Затем введите некоторые простые команды Tcl, которые будут выполняться до и после симуляции, следующим образом:

Перейдите на вкладку Simulation.

В Pre-simulation Tcl commands текстовом поле отредактируйте команду Tcl по умолчанию:

puts "Running inverter in Simulink!"

В Post-simulation Tcl commands текстовом поле отредактируйте команду Tcl по умолчанию:

puts "Inverter Done"

Панель Simulation должна появиться следующим образом.

Нажмите Apply.

Затем просмотрите панель Timescales, чтобы убедиться, что она установлена на свои параметры по умолчанию, следующим образом:

Перейдите на вкладку Timescales.

Настройки по умолчанию для панели Timescales показаны на следующем рисунке. Эти настройки необходимы для операции этого примера. Для получения дополнительной информации смотрите Simulation Timescales.

Нажмите кнопку OK, чтобы закрыть диалоговое окно Block Parameters.

Конечным шагом является соединение блоков, конфигурирование параметров всей модели и сохранение модели. Выполните следующие действия:

Соедините блоки как показано на следующем рисунке.

На данной точке можно также рассмотреть возможность корректировки аннотаций блоков.

Сконфигурируйте выбор решателя Simulink для дискретной симуляции с фиксированным шагом; это необходимо для операции косимуляции. Выполните следующие действия:

В Modeling tab нажмите Model Settings. Откроется диалоговое окно Model Configuration Parameters, в котором отобразится панель Solver selection.

Выберите Fixed-step из Type меню.

Выберите discrete (no continuous states) из Solver меню.

Нажмите Apply.

Нажмите кнопку OK, чтобы закрыть диалоговое окно Model Configuration Parameters.

Смотрите Модель Set Simulink Параметров конфигурации для получения дополнительной информации о настройках Simulink, которые оптимальны для использования с программным обеспечением HDL Verifier.

Сохраните модель.

Теперь у вас есть представление VHDL инвертора и модель Simulink, которая применяет инвертор. Чтобы запустить ModelSim таким образом, чтобы он был готов к использованию с Simulink, введите следующую командную строку в Командном окне MATLAB:

vsim('socketsimulink', 4449)

Примечание

Если при конфигурировании блока HDL Cosimulation в Simulink вы ввели другую спецификацию порта сокета, замените номер порта 4449 в предыдущей командной строке на применимую информацию порта сокета для вашей модели. vsim функция информирует ModelSim о сокете TCP/IP, который будет использоваться для установления ссылки связи с вашей моделью Simulink.

В этом разделе описывается, как использовать vsimulink Команда для загрузки образца VHDL- сущности для косимуляции с Simulink. vsimulink команда является вариантом HDL Verifier ModelSim vsim команда. Он становится доступным как часть строения ModelSim.

Загрузка образца inverter сущность, выполните следующие действия:

Измените вход особого внимания в окне ModelSim.

Если вашего файл VHD нет в текущей папке, измените папку на расположение вашего inverter.vhd файл. Для примера:

ModelSim> cd C:/MyPlayArea

Введите следующее vsimulink команда:

ModelSim> vsimulink work.inverter

ModelSim запускает vsim симулятор таким образом, что он готов моделировать сущность inverter в контексте вашей модели Simulink. Отображение командного окна ModelSim должно быть подобно следующему.

В этом разделе рассматриваются сценарии выполнения и мониторинга сеанса косимуляции.

Выполните следующие действия:

Откройте и добавьте сигналы инвертора в wave окно путем ввода следующей команды ModelSim:

VSIM n> add wave /inverter/*

Появится следующее wave окно.

Измените вход особого внимания в окне модели Simulink.

Запустите симуляцию Simulink. Значение в блоке Display изменяется на 255. Также обратите внимание на изменения, которые происходят в окне wave ModelSim. Вам, возможно, потребуется увеличить масштаб, чтобы получить лучшее представление данных о сигнале.

В модели Simulink смените Constant value на 255сохраните модель и запустите другую симуляцию. Значение в блоке Display изменяется на 0 и окно ModelSim wave обновляется следующим образом.

В модели Simulink смените Constant value на 2 и Sample time до 20 и запустите другую симуляцию. На этот раз значение в блоке Display меняется на 253 и окно ModelSim wave появится как показано на следующем рисунке.

Обратите внимание на изменение шага расчета в wave окне.

В этом разделе описывается, как отключить симуляцию упорядоченным способом, следующим образом:

В ModelSim остановите симуляцию, выбрав Simulate > End Simulation.

Выход из ModelSim.

Закройте окно модели Simulink.