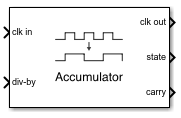

Делитель синхроимпульса, который делит частоту входного сигнала на дробное число

Blockset смешанного сигнала/PLL/Building блоки

Блок Fractional Clock Divider with Accumulator делит частоту входного сигнала на настраиваемое дробное значение (N. FF). Если сравнивать с блоком Single Modulus Prescaler, блок Fractional Clock Divider with Accumulator помогает достичь узкого интервала между каналами, которое может быть меньше, чем опорная частота системы фазовой автоподстройки (ФАП).

[1] Лучший, Roland E. Фазовая автоподстройка Цикла. Нью-Йорк, Нью-Йорк: Tata McGraw-Hill Companies Inc., 2003.

Dual Modulus Prescaler | Fractional Clock Divider with DSM | PFD | Single Modulus Prescaler | VCO