Используя SoC- Blockset™, можно смоделировать в своей модели упрощенный, потоковый протокол. Используйте HDL- Coder™ для генерации AXI4-Stream интерфейсов в ядре IP.

Когда вы хотите сгенерировать AXI4-Stream интерфейс в вашем IP-ядре, в вашем интерфейсе DUT реализуйте следующие сигналы:

Данные

Действительный

Когда вы сопоставляете скалярные порты DUT с AXI4-Stream интерфейсом, можно опционально смоделировать следующие сигналы и сопоставить их с AXI4-Stream интерфейсом:

Готов

Другие сигналы протокола, такие как:

TSTRB

TKEEP

TLAST

TID

TDEST

TUSER

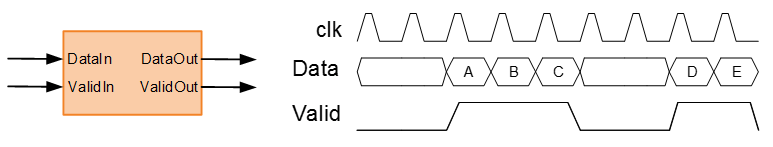

Когда сигнал данные действителен, задается сигнал Valid.

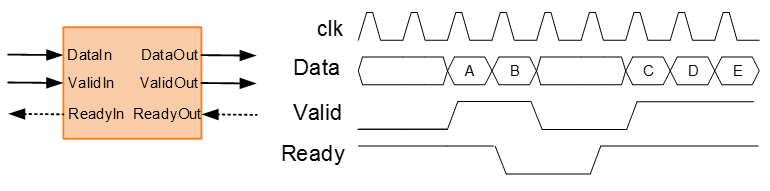

Интерфейсы AXI4-Stream в DUT могут опционально включать сигнал Ready. В подчиненном интерфейсе сигнал Ready позволяет применить обратные давления. В главном интерфейсе сигнал Ready позволяет вам реагировать на обратные давления.

Если вы моделируете сигнал Ready в интерфейсах AXI4-Stream, ваш главный интерфейс игнорирует сигналы данные и Valid через один такт после отключения сигнала Ready. Вы можете начать отправлять данные и Valid, как только сигнал Ready будет утвержден. Вы можете отправить еще один сигнал Data and Valid после отключения сигнала Ready.

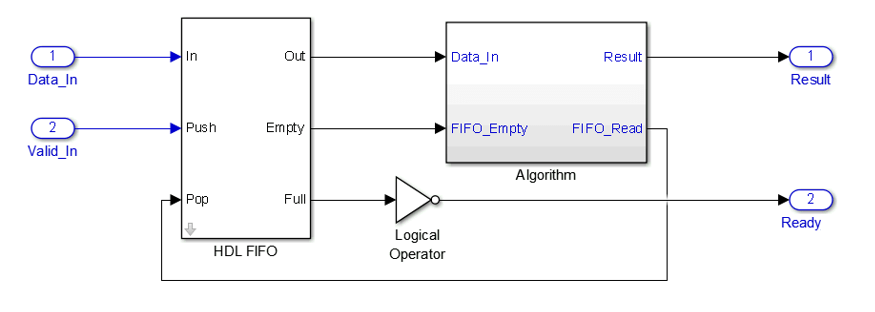

Если вы не моделируете сигнал Ready, HDL Coder генерирует сигнал и связанную логику давления.

Для примера, если в вашем DUT есть FIFO для хранения системы координат данных, для применения обратного давления к вышестоящему компоненту, можно смоделировать сигнал Ready на основе сигнала FIFO Full.

Memory Channel | SoC Bus Creator