Для проектов, которые требуют доступа к большим наборам данных из внешней памяти, моделируйте ваш алгоритм с помощью упрощенного протокола AXI4 Master. Когда вы запускаете IP Core Generation рабочий процесс, HDL Coder™ генерирует IP-ядро с AXI4 интерфейсами Master. Интерфейс AXI4 Master может обмениваться данными между вашим проектом и IP-адресом внешнего контроллера памяти с помощью протокола AXI4 Master.

Можно использовать упрощенный протокол AXI4 Master для сопоставления с AXI4 интерфейсами Master. Используйте упрощенный протокол записи AXI4 Master для транзакции записи и упрощенный протокол чтения AXI4 Master для транзакции чтения.

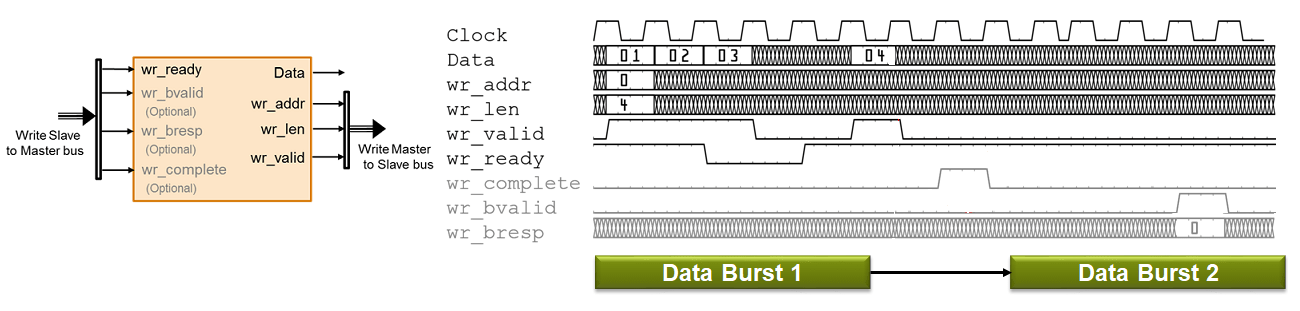

Этот рисунок показывает временную диаграмму для сигналов, которые вы моделируете во входном и выходном интерфейсах DUT для транзакции записи AXI4 Master.

DUT ждет wr_ready чтобы стать высоким, чтобы инициировать запрос на запись. Когда wr_ready становится высоким, DUT может отправить запрос на запись. Запрос на запись состоит из Data и Write Master to Slave bus сигналы. Эта шина состоит из wr_len, wr_addr, и wr_valid. wr_addr задает начальный адрес, по которому DUT хочет записать. The wr_len сигнал соответствует количеству элементов данных в этой транзакции записи. Data может быть отправлен до тех пор, пока wr_valid высоко. Когда wr_ready становится низким, DUT должен прекратить отправку данных в течение одного такта, и Data сигнал становится недопустимым. Если DUT продолжает отправлять данные после одного такта, данные игнорируются.

Упрощенный AXI4 Master Protocol поддерживает конвейерные запросы, поэтому ждать wr_complete не требуется сигнал должен быть высоким перед выдачей последующего запроса на запись. Интерфейс поддерживает до 16 транзакций (или 16 слов данных) перед застопориванием трубопровода и wr_ready сигнал падает.

Выходные сигналы

Моделируйте Data и Write Master to Slave bus сигналы на выходном интерфейсе DUT.

Data: Данные, которые вы хотите перенести, действительны каждый цикл транзакции.

Write Master to Slave bus который состоит из:

wr_addr: Начальный адрес транзакции записи, выбранной в первом цикле транзакции. Адрес указан в байтах.

wr_len: Количество значений данных, которые вы хотите перенести, выбранных в первом цикле транзакции. The wr_len сигнал указан в словах.

wr_valid: Когда этот сигнал управления становится высоким, это указывает, что Data сигнал, дискретизированный на выходе, действителен.

Входные сигналы

Моделируйте Write Slave to Master bus который состоит из:

wr_ready: Этот сигнал соответствует противодавлению от ведомого ядра IP или внешней памяти. Когда этот сигнал управления становится высоким, это указывает, что данные могут быть sent. когда wr_ready низкий, DUT должен прекратить отправку данных в течение одного такта. Можно также использовать wr_ready сигнал для определения, может ли DUT послать второй сигнал пакетной передачи сразу после того, как первый сигнал пакетной передачи был отправлен. Поддерживаются несколько сигналов пакетной передачи, что означает, что wr_ready сигнал остается высоким, чтобы принять второй пакет сразу после принятия последнего элемента первого пакета.

wr_bvalid (необязательный сигнал): Ответный сигнал от ведомого IP-ядра, который можно использовать в целях диагностики. The wr_bvalid сигнал становится высоким после того, как AXI4 соединитель принимает каждую пакетную транзакцию. Если wr_len больше 256модуль записи AXI4 Master разделяет сигнал большого пакета на пакеты 256 размера. wr_bvalid становится высоким для каждого пакета 256 размеров.

wr_bresp (необязательный сигнал): Ответный сигнал от ведомого IP-ядра, который можно использовать в целях диагностики. Используйте этот сигнал с wr_bvalid сигнал.

wr_complete (необязательный сигнал): Управляющий сигнал, который, когда остается высоким в течение одного такта, указывает, что транзакция записи завершена. Этот сигнал утверждает на последнем wr_bvalid всплеска.

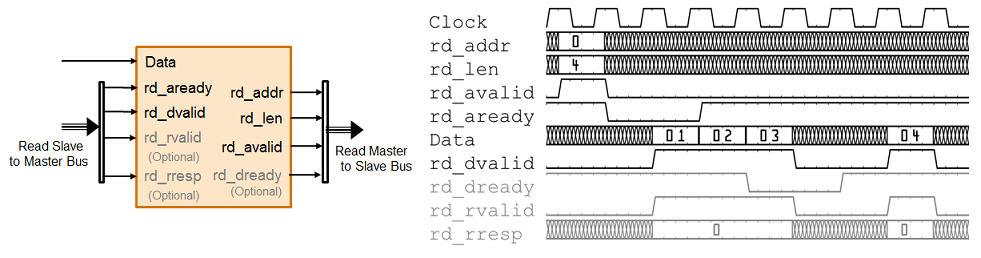

Этот рисунок показывает временную диаграмму для сигналов, которые вы моделируете во входном и выходном интерфейсах DUT для транзакции чтения AXI4 Master. Эти сигналы включают в себя Data, Read Master to Slave Bus, и Read Slave to Master Bus.

DUT ждет rd_aready чтобы стать высоким, чтобы инициировать запрос на чтение. Когда rd_aready высоко, DUT может послать вне запрос чтения. Запрос на чтение состоит из rd_addr, rd_len, и rd_avalid сигналы Read Master to Slave bus. Ведомый IP или внешняя память отвечают на запрос чтения, отправляя Data в каждом такте. The rd_len сигнал соответствует количеству считываемых значений данных. DUT может принимать Data пока rd_dvalid высоко.

Чтение запроса

Чтобы смоделировать запрос на чтение, в выходном интерфейсе DUT моделируйте Read Master to Slave bus который состоит из:

rd_addr: Начальный адрес для считанной транзакции, выбранной в первом цикле транзакции. Адрес указан в байтах.

rd_len: Количество значений данных, которые вы хотите считать, выбранных в первом цикле транзакции. The rd_len сигнал указан в словах.

rd_avalid: Управляющий сигнал, который определяет, является ли запрос чтения допустимым.

На входном интерфейсе DUT реализуйте rd_aready сигнал. Этот сигнал является частью Read Slave to Master bus и указывает, когда принимать запросы на чтение. Можно контролировать rd_aready сигнал для определения, может ли DUT посылать последовательные пакетные запросы. Когда rd_aready становится высоким, это указывает, что DUT может послать запрос на чтение в следующем такте.

Упрощенный главный протокол AXI4 поддерживает конвейерные запросы, поэтому перед отправкой последующего запроса на чтение не требуется ждать завершения ответа на чтение. Интерфейс поддерживает до 4 транзакций чтения перед застопориванием трубопровода и rd_aready сигнал падает.

Чтение ответа

В входе DUT моделируйте Data и Read Slave to Master bus сигналы.

Data: Данные, которые возвращаются из запроса на чтение.

Read Slave to Master bus который состоит из:

rd_dvalid: Управляющий сигнал, который указывает, что Data возвращен из запроса на чтение.

rd_rvalid (необязательный сигнал): сигнал отклика от ведомого IP ядра, который можно использовать в целях диагностики.

rd_rresp (необязательный сигнал): Ответный сигнал от ведомого IP-ядра, который указывает на состояние считанной транзакции.

В выходном интерфейсе DUT можно опционально реализовать rd_dready сигнал. Этот сигнал является частью Read Master to Slave bus и указывает, когда DUT может начать принимать данные. По умолчанию, если вы не сопоставляете этот сигнал с интерфейсом чтения AXI4 Master, сгенерированное ядро HDL IP связывает rd_dready к логике высокий.

Memory Channel | SoC Bus Creator