Вы можете использовать socExportReferenceDesign функция, чтобы сгенерировать исходный проект из модели SoC Blockset™ и избежать ручных шагов, необходимых для генерации и регистрации пользовательского исходного проекта. Функция генерирует эти программные продукты.

Файлы регистрации платы

Исходный проект

IP-репозиторий

Проект файлов

Файлы ограничений

Модели SoC могут быть одним из таких типов.

Однокристальная Модель с FPGA, памятью и дополнительными вводами-выводами (без процессора)

Однокристальная Модель с процессором, FPGA, памятью и дополнительными вводами-выводами

При экспорте пользовательского исходного проекта из модели SoC исходного проекта не включает тестируемый проект (DUT), и интерфейс к DUT доступен. После генерации исходного проекта можно интегрировать пользовательский IP-адрес с помощью инструмента HDL Workflow Advisor. Ваш пользовательский IP должен иметь тот же интерфейс, что и блок Алгоритма FPGA.

Чтобы экспортировать пользовательский исходный проект, сначала создайте модель SoC, чтобы смоделировать систему и вводы-выводы, доступные на вашей плате. Чтобы создать модель SoC Blockset, используйте один из следующих методов.

Создайте модель с помощью шаблона SoC Blockset (рекомендуемый). Для получения дополнительной информации смотрите Использование шаблона для создания модели СО.

Создайте модель SoC с нуля. Для получения дополнительной информации см. Раздел «Создание приложения для однокристального проекта».

Включите подсистему DUT в модель. Эта подсистема должна иметь тот же интерфейс, что и ядро IP, которое вы разрабатываете. Поскольку сгенерированный исходный проект не включает подсистему DUT, DUT может быть простой моделью или просто сквозным блоком.

Можно использовать MATLAB в качестве основной функции AXI в экспортированном исходном проекте для взаимодействия с однокристальным устройством из хоста. В Simulink®Откройте диалоговое окно Параметры конфигурации (Configuration Parameters), нажав Настройки модели (Model Settings) на вкладке Моделирование (Modeling), и на левой панели выберите Hardware Implementation. Затем разверните Target hardware resources, выберите FPGA design (top-level), а затем выберите Include 'MATLAB AXI Master' IP for host-based interaction.

В IP core clock frequency (MHz) окне укажите тактовую частоту ядра IP в МГц.

Чтобы убедиться, что ваша модель SoC поддерживает генерацию кода, используйте инструмент SoC Builder, чтобы сгенерировать исполняемые файлы и развернуть вашу модель. Для получения дополнительной информации об инструменте SoC Builder см. Раздел «Генерация проекта СнК».

Пример, показывающий этот рабочий процесс только в случае FPGA, см. в разделе Экспорт пользовательского исходном проекте.

Дерево устройств (DT) является структурой данных, которая описывает оборудование для операционной системы. Когда вы добавляете IP к проекту, вы должны сгенерировать новое дерево устройств, чтобы операционная система могла получить доступ к IP.

Если ваша модель содержит подсистемы FPGA и процессора, эти дополнительные шаги требуются перед экспортом исходного проекта.

В параметрах конфигурации нажмите Hardware Implementation слева. Затем разверните Target hardware resources и выберите Include processing system в FPGA design (top-level).

Запустите инструмент SoC Builder, следуйте направленным шагам для генерации кода, а затем загрузите двоичные файлы в FPGA. Этот шаг необходим, потому что SoC Builder автоматически генерирует файл дерева устройств (.dtb) на SD-карте с именем hdlcoder_rd/soc_prj.output.dtb и модель ПО с совпадающими именами устройств.

Скопируйте файл дерева устройства из папки hdlcoder_rd в корневую папку карты SD. В сгенерированной plugin_rd.m файл дерева пользовательского устройства задается как:

hRD.DeviceTreeName = 'soc_prj.output.dtb';

socExportReferenceDesign ФункцияЭкспортируйте пользовательский исходный проект для модели с помощью socExportReferenceDesign функция. Для примера, для модели с именем soc_image rotation, введите этот код в MATLAB® командная строка.

socExportReferenceDesign('soc_image_rotation')Функция генерирует эти программные продукты в текущей папке.

Файлы регистрации платы

Исходный проект

IP-репозиторий

Проект файлов

Файлы ограничений

Добавьте сгенерированную папку в путь MATLAB. Используйте инструмент HDL Workflow Advisor, чтобы провести вас через шаги для интеграции IP и генерации оборудования и программных исполняемых файлов для развертывания на однокристальном устройстве.

Пример, показывающий полный рабочий процесс только в случае FPGA, см. в разделе Экспорт пользовательского исходном проекте. Если ваша модель включает систему обработки, эти дополнительные шаги требуются при использовании инструмента HDL Workflow Advisor.

В Simulink щелкните правой кнопкой мыши блок DUT, который необходимо интегрировать в исходный проект, и выберите HDL Code > HDL Workflow Advisor, чтобы открыть инструмент HDL Workflow Advisor. Кроме того, используйте hdladvisor (HDL Coder) функция.

На шаге 1.1 установите Target workflow равным IP Core Generation и Target platform к платформе, сгенерированной socExportReferenceDesign функция.

Щелкните Run This Task, чтобы запустить Set Target Device and Synthesis Tool задачу.

На шаге 1.3 установите целевой интерфейс путем подключения каждого порта в вашем IP к соответствующему порту в исходный проект.

Щелкните Run This Task, чтобы запустить Set Target Interface задачу.

Продолжите оставшиеся шаги инструмента HDL Workflow Advisor.

Необязательно: На шаге 4.2 можно принять решение сгенерировать модель программного интерфейса с блоками драйверов ядра IP (требует Embedded Coder® лицензия). Если вы принимаете решение сгенерировать эту модель интерфейса программного обеспечения, очистите Skip this task под Generate a software interface model with IP core driver blocks for C code generation.

Для получения дополнительной информации смотрите раздел «Генерация модели интерфейса программного обеспечения» в Начало Работы with Targeting Xilinx Zynq Platform (HDL Coder).

Сгенерированное программное обеспечение содержит блоки драйверов AXI, которые совпадают с интерфейсом подсистемы DUT. Для имени устройства задано значение '/dev/mwipcore' по умолчанию. Измените имя устройства в этих блоках драйверов AXI так, чтобы оно совпадало с именем в древовидном файле устройства, используемом изображением карты SD.

Существует несколько способов найти имя устройства:

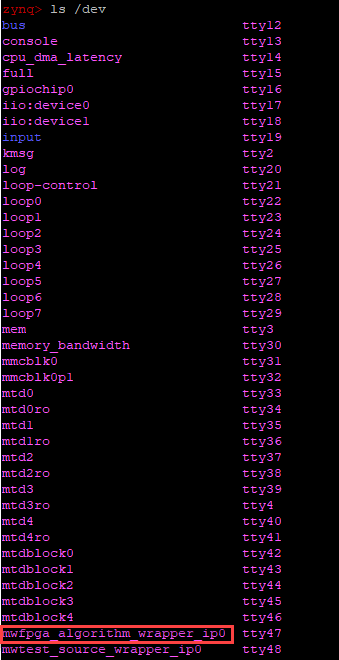

Имя устройства определяется как DUT-имя модели SoC. Если вы экспортируете исходный проект с помощью модели SoC с именем DUT, заданным как 'soc_hwsw_stream_fpga/FPGA Algorithm Wrapper', имя сгенерированного устройства в блоках драйверов AXI '/dev/mwfpga_algorithm_wrapper_ip0'.

Найдите имя устройства в изображении операционной системы (OS) после загрузки устройства СО. Для этого войдите на плату с помощью протоколов UART или SSH и выполните:

ls/dev

На шаге 4.4 установите метод программирования на Download.

Когда инструмент HDL Workflow Advisor завершен, он возвращает сгенерированный файл битового потока. Программируйте FPGA с сгенерированным файлом битового потока.

Теперь можно развернуть модель программного интерфейса в автономном режиме или использовать ее во режиме external mode для взаимодействия с однокристальным устройством. Для получения примера смотрите раздел «Запуск модель программного интерфейса на оборудовании Zynq ZC702» в Начало работы с Targeting Xilinx Zynq Platform (HDL Coder).