Сгенерируйте контрольную сумму и добавьте к входному потоку выборки

Беспроводной HDL Toolbox/Обнаружение и коррекция ошибок

Блок LTE CRC Encoder вычисляет и добавляет контрольную сумму циклического контроля избыточности (CRC) для каждой системы координат потоковых выборок данных. Можно выбрать из полиномов, заданных стандартом LTE TS 36.212 [1]. Блок обеспечивает аппаратно оптимизированную архитектуру и интерфейс.

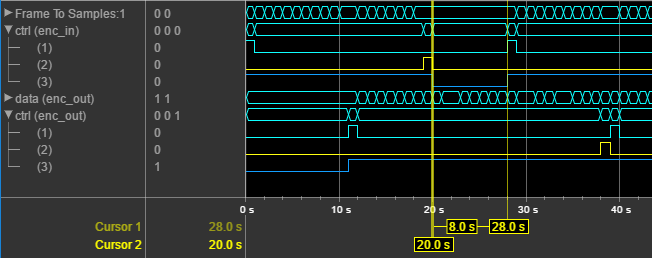

Этот блок использует интерфейс потоковой выборки с шиной для связанных сигналов управления. Этот интерфейс позволяет блоку работать независимо от формата кадра и легко соединяться с другими блоками Toolbox™ Wireless HDL. Блок принимает и возвращает значение, представляющее одну выборку, и шину, содержащую три сигнала управления. Эти сигналы указывают валидность каждой выборки и контуров системы координат. Чтобы преобразовать матрицу в поток сэмплирования и эти сигналы управления, используйте блок Frame To Samples или whdlFramesToSamples функция. Полное описание интерфейса см. в разделе Потоковый пример интерфейса.

Нельзя применять другую систему координат до завершения предыдущей системы координат. Аппаратный алгоритм добавляет (CRCLength + 3)/InputSize циклы задержки. Чтобы учесть дополнительные циклы добавленных выборок контрольной суммы и задержку, необходимо применить минимальный интервал (2*CRCLength + 3)/InputSize между входными кадрами. Также можно использовать выход сигнала ctrl end. чтобы определить, когда блок готов к новому входу. Если применить следующую систему координат слишком рано, ctrl start. сигнал сбрасывает вычисление контрольной суммы и обрезает предыдущую систему координат.

Эта форма волны показывает систему координат с 40 выборками, вводит две выборки за раз в CRC16 энкодер. Поэтому зазор между входными кадрами составляет 8 циклов. Из-за вставки контрольной суммы выход ctrl valid. сигнал остается непрерывно высоким без зазоров между системами координат. Входная и выходная шины ctrl расширены, чтобы показать сигналы управления. start и end показать контуры кадра и valid определяет выборки данных.

[1] 3GPP TS 36.212. «Мультиплексирование и канальное кодирование». 3rd Генерация Partnership Project; Группа технических спецификаций Radio Доступа Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL-адрес: https://www.3gpp.org.

[2] Кампобелло, Джузеппе, Джузеппе Патане и Марко Руссо. «Параллельная реализация CRC». Транзакции IEEE на компьютерах. Том 52, № 10, октябрь 2003, стр. 1312-1319.