Декодируйте сверточно закодированные данные с использованием алгоритма Viterbi

Беспроводной HDL Toolbox/Обнаружение и коррекция ошибок

Блок Viterbi Decoder декодирует сверточно закодированные данные с помощью реализации отслеживания на основе ОЗУ. Декодирование Viterbi широко используется в стандарте LTE TS 36.212 [1] и других приложениях прямой коррекции ошибок (FEC), таких как беспроводные сети (802.11a/b/g/n/ac), цифровая спутниковая связь, цифровая видеотрансляция (DVB), IEEE 802.16 и HiperL Чтобы поддержать любой из этих стандартов, блок принимает коды свертки с длинами ограничений от 3 до 9, скоростями кода от 1/2 до 1/7 и обеспечивает непрерывный, оконечный и усеченный режимы. Блок обеспечивает архитектуру и интерфейс, подходящие для генерации HDL-кода.

Блок поддерживает декодирование проколотых кодов путем предоставления опционального erasure входного порта. Можно использовать блок Depuncturer, чтобы вставить нейтральные значения в проколотый поток сэмплирования и сгенерировать сигнал erasure.

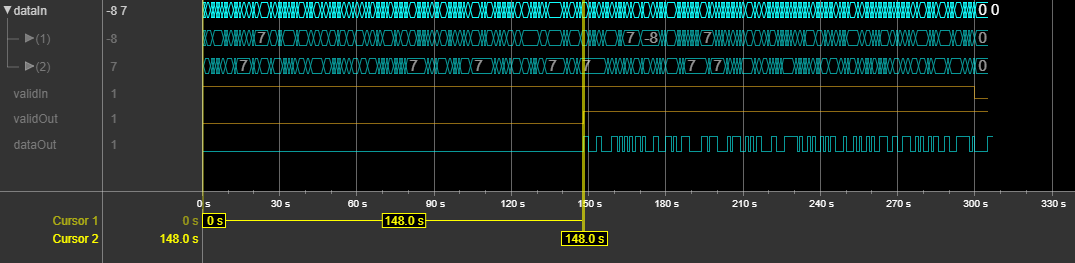

Блок Viterbi Decoder принимает входные выборки как двоичные значения с твердым решением или коэффициенты логарифмической вероятности мягкого решения (LLR). Каждая выборка является вектором-столбцом, длина которой зависит от схемы кодирования. Первая форма волны показывает непрерывный режим работы с входными выборками подписанных 4-битных данных, используя параметры блоков по умолчанию. Это Traceback depth 32. Блок возвращает первую декодированный выход данных после 148 тактов. Задержка декодирования составляет 4 × Traceback depth + Constraint length + 13 допустимых входных циклов.

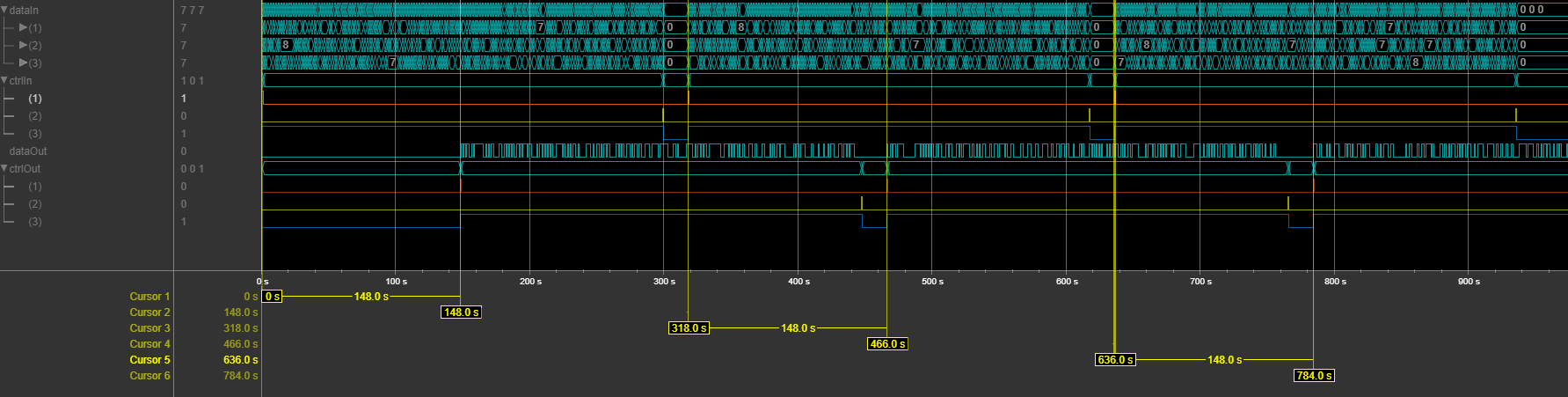

Вторая форма волны показывает три системы координат в режиме завершения операции. Этот вход представляет собой беззнаковые 4-битные выборки, и блок использует шпалеру (7, [171 133 112]). Это Traceback depth 32. Входная и выходная шины ctrl расширены, чтобы показать свои три управляющих сигнала. Задержка от каждого входа ctrl start. для вывода ctrl. start также 148 тактов.

Сигналы управления в шине указывают валидность каждой выборки и контуров системы координат. Чтобы преобразовать матрицу в поток сэмплирования и соответствующие сигналы управления, используйте блок Frame To Samples или whdlFramesToSamples функция. Полное описание потокового примера интерфейса смотрите в Потоковый пример интерфейса.

[1] 3GPP TS 36.212. «Мультиплексирование и канальное кодирование». 3rd Генерация Partnership Project; Группа технических спецификаций Radio Доступа Network; Evolved Universal Terrestrial Radio Access (E-UTRA). URL-адрес: https://www.3gpp.org.

[2] Хорвиц, М. и Р. Браун. «Обобщенный метод проекта для управления памятью выжившего после трассировки в декодерах Viterbi». Материалы Южноафриканского симпозиума 1997 года по связи и обработке сигналов: 63-68. Piscataway, NJ: IEEE, 1997.

[3] Shung, C.b., P.H. Зигель, Г. Унгербоек и Х.К. Тапар. «VLSI Архитектур для метрической нормализации в Алгоритм Viterbi». Международная конференция IEEE по коммуникациям, включая технические сеансы суперкомм: том 4. 1726-728. Нью-Йорк, Нью-Йорк: IEEE, 1990.