Когда вы запускаете типовой рабочий процесс Генерации Ядра IP для своего Simulink® модель или цель ваш собственный исходный проект, который вы создали, можно сгенерировать ядро IP HDL с несколькими AXI4-потоковыми интерфейсами, AXI4-потоковыми Видеоинтерфейсами или Основными интерфейсами AXI4. Чтобы узнать об этих интерфейсах, смотрите Интерфейсы Целевой платформы.

Можно использовать несколько интерфейсов потоковой передачи, чтобы упростить высокоскоростную передачу данных в различных приложениях, таких как:

Передача данных между A/D и цифро-аналоговыми преобразователями

Программно определяемые радио-алгоритмы, что процесс несколько каналов приемопередатчика

Алгоритмы визуализации, которые выполняют аннотацию изображений или обнаружение объектов

Задавать больше чем один AXI4-поток, AXI4-потоковое Видео или Основной канал AXI4:

В задаче Set Target Device and Synthesis Tool выберите IP Core Generation как Target workflow и Generic Xilinx Platform или Generic Altera Platform как Target platform. Запустите эту задачу.

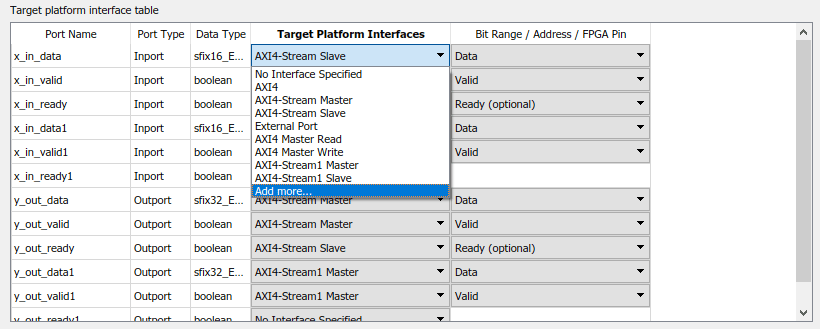

Чтобы добавить несколько целевых интерфейсов, в задаче Set Target Interface, на разделе Target Platform Interfaces таблицы интерфейса Целевой платформы, выбирают Add more ....

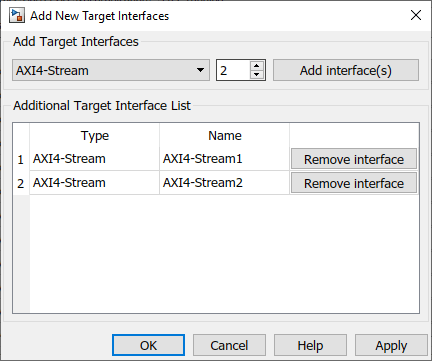

Можно затем добавить больше интерфейсов в диалоговом окне Add New Target Interfaces. Задайте тип интерфейса, который вы хотите добавить, количество интерфейсов и пользовательское имя для каждого дополнительного интерфейса.

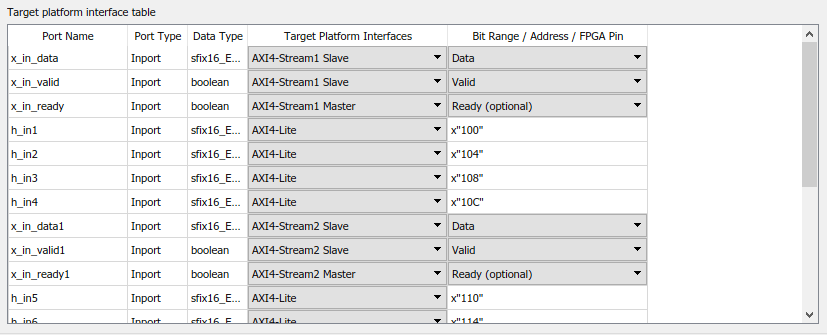

После того, как вы применяете настройки, интерфейсы, которые вы создали, появляются в таблице интерфейса Целевой платформы. После того, как вы запустите эту задачу, дополнительные заданные интерфейсы сохранены на подсистеме DUT как свойство AdditionalTargetInterfaces блока HDL.

Если вы изменяете дополнительные интерфейсы, которые были уже сопоставлены с портами DUT, такими как удаление или переименование интерфейса, который был уже сопоставлен, предыдущая информация об отображении интерфейса может быть потеряна. Порты затем становятся несопоставленными с интерфейсами, и раздел Target platform interfaces отображает No interface specified. Поэтому, если вы вносите изменения в дополнительные целевые интерфейсы, проверяете, что порты DUT сопоставлены с правильными целевыми интерфейсами.

Когда вы создаете свой собственный исходный проект, можно добавить несколько AXI4-поток, AXI4-потоковое Видео и Основные интерфейсы AXI4. В зависимости от интерфейсного типа вы хотите добавить, задать дополнительные интерфейсы при помощи addAXI4StreamInterface, addAXI4StreamVideoInterface, или addAXI4MasterInterface методы hdlcoder.ReferenceDesign класс.

Добавить больше интерфейсов, в plugin_rd файл, вызовите метод интерфейса каждый раз, когда вы хотите добавить больше интерфейсов. В этом примере показано, как добавить два AXI4-потоковых интерфейса.

function hRD = plugin_rd() % Reference design definition % Copyright 2017-2019 The MathWorks, Inc. % Construct reference design object hRD = hdlcoder.ReferenceDesign('SynthesisTool', 'Xilinx Vivado'); hRD.ReferenceDesignName = 'Multiple Interface Reference Design'; hRD.BoardName = 'ZedBoard'; % Tool information hRD.SupportedToolVersion = {'2019.1'}; % ... % ... % Add AXI4-Stream interface 1 hRD.addAXI4StreamInterface (... 'MasterChannelEnable', true, ... 'SlaveChannelEnable', true, ... 'MasterChannelConnection', 'axi_dma_s2mm/S_AXIS_S2MM', ... 'SlaveChannelConnection', 'axi_dma_mm2s/M_AXIS_MM2S', ... 'MasterChannelDataWidth', 32, ... 'SlaveChannelDataWidth', 32, ... 'InterfaceID', 'AXI4-Stream1'); % Add AXI4-Stream interface 2 hRD.addAXI4StreamInterface (... 'MasterChannelEnable', true, ... 'SlaveChannelEnable', true, ... 'MasterChannelConnection', 'ADC/S_AXIS_S2MM', ... 'SlaveChannelConnection', 'DAC/M_AXIS_MM2S', ... 'MasterChannelDataWidth', 32, ... 'SlaveChannelDataWidth', 32, ... 'InterfaceID', 'AXI4-Stream2'); % ... % ...

Когда вы запускаете IP Core Generation рабочий процесс и цель пользовательский исходный проект Multiple Interface Reference Design, в задаче Set Target Interface можно сопоставить порты DUT с Основными и Ведомыми каналами AXI4-Stream1 и Основными и Ведомыми каналами AXI4-Stream2.

Примечание

Когда вы предназначаетесь для своего собственного исходного проекта и сопоставляете дополнительные интерфейсы с портами DUT в задаче Set Target Interfaces, дополнительные интерфейсы не сохранены на модели как свойство блока AdditionalTargetInterfaces HDL. Вместо этого дополнительные интерфейсы сохранены на пользовательском исходном проекте в plugin_rd.m файл.

Можно также динамически настроить исходный проект, чтобы задать количество интерфейсов, которые вы хотите добавить и интерфейсные свойства.

В plugin_rd файл, создайте параметр исходного проекта для количества дополнительных интерфейсов, которые вы хотите добавить.

Создайте функцию обратного вызова, которая имеет различный выбор для количества интерфейсов, вы хотите добавить и затем сослаться на функцию в plugin_rd файл при помощи CustomizeReferenceDesignFcn метод hdlcoder.ReferenceDesign класс.

Чтобы узнать больше, смотрите, Настраивают Исходный проект Динамически На основе Параметров Исходного проекта.

Когда вы используете один канал потоковой передачи, HDL Coder™ автоматически генерирует Готовый сигнал и связанную логику противодавления.

Если вы используете несколько каналов потоковой передачи, HDL Coder автоматически не генерирует логику противодавления. В этом случае Готовый сигнал сгенерирован, но основной Готовый сигнал во входе проигнорирован, и ведомый Готовый сигнал при выходе связывается к высокому значению. Отсутствие логики противодавления может привести к пропускаемым выборкам. Если вы хотите, чтобы ваш проект применил противодавление на интерфейс Slave или ответил на противодавление от интерфейса Master, необходимо смоделировать Готовый сигнал для каждого дополнительного интерфейса и затем сопоставить порт с Готовым сигналом для того интерфейса. Когда вы не моделируете, задача Set Target Interface выводит предупреждение, которое обеспечивает имена интерфейсов, которые требуют порта Ready. Если ваш проект не должен применить или ответить на противодавление, можно проигнорировать это предупреждение, и вы не должны моделировать Готовый сигнал.

При использовании нескольких AXI4-потоковых интерфейсов, если вы хотите, чтобы ваш проект применил противодавление на интерфейс Slave или ответил на противодавление от интерфейса Master, необходимо смоделировать Готовый сигнал для каждого дополнительного интерфейса и затем сопоставить порт с Готовым сигналом для того интерфейса. Чтобы изучить, как логика противодавления сгенерирована для одного канала потоковой передачи и как смоделировать Готовый сигнал, смотрите Готовый Сигнал (Необязательно).

Когда вы запускаете типовой рабочий процесс Генерации Ядра IP, можно задать интерфейсный тип и пользовательский интерфейс ID для каждого дополнительного интерфейса. Другие интерфейсные свойства, такие как ширина данных не могут быть настроены и значения по умолчанию использования. Когда вы создаете свой собственный исходный проект, можно настроить интерфейсное имя и соединить интерфейсом со свойствами.

При отображении портов DUT с несколькими каналами интерфейса AXI4-Stream можно только использовать скалярные порты. Векторные порты могут иметь самое большее один AXI4-потоковый Ведущий канал и один AXI4-потоковый Ведомый канал.

Xilinx® Zynq®- 7000 или Intel® Куарт® Главный должна быть ваша целевая платформа.

Processor/FPGA synchronization должен быть Free running.

Xilinx Vivado® или Intel Куарт Прайм должен быть вашим инструментом синтеза.