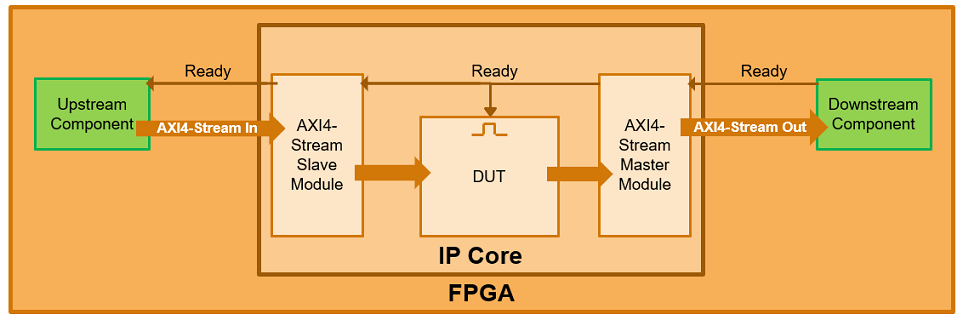

С программным обеспечением HDL Coder™ можно реализовать упрощенный, передающий потоком протокол в модели. Программное обеспечение генерирует AXI4-потоковые интерфейсы в ядре IP.

Чтобы сопоставить порты проекта под тестом (DUT) с AXI4-потоковыми интерфейсами, используйте упрощенный AXI4-потоковый протокол. Вы не должны моделировать фактический AXI4-потоковый протокол, и вместо этого можно использовать упрощенный протокол. Когда вы запускаете IP Core Generation рабочий процесс, сгенерированный HDL-код содержит логику обертки, которая переводит между упрощенным протоколом и фактическим AXI4-потоковым протоколом. Упрощенный протокол требует меньшего количества сигналов протокола, упрощает механизм квитирования между допустимыми и готовыми сигналами и поддерживает пакеты произвольных длин.

Используйте упрощенный AXI4-потоковый протокол для записи и считайте транзакции. Когда это необходимо, чтобы сгенерировать интерфейс AXI4-Stream в вашем ядре IP, в вашем интерфейсе DUT, реализуют следующие сигналы:

Данные

Допустимый

Опционально, когда вы сопоставляете скалярные порты DUT с интерфейсом AXI4-Stream, можно смоделировать следующие сигналы:

Готовый

Другие сигналы протокола, такие как:

TSRTB

TKEEP

TLAST

TID

TDEST

TUSER

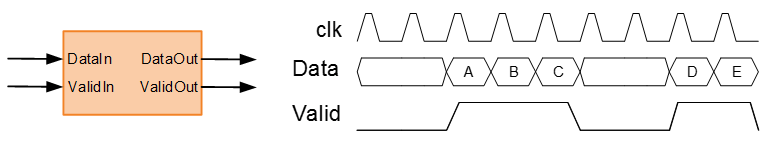

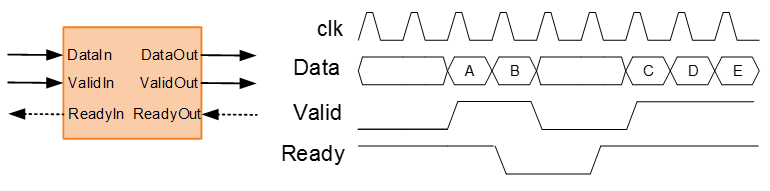

Когда сигнал Данных допустим, Допустимый сигнал утверждается. Эта схема иллюстрирует Данные и Допустимое отношение сигнала согласно упрощенному протоколу потоковой передачи. Когда вы запускаете рабочий процесс генерации ядра IP, HDL Coder добавляет модуль интерфейса потоковой передачи в ядре IP HDL, которое переводит упрощенный протокол в полный AXI4-потоковый протокол. В этой схеме сигнал часов представлен clk.

Когда это необходимо, чтобы симулировать данные сигнализируют как поток выборок на контуре DUT, модели в основанном на выборке режиме. В основанном на выборке режиме можно смоделировать сигнал данных или как скаляр или как вектор. Если вы моделируете сигнал данных как вектор, устанавливаете Демонстрационную Размерность Упаковки на Все. В сгенерированном HDL-коде векторные элементы упаковываются вместе, и целый вектор обработан как одна выборка. Можно задать, как данные упаковываются при помощи Режима Упаковки. Смотрите Демонстрационную Размерность Упаковки.

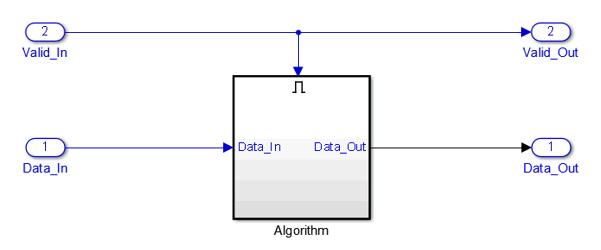

Заключите алгоритм, который обрабатывает сигнал Данных при помощи активированной подсистемы.

Управляйте разрешать портом активированной подсистемы при помощи Допустимого сигнала.

Например, можно непосредственно соединить Допустимый сигнал с разрешать портом.

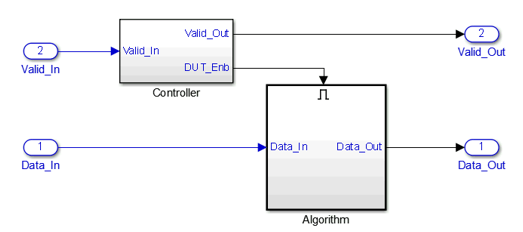

Можно также использовать контроллер в DUT, который генерирует разрешать сигнал для активированной подсистемы.

Противодавление используется нисходящими компонентами, чтобы сказать восходящим компонентам, что они не готовы получить данные. AXI4-потоковые интерфейсы в вашем DUT могут опционально включать Готовый сигнал.. Используйте Готовый сигнал для:

Примените противодавление в AXI4-потоковом ведомом интерфейсе. Например, пропустите Готовый сигнал, когда нисходящий компонент не будет готов получить данные.

Ответьте на противодавление в AXI4-потоковом ведущем интерфейсе. Например, прекратите отправлять данные, когда нисходящий Готовый сигнал компонента будет низким.

Когда вы используете один канал потоковой передачи, по умолчанию, HDL Coder генерирует Готовый сигнал и логику, чтобы обработать противодавление. Связи логики противодавления Готовый сигнал к DUT Включают сигнал. Когда входное ведущее устройство, Готовый сигнал является низким, DUT, отключено, и выходное ведомое устройство, Готовый сигнал управляется низко. Поскольку, HDL Coder генерирует противодавление логический и Готовый сигнал, когда вы используете один канал потоковой передачи, Готовый сигнал является дополнительным, и вы не должны моделировать этот сигнал в порте DUT.

Когда вы используете несколько каналов потоковой передачи, HDL Coder генерирует готовый сигнал и не генерирует логику противодавления. В DUT с несколькими каналами потоковой передачи:

Основной канал игнорирует Готовый сигнал от нисходящих компонентов.

Готовый сигнал ведомого канала высок, который заставляет восходящие компоненты продолжать отправлять данные.

Отсутствие логики противодавления могло привести к пропускаемым данным. Избежать потери данных и применить противодавление на ведомый интерфейс или ответить на противодавление от основного интерфейса в вашем проекте:

Смоделируйте Готовый сигнал для каждого дополнительного потокового интерфейса.

Сопоставьте смоделированный Готовый сигнал с портом DUT для дополнительного интерфейса.

Когда вы не моделируете Готовый сигнал, задача Set Target Interface выводит предупреждение, которое обеспечивает имена интерфейсов, которые требуют порта Ready. Если ваш проект не требует применения или ответа на противодавление, проигнорируйте это предупреждение.

Если вы моделируете Готовый сигнал в своих AXI4-потоковых интерфейсах, ваш основной интерфейс игнорирует Данные и Допустимые сигналы один такт после того, как Готовый сигнал является de-asserted. Можно начать отправлять Данные и Допустимые сигналы, если Готовый сигнал утверждается. После того, как Готовый сигнал является de-asserted, можно отправить еще одни Данные и Допустимый сигнал.

Если вы не моделируете Готовый сигнал, HDL Coder генерирует сигнал и связанную логику противодавления. Эта схема иллюстрирует отношение между Данными, Допустимыми, и Готовыми сигналами согласно упрощенному протоколу потоковой передачи. Когда вы запускаете рабочий процесс генерации ядра IP, HDL Coder добавляет модуль интерфейса потоковой передачи в ядре IP HDL, которое переводит упрощенный протокол в полный AXI4-потоковый протокол. В этой схеме сигнал часов представлен clk.

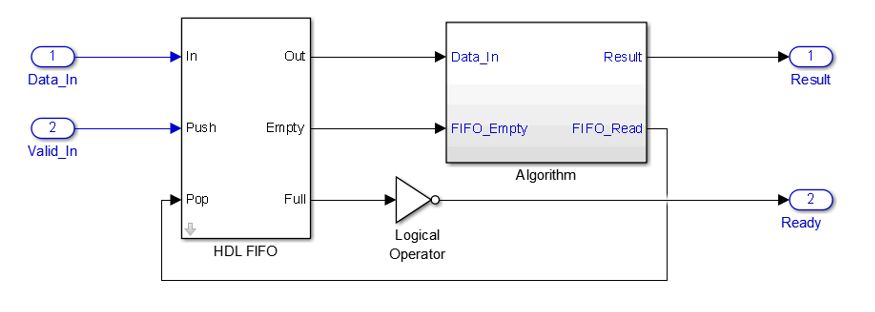

Например, если у вас есть метод "первым пришел - первым вышел" (FIFO) в вашем DUT, чтобы сохранить систему координат данных, применить противодавление к восходящему компоненту, смоделируйте Готовый сигнал на основе FIFO Полный сигнал.

Примечание

Если вы включаете балансировку задержки, кодер вставляет одну или несколько задержек на Готовом сигнале. Отключите задержку, балансирующуюся для Готового пути прохождения сигнала.

Интерфейс AXI4-Stream на вашем DUT может опционально смоделировать сигнал TLAST, который используется, чтобы указать на конец системы координат данных. Если вы не моделируете этот сигнал, HDL Coder генерирует его для вас. В интерфейсе AXI4-Stream Slave поступление проигнорирован сигнал TLAST. В интерфейсе AXI4-Stream Master утверждается автоматически сгенерированный сигнал TLAST, когда количество допустимых выборок рассчитывает до значения длины системы координат по умолчанию. Значение длины системы координат по умолчанию может быть установлено с помощью опций интерфейса AXI4-Stream в Целевой Интерфейсной Таблице. Смотрите, Интерфейсные Опции для Потоковых Данных AXI4.

Когда ядро IP имеет интерфейс AXI4 Slave, значение длины системы координат по умолчанию хранится в программируемом регистре в ядре IP. Можно изменить длину системы координат по умолчанию во время времени выполнения. Когда регистр длины системы координат по умолчанию изменяется посреди системы координат, состояние счетчика TLAST сброшено до нуля, чтобы обнулить, и сигнал TLAST утверждается рано. Можно найти адрес для программируемого регистра TLAST в отчете генерации ядра IP.

Когда это необходимо, чтобы симулировать данные сигнализируют как система координат на контуре DUT, модели в основанном на системе координат режиме. В основанном на системе координат режиме смоделируйте сигнал данных как вектор и установите Демонстрационную Размерность Упаковки ни на Один. Смотрите Демонстрационную Размерность Упаковки.

Основанный на системе координат режим полезен для моделирования и симуляции системного взаимодействия между аппаратным и программным обеспечением и генерацией кода для программного драйвера.

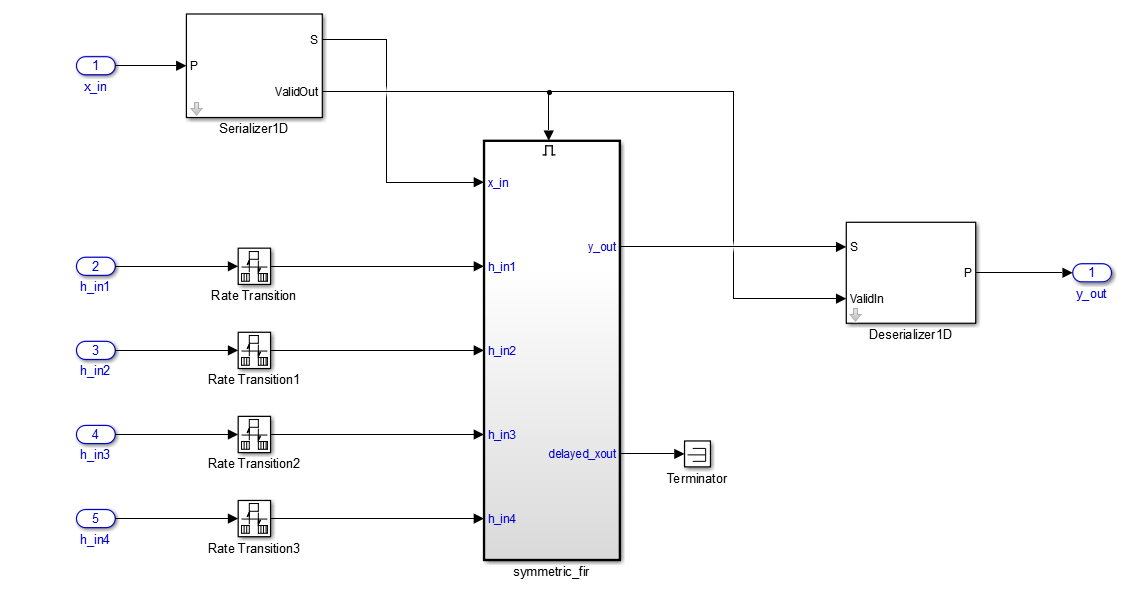

Когда вы сопоставляете векторные порты с AXI4-потоковыми интерфейсами:

Соедините каждый порт данных входного вектора DUT с блоком Serializer1D.

Блок Serializer1D должен иметь порт ValidOut и набор Отношения к векторной битной ширине.

Соедините каждый порт данных выходного вектора DUT с блоком Deserializer1D.

Блок Deserializer1D должен иметь порт ValidIn и набор Отношения к векторной битной ширине.

Соедините каждый скалярный порт, который сопоставляет с интерфейсом AXI4-Lite с блоком Rate Transition.

Отношение в блоке Rate Transition должно совпадать с отношением в блоках Deserializer1D и Serializer1D.

Каждый скалярный порт, который сопоставляет с внешним портом, должен иметь тот же шаг расчета как подсистема алгоритма потоковой передачи.

Подсистема алгоритма потоковой передачи следует за теми же Данными и Допустимым шаблоном моделирования сигнала, как шаблон для отображения скалярных портов к AXI4-потоку взаимодействует через интерфейс. Смотрите Данные модели и Допустимые Сигналы в Simulink.

Чтобы сопоставить векторные порты с AXI4-потоковыми интерфейсами, откройте hdlcoder_sfir_fixed_vector.slx модель. В hdlcoder_sfir_fixed_vector.slx модель, блок symmetric_fir является подсистемой алгоритма потоковой передачи.

Когда вы запускаете IP Core Generation рабочий процесс, можно сопоставить несколько скалярных портов DUT с AXI4-потоковыми Ведущими и AXI4-потоковыми Ведомыми каналами. Когда вы используете векторные порты, можно сопоставить порты с самое большее одним AXI4-потоковым Ведущим каналом и одним AXI4-потоковым Ведомым каналом.

Примечание

Если вы используете несколько каналов потоковой передачи, HDL Coder генерирует Готовый сигнал, но не генерирует логику противодавления. Если вы хотите, чтобы ваш проект обработал противодавление, смоделируйте Готовый сигнал в своем проекте.

Чтобы узнать больше, смотрите, Генерируют Ядро IP HDL с Несколькими, AXI4-передают-потоком и Основные Интерфейсы AXI4.

Когда вы запускаете рабочий процесс Генерации Ядра IP, используйте программное обеспечение HDL Coder для проектов, которые имеют несколько частот дискретизации. Когда вы сопоставляете интерфейсные порты с AXI4-потоковыми Ведущими или AXI4-потоковыми Ведомыми интерфейсами, чтобы использовать несколько частот дискретизации, сопоставить порты DUT, которые сопоставляют с этими интерфейсами AXI4, чтобы запуститься на самом быстром уровне проекта или на уровнях медленнее, чем уровень проекта.

HDL Coder запускает порты DUT, сопоставленные с AXI4-потоковым ведущим устройством и ведомыми интерфейсами на уровнях медленнее, чем уровень проекта модели:

Установка AXI4-потокового ведущего устройства образовывает канал допустимый сигнал к высоко в первом цикле каждый такты N. Например, если уровень проекта в восемь раз быстрее, чем порты DUT низкой скорости, допустимый сигнал высок для первого такта каждые восемь тактов.

Утверждение противодавления на AXI4-потоковом ведомом устройстве взаимодействует через интерфейс, чтобы убедиться, что входящие данные передаются потоком по курсу одной системы координат данных каждый такты N. Например, если уровень проекта в восемь раз быстрее, чем порты DUT низкой скорости, первая система координат передается потоком в такте один, вторая система координат в такте девять, и так далее.

Когда вы сопоставляете порт AXI4-Stream Interface DUT с самым быстрым уровнем в проекте, допустимый сигнал высоко всегда убеждается, что в AXI4-потоковом ведомом интерфейсе нет никакого противодавления.

При разработке моделей, которые имеют несколько частот дискретизации, весь AXI4-потоковый ведущий интерфейс, который сопоставленные порты DUT должны запустить на том же уровне. Весь AXI4-потоковый ведомый интерфейс сопоставленные порты DUT должен запуститься на том же уровне.

Чтобы узнать больше, смотрите Многоскоростную Генерацию Ядра IP.

Когда вы запускаете рабочий процесс Генерации Ядра IP на модели, которая имеет векторные данные, можно задать, как векторные данные обработаны как выборка или как система координат при помощи Sample Packing Dimension. Когда векторные данные обработаны как выборка, можно задать, как векторные элементы упаковываются вместе при помощи опции Packing mode.

Когда вы запускаете рабочий процесс Генерации Ядра IP на модели, которая имеет интерфейс AXI4 Stream ни с одним из сигналов, сопоставленных с TLAST, можно задать TLAST укажите значение при помощи опции DefaultFrameLength.

Задайте длину системы координат по умолчанию (TLAST) значение для интерфейса AXI4 Stream Master, когда вы не смоделируете сигнал TLAST. Сигнал TLAST создается для вас В сгенерированном ядре IP, и сигнал утверждается, когда количество допустимых выборок рассчитывает до значения в счетчике длины системы координат по умолчанию. Когда сгенерированное ядро IP имеет интерфейс AXI4 Slave, HDL Coder генерирует длину системы координат по умолчанию как программируемый регистр. Когда регистр длины системы координат по умолчанию изменяется посреди системы координат, состояние счетчика TLAST сброшено до нуля, чтобы обнулить, и сигнал TLAST утверждается рано. Для получения дополнительной информации см. (дополнительный) Сигнал TLAST. Когда вы не выбираете Generate default AXI4 slave interface, длина системы координат по умолчанию сгенерирована как постоянное значение и не как программируемый регистр.

Задайте, обработаны ли векторные данные как выборка или как система координат.

'none'. Это - значение по умолчанию. Когда вы не задаете Ни один, векторы обработаны как системы координат, и векторные элементы передаются потоком один за другим. Например, когда вход шесть одним вектор за первый такт, первый векторный элемент передается потоком, второй векторный элемент, за второй такт, и так далее. Модель должна содержать блок Serializer для входных параметров и блок Deserializer для выходных параметров, чтобы использовать этот режим. Packing mode не доступен, когда Sample Packing Dimension не установлен ни в Один.

Все. Когда вы задаете Все, векторы упаковываются вместе и передаются потоком за один такт. Например, когда вход шесть одним вектор, все векторные элементы упаковываются вместе и передаются потоком за один такт. В этом случае можно задать, как векторные элементы упаковываются при помощи опции Packing mode.

Задайте, как векторные элементы упаковываются вместе, когда Sample Packing Dimension установлен во Все. Режим упаковки применяется к AXI4-потоковому ведомому устройству и основным каналам. На основном канале данные упаковываются с помощью Выровненного Бита или Степень 2 Выровненных форматов. На ведомом канале данные распакованы на основе основного формата упаковки канала.

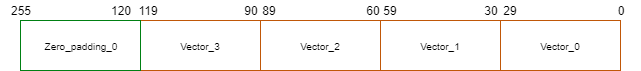

Выровненный бит. В этом режиме векторные элементы упаковываются непосредственно друг рядом с другом. Если упакованная битная ширина меньше ширины AXI4-речного-русла, то упакованные данные дополнены нулями, чтобы совпадать с шириной канала.

Например:

Ширина AXI4-речного-русла составляет 256 битов.

Векторы 30 битов длиной и существует 4 векторных системы координат. Общая ширина данных составляет 120 битов.

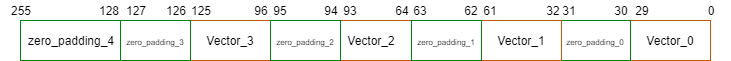

Когда режим упаковки установлен в Выровненный Бит, AXI4-потоковые данные упаковываются как в этой схеме

Степень 2 Выровненных. В этом режиме векторные элементы сначала дополнены нулями к самому близкому контуру степени двойки. Затем заполненные элементы упаковываются вместе. Если упакованная векторная битная ширина меньше ширины AXI4-речного-русла, то упакованные данные дополнены нулями, чтобы совпадать с шириной канала.

Например:

Ширина AXI4-речного-русла составляет 256 битов.

Векторы 30 битов длиной и существует 4 векторных системы координат. Общая ширина данных составляет 120 битов.

Когда режим упаковки установлен в Степень 2 Выровненных, AXI4-потоковые данные упаковываются как показано в этой схеме:

Каждый векторный элемент битной ширины 30 дополнен нулями битной ширины два, чтобы расширить его к 32, самый близкий контур степени двойки.

Когда вы сопоставляете скалярные или векторные порты DUT с AXI4-потоковыми интерфейсами:

Xilinx® Zynq®- 7000 или Intel® Куарт® Главный должна быть ваша целевая платформа.

Xilinx Vivado® или Intel Куарт Прайм должен быть вашим инструментом синтеза.

Processor/FPGA synchronization должен быть Свободный ход.

Когда вы используете основанное на системе координат моделирование, вы не можете использовать сигналы протокола кроме Данных и Допустимый. Например, Готовый и TLAST не поддерживаются.