Декодируйте convolutionally закодированное использование данных алгоритм Viterbi (HDL Coder)

Блок Viterbi Decoder доступен с Communications Toolbox™.

Для декодирования данных, закодированных с усеченными или отключенными режимами или проколотыми кодами, используют блок Viterbi Decoder от LTE HDL Toolbox™.

Для получения информации о поведении симуляции и параметрах блоков, смотрите Декодер Витерби.

HDL Coder™ поддерживает следующие функции блока Viterbi Decoder:

Нерекурсивный энкодер/декодер с прямой каналом решеткой и простой настройкой генерации сдвигового регистра

Непрерывный режим

Основанный на выборке вход

Уровни декодера от 1/2 до 1/7

Продолжительность ограничения от 3 до 9

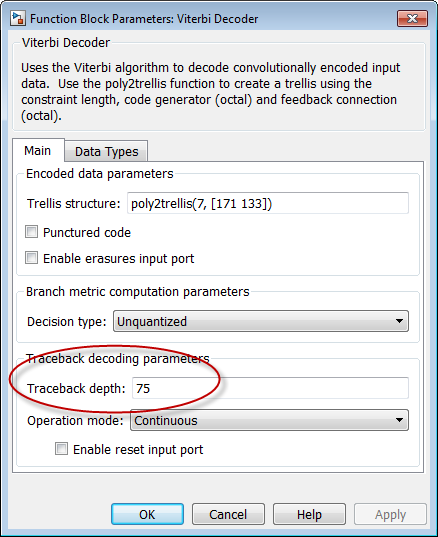

Блок Viterbi Decoder декодирует каждый бит путем прослеживания через traceback глубину, которую вы задаете для блока. Блок реализует полный traceback для каждого бита решения, с помощью регистров, чтобы сохранить минимальный индекс состояния и выбор при разветвлении в traceback декодирование модуля. Существует два метода, чтобы оптимизировать traceback логику: конвейерная основанная на регистре реализация или основанная на RAM архитектура. Смотрите генерацию HDL-кода для Декодера Витерби (Communications Toolbox) пример.

Можно указать что traceback декодирование модуля быть конвейерными, чтобы улучшить скорость сгенерированной схемы. Можно добавить конвейерные регистры в traceback модуль путем определения количества этапов traceback на конвейерный регистр.

Используя параметр реализации TracebackStagesPerPipeline, можно сбалансировать производительность схемы на основе системных требований. Меньшее значение параметров указывает на требование, чтобы добавить больше регистров, чтобы увеличить скорость traceback схемы. Увеличение значения параметров приводит к меньшему количеству регистров наряду с уменьшением в скорости схемы.

Вместо того, чтобы использовать регистры, можно принять решение использовать RAM, чтобы сохранить информацию ответвления оставшегося в живых. Кодер не поддерживает Enable reset input port при использовании основанного на RAM traceback.

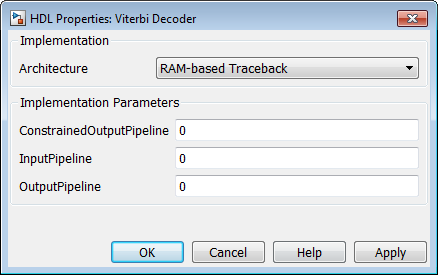

Установите свойство Architecture блока Viterbi Decoder к RAM-based Traceback.

Установите traceback глубину на маске блока Viterbi Decoder.

Основанный на RAM traceback и основанный на регистре traceback отличаются следующими способами:

Основанная на RAM реализация прослеживает через один набор данных, чтобы найти, что начальное состояние декодирует предыдущий набор данных. Основанная на регистре реализация комбинирует traceback, и декодируйте операции в один шаг. Это использует лучшее состояние, найденное от минимальной операции как начальное состояние декодирования.

Основанная на RAM реализация прослеживает посредством выборок M, декодирует предыдущие биты M в обратном порядке и выпускает один бит по порядку в каждом такте. Основанная на регистре реализация декодирует один бит после полного traceback.

Из-за различий в двух traceback алгоритмах основанная на RAM реализация приводит к различным числовым результатам, чем основанный на регистре traceback. Более долгая traceback глубина, например, 10 раз продолжительность ограничения, рекомендуется в основанном на RAM traceback. Эта глубина достигает подобной частоты ошибок по битам (BER) как основанной на регистре реализации. Размер RAM, требуемого для реализации, зависит от решетки и traceback глубины.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Смотрите основанный на регистре Traceback.

Punctured code: не выбирайте эту опцию. Проколотый код требует основанного на кадре входа, который не поддерживает HDL Coder.

Decision type: кодер не поддерживает тип решения Unquantized.

Error if quantized input values are out of range: кодер не поддерживает эту опцию.

Operation mode: кодер поддерживает только режим Continuous.

Enable reset input port: Когда вы включаете и Enable reset input port и Delay reset action to next time step, поддержка HDL оказывается. Необходимо выбрать режим работы Continuous и использовать основанный на регистре traceback.

Вы не можете использовать блок Viterbi Decoder в Восстановленной Синхронной Подсистеме.

Когда Decision type установлен в Soft decision, реализация HDL блока Viterbi Decoder поддерживает входные параметры фиксированной точки и вывод. Для входа типом данных с фиксированной точкой должен быть ufixN. N является количеством битов мягкого решения. Встроенные типы данных со знаком (int8, int16, int32) не поддержаны. Для вывода реализация HDL блока Viterbi Decoder поддерживает поддержанные блоком типы выходных данных.

Когда Decision type установлен в Hard decision, вход поддержек блока с типами данных ufix1 и Boolean. Для вывода реализация HDL блока Viterbi Decoder поддерживает поддержанные блоком типы выходных данных.

Реализация HDL блока Viterbi Decoder не поддерживает двойные и один типы входных данных. Блок не поддерживает вывод с плавающей точкой для входных параметров фиксированной точки.