Представляйте восстановленную подсистему, которая имеет синхронный сброс, и включите поведение

HDL Coder / Подсистемы HDL

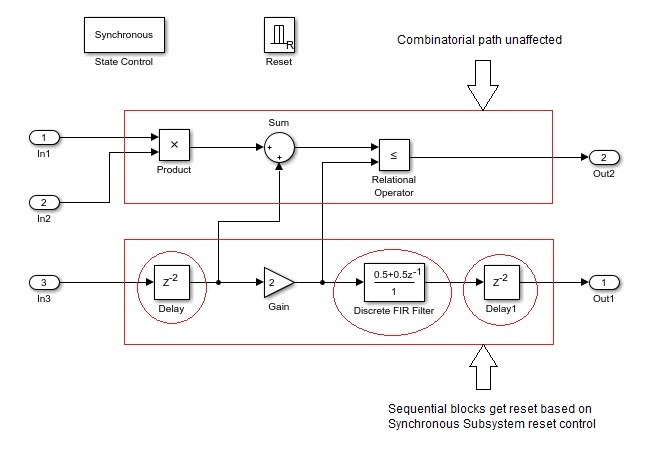

Восстановленная Синхронная Подсистема использует блок State Control в режиме Synchronous с Восстановленным блоком Subsystem. Для блоков подсистемы с состоянием блок State Control в режиме Synchronous обеспечивает эффективный сброс, и включите поведение симуляции на оборудовании.

Порт сброса в Восстановленном Синхронном блоке Subsystem добавляет возможность сброса в блоки в подсистеме, которые имеют состояние. Это включает блоки, которые не должны иметь внешней возможности порта сброса, такой как фильтры,

График Stateflow® и блоки MATLAB function. Для генерации HDL-кода Reset trigger type порта Reset установлен в level hold по умолчанию.

См. Inport для получения информации о типах данных, принятых входными портами подсистемы. Смотрите Выходной порт для получения информации о типах данных, выведенных выходными портами подсистемы.

Для получения дополнительной информации смотрите Типы данных, Поддержанные Simulink (Simulink) в документации Simulink®.

Метки порта подсистемы отображения на блоке подсистемы.

Значение по умолчанию:

FromPortIcon

noneНе отображает метки порта на блоке подсистемы.

FromPortIconЕсли соответствующий значок порта отображает имя сигнала, параметр отображает имя сигнала на блоке подсистемы. В противном случае это отображает имя блокировки порта.

FromPortBlockNameОтобразите имя соответствующей блокировки порта на блоке подсистемы.

SignalNameЕсли сигнал, соединенный с портом блока подсистемы, называют, этот параметр отображает имя. В противном случае это отображает имя соответствующей блокировки порта.

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Управляйте пользовательским доступом к содержимому подсистемы.

Значение по умолчанию:

ReadWrite

ReadWriteПозволяет открыться и модификация содержимого подсистемы.

ReadOnlyВключает открытие, но не модификацию подсистемы. Если подсистема находится в библиотеке блоков, можно создать и открыть ссылки на подсистему, и создать и изменить локальные копии подсистемы. Вы не можете изменить полномочия или изменить содержимое исходного экземпляра библиотеки.

NoReadOrWriteОтключает открытие или модификацию подсистемы. Если подсистема находится в библиотеке блоков, можно создать ссылки на подсистему в модели. Вы не можете открыть, изменить, полномочия изменения, или создать локальные копии подсистемы.

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Введите имя функции, которое будет названо, если ошибка происходит, в то время как программное обеспечение Simulink выполняет подсистему.

Значение по умолчанию:

' '

Simulink передает два аргумента функции: указатель подсистемы и вектор символов, который задает ошибочный тип. Если никакая функция не задана, вы получаете типичное сообщение об ошибке.

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Задайте, разрешить ли имена переменных рабочей области, на которые ссылается эта подсистема.

Значение по умолчанию:

All

AllРазрешите все имена переменных рабочей области, используемых этой подсистемой, включая используемых, чтобы задать значения параметров блоков и Объекты данных Simulink (например, объекты Simulink.Signal).

ExplicitOnlyРазрешите, что имена переменных рабочей области раньше задавали значения параметров блоков, память хранилища данных (где никакой блок не существует), сигналы, и утверждает отмеченный при помощи значка разрешения сигнала.

NoneНе разрешайте имена переменных рабочей области.

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Причины Simulink, чтобы обработать подсистему как модуль при определении порядка выполнения методов блока.

Значение по умолчанию: 'off'

Заставьте Simulink обрабатывать подсистему как модуль при определении порядка выполнения методов блока. Например, когда это должно вычислить вывод подсистемы, программное обеспечение Simulink вызывает выходные методы всех блоков в подсистеме прежде, чем вызвать выходные методы других блоков на том же уровне как блок подсистемы.

Заставьте Simulink обрабатывать все блоки в подсистеме, как являющейся на том же уровне в иерархии модели как подсистема при определении порядка выполнения метода блока. Это может заставить осуществление методов блока в подсистеме быть чередованным с осуществлением методов блока вне подсистемы.

Этот параметр включает:

Minimize algebraic loop occurrences

Sample time

Function packaging (требует лицензии Simulink Coder™),

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Программное обеспечение Simulink причин, чтобы обработать подсистему как модуль при распространении различных условий от Различных Исходных блоков или к Различным блокам Приемника.

Значение по умолчанию: на

Simulink обрабатывает подсистему как модуль при распространении различных условий от Различных Исходных блоков или к Различным блокам Приемника. Например, когда Simulink вычисляет различное условие подсистемы, это распространяет то условие ко всем блокам в подсистеме.

Simulink обрабатывает все блоки в подсистеме, как являющейся на том же уровне в иерархии модели как сама подсистема при определении их различного условия.

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Задайте формат кода, который будет сгенерирован для атомарной (невиртуальной) подсистемы.

Значение по умолчанию:

Auto

AutoSimulink Coder выбирает оптимальный формат на основе типа и количества экземпляров подсистемы в модели.

InlineSimulink Coder встраивает подсистему безусловно.

Nonreusable functionПрограммное обеспечение Simulink Coder явным образом генерирует отдельную функцию в отдельном файле. Подсистемы с этой установкой генерируют функции, которые могут иметь аргументы в зависимости от установки параметра Function interface. Можно назвать сгенерированную функцию и файл с помощью параметров Function name и File name (no extension). Эти функции не повторно используемы.

Reusable functionSimulink Coder генерирует функцию с аргументами, которая позволяет повторное использование кода подсистемы, когда модель включает несколько экземпляров подсистемы.

Эта опция генерирует функцию с аргументами, которая позволяет коду подсистемы быть снова использованным в сгенерированном коде иерархии модели - ссылки. В этом случае подсистема должна быть в библиотеке.

Смотрите Специфичные для блока Параметры (Simulink) для получения информации о командной строке.

Типы данных | Дважды | один | булевская переменная | основывают целое число | фиксированная точка | перечислимый | шина |

Многомерные сигналы | Да |

Сигналы переменного размера | Да |

Генерация HDL-кода | Да |

| Архитектура | Описание |

|---|---|

Module (значение по умолчанию) | Сгенерируйте код для подсистемы и блоков в подсистеме. |

BlackBox | Сгенерируйте интерфейс черного квадрата. Сгенерированный HDL-код включает только определения порта ввода/вывода для подсистемы. Поэтому можно использовать подсистему в модели, чтобы сгенерировать интерфейс к существующему, вручную записанному HDL-коду. Генерация интерфейса черного ящика для подсистем подобна генерации интерфейса блока Model без сигналов часов. |

| Удалите подсистему из сгенерированного кода. Можно использовать подсистему в симуляции, однако, обработать его как "нет" в HDL-коде. |

Для архитектуры BlackBox можно настроить имена порта и установить атрибуты интерфейса внешнего компонента. Смотрите Настраивают Черный квадрат или HDL Интерфейс Cosimulation.

Автоматическая конвейерная вставка на основе инструмента синтеза, предназначайтесь для частоты и размеров слова множителя. Значением по умолчанию является inherit. См. также AdaptivePipelining.

Обнаруживает введение новых задержек вдоль одного пути и вставляет соответствие с задержками на других путях. Значением по умолчанию является inherit. См. также BalanceDelays.

Вставьте конвейерные регистры на более быстрой тактовой частоте вместо более медленной скорости передачи данных. Значением по умолчанию является inherit. См. также ClockRatePipelining.

Количество регистров, чтобы поместить при выходных параметрах путем перемещения существующих задержек в рамках проекта. Распределенная конвейеризация не перераспределяет эти регистры. Значение по умолчанию 0. См. также ConstrainedOutputPipeline.

Конвейерно обработайте распределение регистра или повторную синхронизацию регистра. Значением по умолчанию является off. См. также DistributedPipelining.

Синтез приписывает для отображения множителя. Значением по умолчанию является none. См. также DSPStyle.

Удалите иерархию подсистемы из сгенерированного HDL-кода. Значением по умолчанию является inherit. См. также FlattenHierarchy.

Количество входных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также InputPipeline.

Количество выходных настроек канала связи, чтобы вставить в сгенерированный код. Распределенная конвейеризация и ограниченная выходная конвейеризация могут переместить эти регистры. Значение по умолчанию 0. См. также OutputPipeline.

Количество функционально эквивалентных ресурсов, чтобы сопоставить с одним совместно используемым ресурсом. Значение по умолчанию 0. См. также Разделение ресурсов.

Количество параллельных информационных каналов или векторы, которые являются временем, мультиплексированным, чтобы преобразовать в последовательные, скалярные информационные каналы. Значение по умолчанию 0, который реализует полностью параллельные информационные каналы. См. также Потоковую передачу.

Если этот блок не является DUT, настройки свойства блока во вкладке Target Specification проигнорированы.

В HDL Workflow Advisor, если вы используете рабочий процесс IP Core Generation, эти целевые значения свойств блока спецификации сохранены с моделью. Если вы задаете эти целевые значения свойств блока спецификации с помощью hdlset_param, когда вы открываете HDL Workflow Advisor, поля заполняются с соответствующими значениями.

Режим синхронизации процессора/FPGA, заданный как вектор символов.

Чтобы сохранить это свойство блока на модели, задайте Processor/FPGA Synchronization в задаче Set Target Interface рабочего процесса IP Core Generation.

Значения: Free running (значение по умолчанию) | Coprocessing - blocking

Пример: 'Free running'

Чтобы сохранить это свойство блока на модели, задайте отображение портов тестовой точки к интерфейсам целевой платформы в задаче Set Target Interface рабочего процесса IP Core Generation.

Значения: '' (значение по умолчанию) | массив ячеек из символьных векторов

Пример: '{{'TestPoint','AXI4-Lite','x"108"'}}'

Чтобы сохранить это свойство блока на модели, задайте отображение портов настраиваемого параметра к интерфейсам целевой платформы в задаче Set Target Interface рабочего процесса IP Core Generation.

Значения: '' (значение по умолчанию) | массив ячеек из символьных векторов

Пример: '{{'myParam','AXI4-Lite','x"108"'}}'

Чтобы сохранить это свойство блока на модели, задайте, хотите ли вы включить readback на ведомых регистрах записи AXI4 в задаче Generate RTL Code and IP Core рабочего процесса IP Core Generation.

Значения: 'off' (значение по умолчанию) | 'on'

Чтобы сохранить это свойство блока на модели, задайте, хотите ли вы отключить генерацию ведомых интерфейсов AXI4 по умолчанию в задаче Generate RTL Code and IP Core рабочего процесса IP Core Generation.

Значения: 'on' (значение по умолчанию) | 'off'

Verilog® или файлы VHDL® для черных квадратов в вашем проекте. Задайте полный путь к каждому файлу и разделите имена файлов точкой с запятой (;).

Можно установить это свойство в HDL Workflow Advisor в поле Additional source files.

Значения: '' (значение по умолчанию) | вектор символов

Пример: 'C:\myprojfiles\led_blinking_file1.vhd;C:\myprojfiles\led_blinking_file2.vhd;'

Имя ядра IP, заданное как вектор символов.

Можно установить это свойство в HDL Workflow Advisor в поле IP core name. Если это свойство установлено в значение по умолчанию, HDL Workflow Advisor создает имя ядра IP на основе имени DUT.

Значения: '' (значение по умолчанию) | вектор символов

Пример: 'my_model_name'

Номер версии ядра IP, заданный как вектор символов.

Можно установить это свойство в HDL Workflow Advisor в поле IP core version. Если это свойство установлено в значение по умолчанию, HDL Workflow Advisor устанавливает версию ядра IP.

Значения: '' (значение по умолчанию) | вектор символов

Пример: '1.3'

Вы не можете использовать блок State Control в режиме Classic или удалить блок State Control от Восстановленного Синхронного блока Subsystem.

Reset trigger type порта Reset в подсистеме должен быть установлен в level hold.

Блок Delay с невиртуальными входными сигналами шины в Восстановленной Синхронной Подсистеме не поддержан, если вы включаете оптимизацию на подсистеме.

HDL Coder™ не поддерживает эти блоки в Восстановленной Синхронной Подсистеме:

Все блоки RAM или блоки, которые выводят RAM в сгенерированном HDL-коде. Блоки RAM включают:

Один порт RAM

Простой двухпортовый RAM

Двухпортовый RAM

Двойной уровень двухпортовый RAM

FIFO HDL

Системный объект hdl.RAM

DSP System Toolbox

Фильтр Biquad

Оптимизированный HDL NCO

Communications Toolbox

Сверточный энкодер

Декодер Витерби

Генератор последовательности PN

Выведенный целым числом оптимизированный HDL декодера RS

Vision HDL Toolbox

Интерполятор Demosaic

Детектор ребра

Гистограмма

Отобразите фильтр, средний фильтр, двусторонний фильтр

Память строки

Бинарные и Полутоновые блоки Морфологии

Пиксельный поток FIFO

LTE HDL Toolbox

Турбо декодер

Турбо энкодер

Сверточный энкодер

Демодулятор OFDM

Включить | Enabled синхронная подсистема | Госконтроль | Синхронная подсистема