С программным обеспечением HDL Coder™ можно реализовать упрощенный, передающий потоком протокол в модели. Программное обеспечение генерирует AXI4-потоковые интерфейсы в ядре IP.

Когда это необходимо, чтобы сгенерировать интерфейс AXI4-Stream в вашем ядре IP, в вашем интерфейсе DUT, реализуют следующие сигналы:

Данные

Допустимый

Когда вы сопоставляете скалярные порты DUT с интерфейсом AXI4-Stream, можно опционально смоделировать следующие сигналы и сопоставить их с интерфейсом AXI4-Stream:

Готовый

Другие сигналы протокола, такие как:

TSTRB

TKEEP

TLAST

TID

TDEST

TUSER

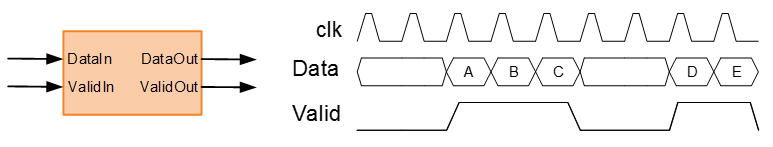

Когда сигнал Данных допустим, Допустимый сигнал утверждается.

Если вы хотите сгенерировать аппаратное ядро IP, но не должны смоделировать и моделировать взаимодействие между программным и аппаратным обеспечением, используйте скалярные порты данных в своем интерфейсе DUT. Сопоставьте порты данных с AXI4-потоковыми интерфейсами.

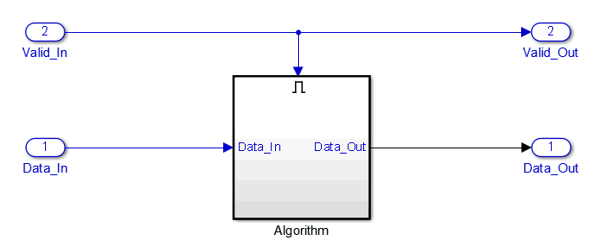

Смоделировать Данные и Допустимые сигналы в Simulink®:

Заключите алгоритм, который обрабатывает сигнал Данных при помощи активированной подсистемы.

Управляйте разрешать портом активированной подсистемы при помощи Допустимого сигнала.

Например, можно непосредственно соединить Допустимый сигнал с разрешать портом.

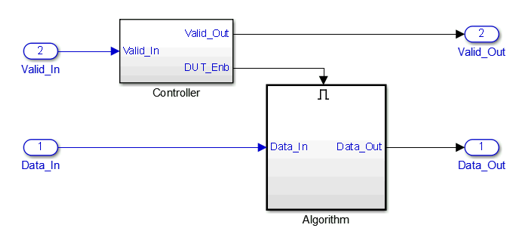

Можно также использовать контроллер в DUT, который генерирует разрешать сигнал для активированной подсистемы.

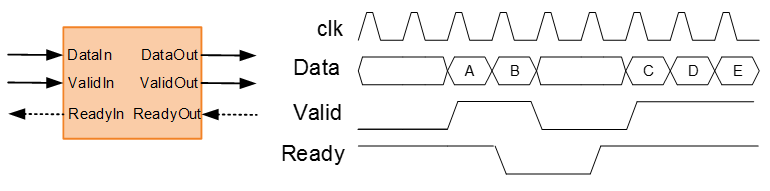

AXI4-потоковые интерфейсы в вашем DUT могут опционально включать Готовый сигнал. В интерфейсе Slave Готовый сигнал позволяет вам применить противодавление. В интерфейсе Master Готовый сигнал позволяет вам ответить на противодавление.

Если вы моделируете Готовый сигнал в своих AXI4-потоковых интерфейсах, ваш интерфейс Master игнорирует Данные и Допустимые сигналы один такт после того, как Готовый сигнал является deasserted. Можно начать отправлять Данные и Допустимые сигналы, если Готовый сигнал утверждается. Можно отправить еще одни Данные и Допустимый сигнал после того, как Готовый сигнал будет deasserted.

Если вы не моделируете Готовый сигнал, HDL Coder генерирует сигнал и связанную логику противодавления.

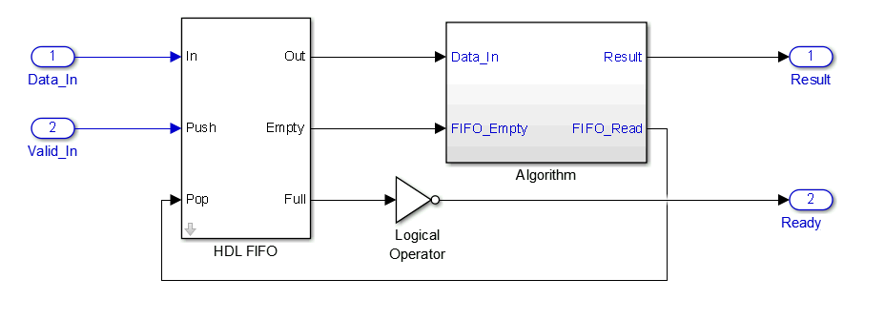

Например, если у вас есть FIFO в вашем DUT, чтобы сохранить кадр данных, применить противодавление к восходящему компоненту, можно смоделировать Готовый сигнал на основе FIFO Полный сигнал.

Если вы включаете балансировку задержки, кодер может вставить одну или несколько задержек на Готовом сигнале. Отключите задержку, балансирующуюся для Готового пути прохождения сигнала.

Можно опционально смоделировать другие AXI4-потоковые сигналы протокола. Если вы моделируете только необходимые Данные и Допустимые сигналы, кодер генерирует TREADY и AXI4-потоковые сигналы протокола TLAST.

Если вы не моделируете сигнал TLAST, кодер генерирует программируемый регистр в ядре IP так, чтобы можно было задать пакетный размер. Детали программируемого пакетного регистра размера находятся в вашем отчете генерации ядра IP.

Если вы хотите смоделировать и моделировать системное взаимодействие между программным и аппаратным обеспечением и сгенерировать код для программного драйвера, используйте векторные порты данных в своем интерфейсе DUT. Сопоставьте порты данных с AXI4-потоковыми интерфейсами.

Когда вы сопоставляете векторные порты с AXI4-потоковыми интерфейсами, ваша модель имеет эти требования:

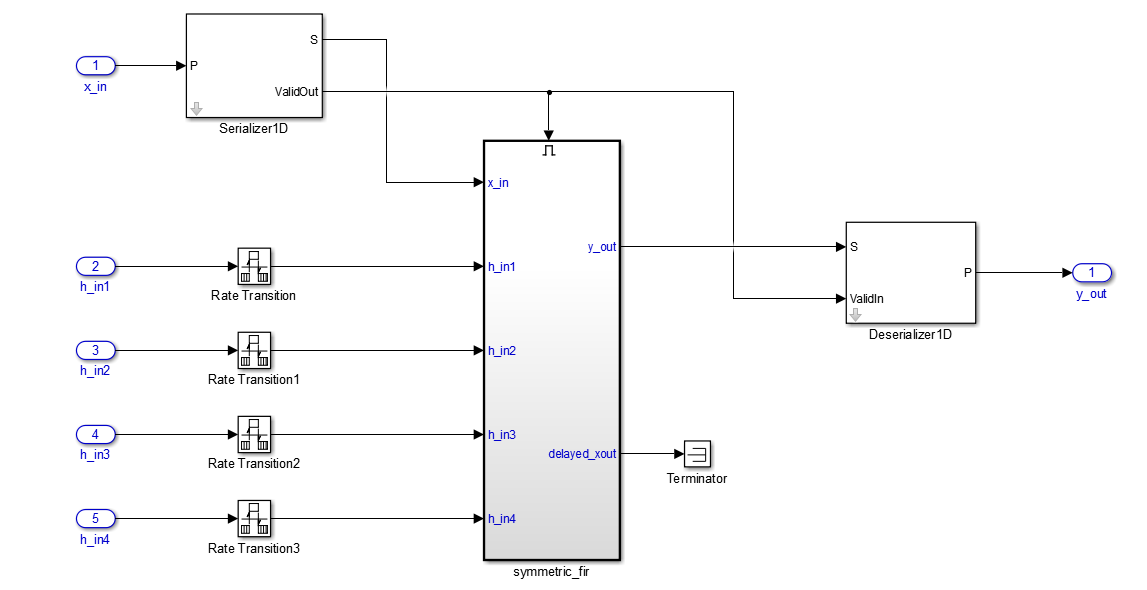

Соедините каждый порт данных входного вектора DUT с блоком Serializer1D.

Блок Serializer1D должен иметь порт ValidOut и набор Отношения к векторной битной ширине.

Соедините каждый порт данных выходного вектора DUT с блоком Deserializer1D.

Блок Deserializer1D должен иметь порт ValidIn и набор Отношения к векторной битной ширине.

Соедините каждый скалярный порт, который сопоставляет с интерфейсом AXI4-Lite к блоку Rate Transition.

Отношение в блоке Rate Transition должно совпадать с Отношением в блоках Serializer1D и Deserializer1D.

Каждый скалярный порт, который сопоставляет с внешним портом, должен иметь тот же шаг расчета как подсистема алгоритма потоковой передачи.

Подсистема алгоритма потоковой передачи следует за теми же Данными, и Допустимый шаблон моделирования сигнала что касается отображения скалярных портов к AXI4-потоку взаимодействует через интерфейс. Смотрите Данные и Допустимый Шаблон Моделирования Сигнала.

Для примера, который показывает, как сопоставить векторные порты с AXI4-потоковыми интерфейсами, открыть модель hdlcoder_sfir_fixed_vector. В модели hdlcoder_sfir_fixed_vector symmetric_fir является подсистемой алгоритма потоковой передачи.

Программное обеспечение HDL Coder поддерживает проекты с несколькими частотами дискретизации, когда вы запускаете рабочий процесс Генерации Ядра IP. Когда вы сопоставляете интерфейсные порты с AXI4-потоковыми Ведущими или AXI4-потоковыми Ведомыми интерфейсами, чтобы использовать несколько частот дискретизации, гарантировать, что порты DUT, которые сопоставляют с этими интерфейсами AXI4, запущенными на самом быстром уровне проекта после генерации HDL-кода.

Чтобы узнать больше, смотрите Многоскоростную Генерацию Ядра IP.

Когда вы сопоставляете скалярные или векторные порты DUT с AXI4-потоковыми интерфейсами:

DUT может иметь самое большее один AXI4-потоковый Ведущий канал и один AXI4-потоковый Ведомый канал.

Xilinx® Zynq®-7000 или Intel® Quartus® Prime должны быть вашей целевой платформой.

Xilinx Vivado® или Intel Куарт Прайм должны быть вашим инструментом синтеза.

Processor/FPGA synchronization должен быть Free running.

Когда вы сопоставляете векторные порты DUT с AXI4-потоковыми интерфейсами, вы не можете использовать сигналы протокола кроме Данных и Допустимый. Например, Готовый и TLAST не поддержаны.