HDL Workflow Advisor проводит вас по этапам генерации HDL-кода для подсистемы Simulink® и процесса проектирования FPGA, таким как:

Проверка модели для совместимости генерации HDL-кода и автоматически фиксация несовместимых настроек.

Генерация HDL-кода, испытательного стенда и скриптов, чтобы создать и запустить код и испытательный стенд.

Генерация cosimulation или испытательных стендов SystemVerilog DPI и покрытия кода (требует HDL Verifier™).

Синтез и анализ синхронизации посредством интеграции со сторонними инструментами синтеза.

Обратная корректировка проекта модели с информацией о критическом пути и другой информацией получена во время синтеза.

Полные автоматизированные рабочие процессы для выбранных целевых устройств разработки FPGA, включая FPGA в симуляции цикла (требует HDL Verifier), и рабочий процесс ввода-вывода FPGA Simulink Real-Time™.

Этот пример иллюстрирует, как можно сгенерировать HDL-код для КИХ-модели фильтра и синтезировать проект на устройстве FPGA. Прежде чем вы сгенерируете HDL-код, модель должна быть совместимой для генерации HDL-кода. Чтобы проверять и обновить вашу модель для совместимости HDL, смотрите Совместимость HDL Проверки Модели Simulink Используя Советника по вопросам HDL-кода.

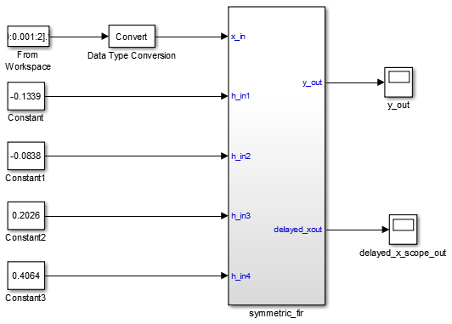

Этот пример использует Симметричную КИХ-модель фильтра, которая совместима для генерации HDL-кода. Открыть эту модель в командной строке, введите:

sfir_fixed

Модель использует разделение труда, которое подходит для проекта HDL.

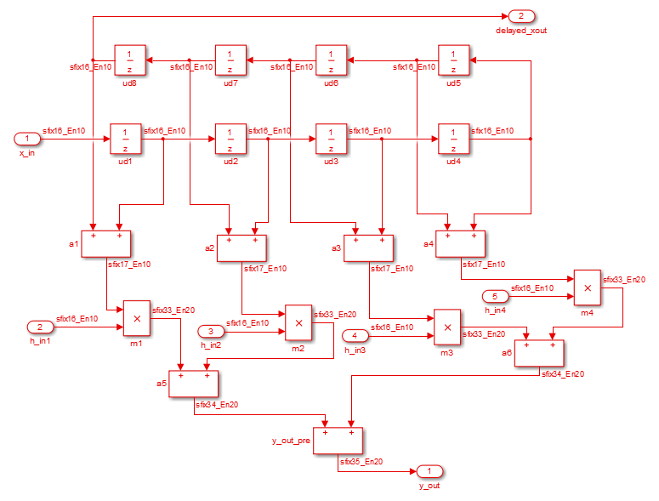

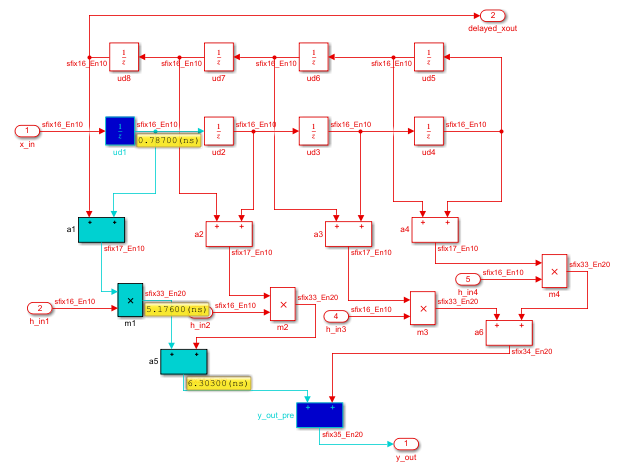

symmetric_fir подсистема, которая реализует алгоритм фильтра, является устройством под тестом (DUT). Сущность HDL сгенерирована от этой подсистемы.

Компоненты модели верхнего уровня, которые управляют подсистемой, работают испытательным стендом.

Модель верхнего уровня генерирует 16-битные входные сигналы фиксированной точки для symmetric_fir подсистема. Блок Signal From Workspace генерирует тестовое воздействие (стимул) сигнал для фильтра. Четыре блока Constant обеспечивают коэффициенты фильтра. Блоки Scope используются для симуляции и не используются для генерации HDL-кода.

Перейти к symmetric_fir подсистема, введите:

open_system('sfir_fixed/symmetric_fir')

В MATLAB®:

Создайте папку под названием sl_hdlcoder_work, например:

mkdir C:\work\sl_hdlcoder_work

sl_hdlcoder_work хранит локальную копию модели в качестве примера и папок и сгенерированного HDL-кода. Используйте местоположение папки, которое не является в дереве папки MATLAB.

Сделайте sl_hdlcoder_work папка ваша рабочая папка, например:

cd C:\work\sl_hdlcoder_workСохраните локальную копию sfir_fixed модель к вашей текущей рабочей папке. Оставьте модель открытой.

Если вы не хотите синтезировать свой проект, но хотеть сгенерировать HDL-код, вы не должны устанавливать инструмент path. В HDL Workflow Advisor, на Set Target> шаг Set Target Device and Synthesis Tool, оставляют установку Synthesis tool No Synthesis Tool Specified по умолчанию, и затем запустите рабочий процесс.

Если вы хотите синтезировать свой проект на целевой платформе, прежде чем вы откроете HDL Workflow Advisor и запустите рабочий процесс, создадите путь к вашему инструменту синтеза. Этот пример использует Xilinx® Vivado®, таким образом, вы, должно быть, уже установили Xilinx Vivado. Чтобы установить инструмент path, используйте hdlsetuptoolpath функционируйте, чтобы указать на установленный исполняемый файл Xilinx Vivado 2019.2. Опционально, можно использовать различный инструмент синтеза по вашему выбору и последовать этому примеру. Чтобы установить путь к тому инструменту синтеза, использовать hdlsetuptoolpath. Чтобы узнать о последних поддерживаемых инструментах, смотрите Поддержку Языка HDL и Поддерживаемые Сторонние программы и Оборудование.

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath',... 'C:\Xilinx\Vivado\2019.1\bin\vivado.bat');

Запустить HDL Workflow Advisor с модели Simulink,

Во вкладке Apps выберите HDL Coder. Вкладка HDL Code появляется.

Выберите DUT Subsystem в своей модели и убедитесь, что это имя Subsystem появляется в опции Code for. Чтобы помнить выбор, можно прикрепить эту опцию. Нажмите Workflow Advisor.

Когда вы открываете HDL Workflow Advisor, генератор кода может предупредить, что папка проекта несовместима. Чтобы открыть Советника, выберите Remove slprj and continue.

В HDL Workflow Advisor левая панель перечисляет папки в иерархии. Каждая папка представляет группу или категорию связанных задач. От левой панели можно выбрать папку или отдельную задачу. HDL Workflow Advisor отображает информацию о выбранной папке или задаче на правой панели.

Чтобы узнать больше о каждой отдельной задаче, щелкните правой кнопкой по той задаче и выберите What's This?.

![]()

Чтобы узнать больше об окне HDL Workflow Advisor, смотрите Начало работы с HDL Workflow Advisor.

В Set Target> шаг Set Target Device and Synthesis Tool, для Synthesis tool, выбирают Xilinx Vivado и выберите Run This Task.

Чтобы сгенерировать код, щелкните правой кнопкой по задаче Generate RTL Code and Testbench и выберите Run to Selected Task.

В FPGA Synthesis and Analysis> Perform Synthesis and P/R> задача Run Implementation, очистите Skip this task и нажмите Apply.

Щелкните правой кнопкой по Annotate Model with Synthesis Result и выберите Run to Selected Task.

Чтобы запустить рабочий процесс HDL в командной строке, можно экспортировать настройки Workflow Advisor в скрипт. Чтобы экспортировать в скрипт, в окне HDL Workflow Advisor, выбирают File> Export to Script. В диалоговом окне Export Workflow Configuration введите имя файла и сохраните скрипт.

Скриптом является файл MATLAB, который можно запустить из командной строки. Можно изменить скрипт непосредственно или, импортировать скрипт в HDL Workflow Advisor, изменить задачи и экспортировать обновленный скрипт. Чтобы узнать больше, смотрите Рабочий процесс HDL Запуска со Скриптом.