В браузере библиотеки Simulink ® можно следовать этой рекомендации в качестве общей практики моделирования проекта с использованием различных блоков.

Каждое руководство имеет уровень серьезности, который указывает уровень соответствия требованиям. Дополнительные сведения см. в разделе Рекомендации по моделированию HDL Уровни серьезности.

1.1.8

Информативный

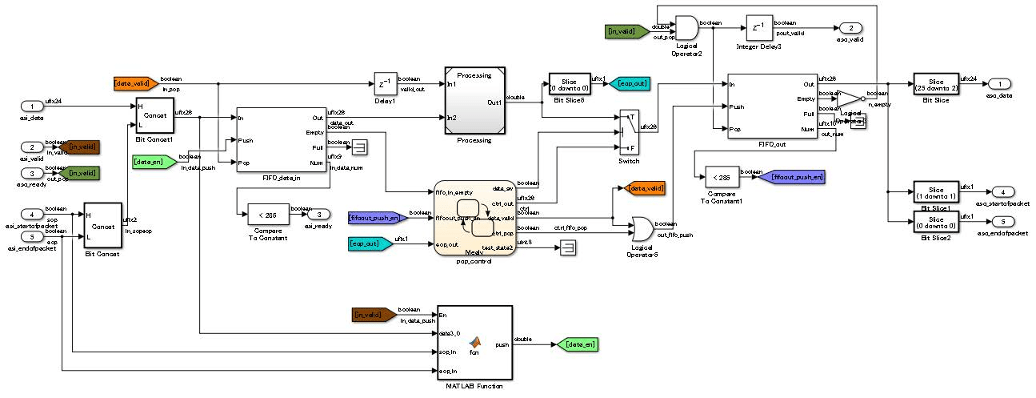

При создании модели Simulink для создания кода HDL используйте блоки Simulink, функциональные блоки MATLAB и блоки Stateflow ® на основе приложения. На этом рисунке показан пример использования различных блоков внутри DUT.

Используйте блоки Simulink для моделирования арифметических алгоритмов, которые выполняют численную обработку или содержат циклы обратной связи.

Используйте функциональные блоки MATLAB для моделирования логики управления, условных ветвей, таких как операторы if-else, и простых конечных автоматов. Функциональные блоки MATLAB можно также использовать для моделирования IP-адреса, написанного с использованием кода MATLAB ®.

Используйте следующие блоки Stateflow для моделирования алгоритма:

Таблица перехода состояний (Stateflow): используйте эти блоки для моделирования конечных автоматов, которые управляют выводом с использованием знаний о прошлом и настоящем.

Диаграмма (Stateflow): используйте эти блоки для моделирования блок-схем с использованием условных ветвей if-else и конечных автоматов, которые управляют выводом с использованием знаний о прошлом и настоящем.

Таблица истинности (Stateflow): используйте эти блоки для моделирования условных ветвей if-else.

Комбинированную логику можно моделировать с помощью блоков Stateflow. Для более сложных операций и операций, изменяющих время, таких как вставка и обработка трубопровода, используйте блоки Simulink. Затем можно использовать логику потока состояний для обработки результата, вычисленного из блоков Simulink.

Для значительно больших алгоритмов, имеющих сложные вычисления, можно разбить конструкцию на иерархию меньших конструкций. Это разделение используется для повторного использования, модульной разработки и ускоренного моделирования. Можно повторно использовать модели, включив их в качестве блоков модели в верхнюю модель. Модель, которая повторно использует этот блок, называется верхней моделью, а блок, который повторно используется или включается в верхнюю модель, называется ссылочной моделью.

Примечание

При создании кода HDL для подсистемы, которая не находится на верхнем уровне модели, HDL Coder™ преобразует подсистему в ссылку модели.

Ссылочная модель обрабатывается аналогично атомной подсистеме. В некоторых случаях потенциально может возникнуть алгебраический цикл и может предотвратить генерацию кода HDL. Чтобы создать код, удалите алгебраический цикл в конструкции или в диалоговом окне «Параметры конфигурации» задайте параметр «Минимизировать вхождения алгебраического цикла».

Для подсистем, которые необходимо смоделировать в проекте и включить созданный код HDL, используйте подсистемы BlackBox. Чтобы создать подсистему BlackBox, установите для архитектуры HDL подсистемы или ссылки на модель значение BlackBox. Эту архитектуру можно использовать для включения рукописного HDL-кода в модель Simulink. Дополнительные сведения см. в разделе Проверка комбинации написанного вручную и сгенерированного кода HDL (HDL Verifier).

Если модель Simulink создается с использованием созданного кода HDL, используйте импорт HDL. Дополнительные сведения см. в разделах Импорт кода Verilog и Создание модели Simulink.

При наличии имитатора ЛПВП, такого как Mentor Graphics ® ModelSim ® или Cadence Incisive ®, можно использовать блоки косимуляции ЛПВП (HDL Verifier) для моделирования кода ЛПВП для DUT и создания экземпляра этого кода ЛПВП в сгенерированном коде.