Консультант по рабочим процессам HDL - это инструмент, поддерживающий набор задач, охватывающих этапы процесса проектирования FPGA. Некоторые задачи выполняют проверку или проверку модели; другие запускают генератор кода HDL или сторонние инструменты. Каждая папка на верхнем уровне помощника по рабочим процессам HDL содержит группу связанных задач, которые можно выбрать и запустить.

Для получения сводной информации о каждой папке или задаче помощника по рабочим процессам HDL выберите папку или значок задачи, а затем нажмите кнопку Справка помощника по рабочим процессам HDL.

Set Target: Задачи в этой категории позволяют выбрать нужное целевое устройство и сопоставить его интерфейс ввода-вывода с входами и выходами модели.

Подготовка модели для генерации кода HDL: Задачи этой категории проверяют модель на совместимость генерации кода HDL. Задачи также сообщают о настройках модели, блоках или других условиях (таких как алгебраические циклы), которые препятствуют генерации кода, и дают рекомендации по устранению таких проблем.

Создание кода HDL: Эта категория поддерживает все связанные с HDL опции диалогового окна «Параметры конфигурации», включая настройку кода HDL и параметров генерации тестового стенда, а также создание кода, тестового стенда или модели косимуляции.

FPGA Synthesis and Analysis: Задачи в этой категории поддерживают:

Синтез и анализ времени посредством интеграции со сторонними инструментами синтеза

Обратная аннотация модели с критическим путем и другой информацией, полученной в ходе синтеза

FPGA-in-the-Loop Implementation: Эта категория реализует фазы FIL, включая генерацию блоков, синтез, логическое отображение, PAR (место и маршрут), генерацию файлов программирования и канал связи. Эти возможности разработаны для конкретной платы и адаптированы к коду RTL. Для FIL требуется лицензия HDL Verifier™.

Загрузить в цель: Задачи в этой категории зависят от выбранного целевого устройства и могут включать:

Создание целевого файла программирования FPGA

Программирование целевого устройства

Создание модели, содержащей подсистему Real-Time™ интерфейса Simulink ®

В папке Set Target можно выбрать целевое устройство FPGA и определить интерфейс, созданный для устройства.

Set Target Device and Synthesis Tool: Выберите целевое устройство FPGA и инструменты синтеза.

Задать целевую ссылочную конструкцию: для IP Core Generation выберите эталонный проект для целевого устройства.

Задать целевой интерфейс: для IP Core Generation, FPGA Turnkey, и Simulink Real Time FPGA I/O используйте таблицу интерфейса целевой платформы для назначения каждого порта DUT ресурсу ввода-вывода на целевом устройстве. Команда Enable HDL DUT port generation for test points используется для создания выходных портов DUT для сигналов тестовых точек в сгенерированном коде HDL.

Set Target Frequency (Задать целевую частоту): выберите целевую тактовую частоту для реализации FPGA проекта.

Для получения дополнительных сведений о каждой задаче Задать цель (Set Target) выберите значок задачи и нажмите кнопку Справка помощника по рабочим процессам HDL (HDL Workflow Advisor Help).

Задание Set Target Device and Synthesis Tool (Задать целевое устройство и средство синтеза) позволяет выбрать целевое устройство FPGA и связанное с ним средство синтеза из раскрывающегося меню, в котором перечислены устройства, которые в настоящее время поддерживает помощник по рабочим процессам HDL.

Эта задача отображает следующие параметры:

Целевой рабочий процесс: раскрывающееся меню, в котором перечислены возможные рабочие процессы, поддерживаемые помощником по рабочим процессам HDL. Выберите один из следующих вариантов:

Общий ASIC/FPGA

FPGA-в-контуре

FPGA «под ключ»

Интерфейс ввода-вывода FPGA в режиме реального времени Simulink

Поколение ядер IP

Настройка устройства USRP

Программно-определяемое радио

Целевая платформа: раскрывающееся меню, в котором перечислены устройства, поддерживаемые в настоящее время помощником по рабочим процессам HDL. Недоступно для общего рабочего процесса ASIC/FPGA.

Инструмент синтеза: выберите инструмент синтеза, затем выберите семейство, устройство, пакет и скорость для цели синтеза.

Если инструмент синтеза не является одним из параметров инструмента синтеза, см. раздел Настройка траектории инструмента синтеза. После настройки траектории инструмента синтеза щелкните Обновить (Refresh), чтобы сделать инструмент доступным в помощнике по рабочим процессам HDL.

Папка проекта: укажите имя папки проекта.

Версия инструмента: этот флажок отображает текущую версию инструмента синтеза.

Примечание

При выборе Intel Quartus Pro или Microsemi Libero SoC в качестве инструмента синтеза можно запустить только Generic ASIC/FPGA workflow-процесс. При использовании этих инструментов задача Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) недоступна. В этом случае можно запустить workflow-процесс для синтеза, а затем просмотреть отчеты о времени для просмотра критического пути.

Задание Задать целевую ссылочную конструкцию (Set Target Reference Design) отображает входные параметры ссылочной конструкции и версию инструмента. В разделе «Параметры ссылочной конструкции» отображаются все пользовательские параметры, заданные для ссылочной конструкции.

Задача отображает следующие параметры:

Ссылочный проект: раскрывающееся меню, в котором перечислены ссылочные проекты, поддерживаемые HDL Coder™, и любые пользовательские ссылочные проекты, которые вы указываете. Дополнительные сведения о создании пользовательской платы и эталонной конструкции см. в разделе Система регистрации плат и эталонных конструкций.

Версия ссылочного инструмента проектирования: текстовое поле, в котором отображается текущая версия ссылочного инструмента проектирования. Рекомендуется использовать ссылочную версию инструмента проектирования, совместимую с поддерживаемой версией инструмента. При несоответствии версий инструментов кодер HDL создает ошибку при выполнении этой задачи. Несоответствие версий инструментов может привести к сбою задачи создания проекта.

Если установлен флажок Игнорировать несоответствие версий инструментов, кодер HDL генерирует предупреждение вместо ошибки. Можно попытаться продолжить создание ссылочного проектного проекта.

Параметры ссылочной конструкции: список параметров ссылочной конструкции. Это могут быть параметры, доступные в ссылочных конструкциях по умолчанию, поддерживаемых кодером HDL, или параметры, определенные для пользовательской ссылочной конструкции. Дополнительные сведения см. в разделе Определение пользовательских параметров и функций обратного вызова для пользовательского ссылочного проекта.

Задача Set Target Interface отображает свойства портов ввода и вывода на DUT и позволяет сопоставить эти порты с ресурсами ввода-вывода на целевом устройстве.

Set Target Interface отображает таблицу интерфейса целевой платформы, которая показывает:

Имя, тип порта (входы и выходы) и тип данных для каждого порта на DUT.

Раскрывающееся меню, в котором перечислены доступные ресурсы ввода-вывода для целевого устройства.

Эти ресурсы зависят от конкретного устройства. Для получения подробной информации о каждом ресурсе см. документацию по вашей плате разработки FPGA.

Укажите целевую частоту для следующих рабочих процессов:

Generic ASIC/FPGAЧтобы указать целевую частоту, которую должен достичь дизайн. Кодер HDL создает файл ограничений синхронизации для этой тактовой частоты и добавляет ограничение в проект инструмента синтеза FPGA, который создается в задаче Создать проект. Если целевая частота не достижима, средство синтеза генерирует ошибку. Целевая частота не поддерживается в микросеми ® Libero ® SoC.

IP Core Generation: Указание целевой частоты для кодера HDL для изменения настройки модуля синхронизации в опорной конструкции для формирования тактового сигнала с этой частотой. Введите целевое значение частоты в диапазоне частот (МГц). Если целевая частота не указана, кодер HDL использует целевую частоту по умолчанию (МГц).

Simulink Real-Time FPGA I/O: Для плат Speedgoat, которые поддерживаются Xilinx ISE, укажите целевую частоту для формирования тактового модуля для формирования тактового сигнала с этой частотой.

Платы Speedgoat, поддерживаемые Xilinx Vivado использовать IP Core Generation инфраструктура рабочих процессов. Укажите целевую частоту для кодера HDL, чтобы изменить настройку модуля синхронизации в опорной конструкции для формирования тактового сигнала с этой частотой. Введите целевое значение частоты в диапазоне частот (МГц). Если целевая частота не указана, кодер HDL использует целевую частоту по умолчанию (МГц).

FPGA TurnkeyГенерация тактового модуля для автоматического формирования тактового сигнала с этой частотой.

Выберите режим синхронизации процессор-FPGA и сопоставьте входные порты DUT, выходные порты и контрольные точки с ресурсами ввода-вывода на целевом устройстве.

Для синхронизации процессора/FPGA выберите:

Бесплатный запуск, если не требуется автоматическая синхронизация процессора и FPGA.

Сопроцессирование - блокировка, если вы хотите, чтобы кодер HDL автоматически генерировал логику синхронизации для FPGA, чтобы процессор и FPGA работали параллельно. Выберите этот режим, когда время выполнения FPGA является коротким по отношению к времени выборки процессора, и необходимо, чтобы FPGA была завершена до продолжения работы процессора.

Сообработка - без блокировки с задержкой (не поддерживается для IP Core Generation workflow), если вы хотите, чтобы кодер HDL автоматически генерировал логику синхронизации для FPGA, чтобы процессор и FPGA работали параллельно. Выберите этот режим, если время обработки FPGA является большим относительно времени выборки процессора, или если не требуется, чтобы процессор ожидал завершения обработки FPGA до продолжения работы процессора.

Эта настройка сохраняется вместе с моделью в качестве ProcessorFPGASynchronization Свойство блока HDL для блока DUT.

Выбор опции Enable HDL DUT port generation for testpoints (Включить создание порта HDL DUT для тестовых

Маркирует сигналы контрольных точек для формирования кода. См. Модель и отладка сигналов контрольных точек с кодером HDL.

Включает опцию Включить генерацию порта HDL DUT для набора конфигурации контрольных точек.

Обновление целевой таблицы интерфейсов для отображения выходных портов контрольных точек в таблице интерфейсов.

В таблице интерфейса целевой платформы отображаются:

Имя, тип порта (вход, выход и контрольная точка) и тип данных для каждого порта на DUT.

Контекстное меню, содержащее список доступных ресурсов ввода-вывода для целевого устройства.

Эти ресурсы зависят от конкретного устройства. Для получения подробной информации о каждом ресурсе см. документацию по вашей плате разработки FPGA.

Выберите режим синхронизации процессор-FPGA и сопоставьте входные и выходные порты DUT с ресурсами ввода/вывода на целевом устройстве. При необходимости укажите ссылочную конструкцию.

Эталонный дизайн: Выберите предопределенный проект интеграции встраиваемой системы, в который HDL Coder вставляет созданное ядро IP.

Путь к ссылочному проекту: введите путь к загруженным ссылочным компонентам проекта. Это поле доступно только в том случае, если для указанной ссылочной конструкции требуются загружаемые компоненты.

Для синхронизации процессора/FPGA выберите:

Бесплатный запуск, если не требуется автоматическая синхронизация процессора и FPGA.

Сопроцессирование - блокировка, если вы хотите, чтобы кодер HDL автоматически генерировал логику синхронизации для FPGA, чтобы процессор и FPGA работали параллельно. Выберите этот режим, когда время выполнения FPGA является коротким по отношению к времени выборки процессора, и необходимо, чтобы FPGA была завершена до продолжения работы процессора.

Сообработка - без блокировки с задержкой (не поддерживается для IP Core Generation workflow), если вы хотите, чтобы кодер HDL автоматически генерировал логику синхронизации для FPGA, чтобы процессор и FPGA работали параллельно. Выберите этот режим, если время обработки FPGA является большим относительно времени выборки процессора, или если не требуется, чтобы процессор ожидал завершения обработки FPGA до продолжения работы процессора.

Эта настройка сохраняется вместе с моделью в качестве ProcessorFPGASynchronization Свойство блока HDL для блока DUT.

Таблица интерфейса целевой платформы показывает:

Имя, тип порта (входы и выходы) и тип данных для каждого порта на DUT.

Раскрывающееся меню со списком доступных ресурсов ввода-вывода для целевого устройства.

Эти ресурсы зависят от конкретного устройства. Для получения подробной информации о каждом ресурсе см. документацию по вашей плате разработки FPGA.

Задачи в папке Prepare Model For HDL Code Generation проверяют модель на совместимость с созданием кода HDL. Если при проверке возникает условие, которое может вызвать предупреждение о создании кода или ошибку, на правой панели помощника по рабочим процессам HDL отображается информация об этом условии и о том, как его исправить. В папке Prepare Model For HDL Code Generation содержатся следующие проверки:

Проверка параметров модели ускоряет проверку модели путем удаления избыточных проверок. Этот чек предоставляет возможность открыть чеки HDL Code Advisor в отдельном окне и выполнить эти чеки.

Проверка совместимости FPGA-in-the-Loop: проверка совместимости модели с FPGA-in-the-loop, в частности:

Не допускается: подсистемы приемника/источника, типы данных один/два, нулевое время выборки

Должна присутствовать лицензия HDL Verifier

Эта опция доступна только при выборе FPGA-in-the-Loop для целевого рабочего процесса.

Проверка совместимости USRP: Модель должна иметь два входных порта и два выходных порта со знаком 16-разрядных сигналов.

Эта опция доступна только при выборе Customization for the USRP Device для целевого рабочего процесса.

Для получения сводной информации о каждой задаче Подготовка модели для создания кода HDL (Prepare Model For HDL Code Generation) выберите значок задачи, а затем нажмите кнопку Справка помощника по рабочим процессам HDL (HDL Workflow Advisor Help).

Флажок Параметры модели (Model Settings) проверяет параметры для всей модели на совместимость генерации кода HDL.

Эта проверка ускоряет проверку модели путем удаления избыточных проверок. Чек предоставляет кнопку для открытия чека HDL Code Advisor в отдельном окне. Следующие проверки были заменены проверками помощника по коду HDL:

Проверьте глобальные параметры.

Проверка алгебраических контуров

Проверка совместимости блоков

Время проверки образцов

При нажатии кнопки Run This Task проверки помощника по коду HDL не открываются.

Флажок Параметры модели (Model Settings) проверяет параметры для всей модели на совместимость генерации кода HDL.

Эта проверка проверяет параметры модели на совместимость с условиями генерации кода HDL и флагов, которые могут вызвать ошибку или предупреждение во время генерации кода. Помощник по рабочим процессам HDL отображает таблицу со следующей информацией о каждом обнаруженном условии:

Блок: гиперссылка на страницу диалогового окна конфигурации модели, содержащую условие ошибки или предупреждения

Параметры: имя параметра модели, вызвавшего ошибку или условие предупреждения

Текущее: текущее значение параметра

Рекомендуется: Рекомендуемое значение параметра

Степень серьезности: уровень серьезности предупреждения или состояния ошибки. Как минимум, необходимо исправить параметры, помеченные как error.

Чек также предоставляет кнопку для открытия помощника по коду HDL в отдельном окне. Помощник по коду HDL может выполнять дополнительные проверки совместимости генерации кода HDL, не охваченные этой задачей. Дополнительные сведения см. в разделе Проверки конфигурации модели.

Совет

Чтобы задать рекомендуемые значения параметров отчета, нажмите кнопку «Изменить все». Затем можно снова выполнить проверку и перейти к следующей проверке.

При нажатии кнопки Run This Task проверки помощника по коду HDL не открываются.

Обнаружение алгебраических циклов в модели.

Программное обеспечение HDL Coder не поддерживает генерацию кода HDL для моделей, в которых существуют алгебраические условия цикла. Команда Проверить алгебраические циклы (Check Algebraic Loops) проверяет модель и не выполняет проверку, если она обнаруживает алгебраический цикл. Устраните алгебраические циклы из модели, прежде чем продолжить проверку или генерацию кода ПО HDL Workflow Advisor.

Проверьте DUT на наличие неподдерживаемых блоков.

Проверка совместимости блоков проверяет блоки в DUT на совместимость с генерацией кода HDL. Проверка завершается неуспешно, если обнаруживаются блоки, которые кодер HDL не поддерживает. Помощник по рабочим процессам HDL сообщает о несовместимых блоках, включая полный путь к каждому блоку.

Проверьте решатель, время выборки и настройки режима задания для модели.

Check Sample Times проверяет параметры решателя, время выборки, режим задания и диагностику перехода скорости для совместимости генерации кода HDL. Параметры решателя, которые требует или рекомендует программное обеспечение HDL Coder:

Тип: Фиксированный шаг. (Кодер в настоящее время поддерживает решатели с переменным шагом в ограниченных условиях. Посмотрите hdlsetup для получения подробной информации.)

Решатель: Дискретный (без непрерывных состояний). Можно выбрать другие решатели с фиксированным шагом, но эта опция обычно является лучшей для моделирования дискретных систем.

Режим задания: SingleTasking. В настоящее время кодер не поддерживает модели, выполняющиеся в многозадачном режиме. Не устанавливать режим задания в Auto.

Параметры диагностики многозадачной скорости и однозадачной скорости: значение Error.

HDL Verifier проверяет модель на совместимость с обработкой FPGA-in-the-loop.

Подготовка DUT к генерации интерфейса FIL (верификатор HDL).

Задачи в папке Создание кода HDL позволяют:

Установка и проверка параметров формирования кода HDL и тестового стенда. Большинство параметров панели Создание кода HDL (HDL Code Generation) диалогового окна Параметры конфигурации (Configuration Parameters) и Проводника моделей (Model Explorer) поддерживаются.

Создать любое или все из:

Код RTL

Испытательный стенд RTL

Модель косимуляции

Испытательный стенд SystemVerilog DPI

Для автоматического выполнения задач в папке «Создание кода HDL» выберите папку и нажмите кнопку «Выполнить все».

Совет

После выполнения каждой задачи в этой папке кодер HDL обновляет диалоговое окно Параметры конфигурации (Configuration Parameters) и Обозреватель моделей (Model Explorer).

Дополнительная задача для открытия окна параметров конфигурации кодера HDL.

Настройка параметров HDL является необязательной задачей. Эта задача позволяет открыть диалоговое окно Параметры конфигурации кодера HDL (HDL Coder Configuration Parameters) в отдельном окне. Изменения параметров конфигурации используются в следующей задаче помощника по рабочим процессам кодера HDL.

Примечание

Перед выполнением этой задачи закройте диалоговое окно «Параметры конфигурации кодера HDL».

Если для текущей тестируемой конструкции (DUT) открыто окно «Помощник по рабочим процессам» (Workflow Advisor), для редактирования отключены следующие параметры конфигурации:

Имя модели или подсистемы DUT.

Имя и путь к папке создания целевого кода.

Имя инструмента синтеза.

Выбор семейства устройств.

Выбор устройства.

Выбор пакета устройства.

Выбор скорости устройства.

Целевая частота.

При внесении изменений в эти параметры конфигурации повторно запустите все предыдущие задачи помощника по рабочим процессам.

Задайте параметры, влияющие на общую генерацию кода.

Задача «Задать основные параметры» задает параметры, которые являются фундаментальными для создания кода HDL. Эти параметры включают в себя выбор DUT и выбор целевого языка. Основные параметры те же, что и на панели «Создание кода HDL» верхнего уровня диалогового окна «Параметры конфигурации», за исключением того, что группа вывода «Создание кода» опущена.

Задайте параметры, определяющие разделы, которые должны отображаться в отчете о создании кода.

Опции аналогичны тем, которые находятся на панели Создание кода HDL (HDL Code Generation) > Отчет (Report) диалогового окна Параметры конфигурации (Configuration Parameters) и в Обозревателе моделей (Model Explorer).

Задайте параметры, определяющие подробные характеристики создаваемого кода.

Дополнительные опции аналогичны тем, которые находятся на панели Создание кода HDL (HDL Code Generation) > Глобальные настройки (Global Settings) диалогового окна Параметры конфигурации (Configuration Parameters) и в Обозревателе моделей (Model Explorer).

Задайте параметры, определяющие оптимизации, такие как совместное использование ресурсов и конвейерная обработка, для улучшения области и синхронизации.

Опции оптимизации те же, что и на панели Создание кода HDL (HDL Code Generation) > Цель и оптимизация (Target and Optimizations) диалогового окна Параметры конфигурации (Configuration Parameters) и Проводника моделей (Model Explorer).

Установите опции, определяющие характеристики сформированного кода стенда.

Параметры тестового стенда те же, что и на панели «Создание кода HDL» (HDL Code Generation) > «Тестовое стенд» (Test Bench) диалогового окна «Параметры конфигурации» (Configuration Parameters) и «Обозреватель моделей» (Model Explorer).

Создайте код RTL и оболочку верхнего уровня HDL.

Задача Generate RTL Code генерирует код RTL и оболочку верхнего уровня HDL для подсистемы DUT. Он также создает файл ограничений, содержащий информацию о сопоставлении контактов и ограничения синхронизации.

Выберите и инициируйте создание кода RTL, тестового стенда RTL и модели косимуляции.

Задача Генерировать код RTL (Generate RTL Code) и Тестбэнч (Testbench) позволяет выбрать тип кода или модели, которую требуется создать. Можно выбрать любую комбинацию из следующих:

Создать код RTL: Создать код RTL на целевом языке.

Создать тестовый стенд: создать тестовый стенд (ы), выбранный в параметрах Set Testbench.

Создать модель проверки: создать модель проверки, которая выделяет сгенерированные задержки и другие различия между исходной моделью и созданной моделью косимуляции. С помощью модели проверки можно наблюдать эффекты потоковой передачи, совместного использования ресурсов и балансировки задержек.

Модель проверки содержит DUT из исходной модели и DUT из созданной модели косимуляции. С помощью модели проверки можно проверить, что выходные данные оптимизированной DUT являются битово верными результатам, полученным исходной DUT.

Создание модели симулятора для косимуляции с помощью имитатора ЛПВП (кодер ЛПВП для проектирования фильтров).

Выполните этот шаг для проверки созданного ЛПВП с помощью косимуляции между имитатором ЛПВП и испытательным стендом Simulink. Этот шаг показывает, только если выбрана модель Cosimulation и указан имитатор ЛПВП в окне Задать параметры тестирования (Set Testbench Options).

Выберите и инициируйте создание кода RTL и пользовательского IP-ядра.

В задаче Создать код RTL и ядро IP укажите характеристики сгенерированного ядра IP:

Имя ядра IP: Введите имя ядра IP.

Эта настройка сохраняется вместе с моделью в качестве IPCoreName Свойство блока HDL для блока DUT.

Версия ядра IP: введите номер версии ядра IP. Кодер HDL добавляет номер версии к имени ядра IP для создания имени папки вывода.

Эта настройка сохраняется вместе с моделью в качестве IPCoreVersion Свойство блока HDL для блока DUT.

Основная папка IP (не редактируемая): Кодер HDL генерирует основные файлы IP в выводимой папке, включая документацию HTML.

IP-репозиторий: Если у вас есть папка IP-репозитория, введите ее путь вручную или с помощью кнопки Обзор. Кодер копирует сгенерированное ядро IP в папку репозитория IP.

Дополнительные исходные файлы: Если в проекте используется интерфейс черного ящика для включения существующего кода Verilog ® или VHDL ®, введите имена файлов. Введите имя каждого файла вручную, разделяя его точкой с запятой (;) или с помощью кнопки «Добавить». Язык исходного файла должен совпадать с целевым языком.

Эта настройка сохраняется вместе с моделью в качестве IPCoreAdditionalFiles Свойство блока HDL для блока DUT.

Размер буфера захвата данных FPGA: укажите размер памяти в сформированном ядре IP. Ширина памяти представляет собой общую битовую ширину сигналов данных. Размер буфера использует значения, равные 128 * (2n), где n - целое число. По умолчанию размер буфера равен128 (n = 0). Максимальное значение n равно 13, что означает, что максимальное значение размера буфера составляет 128 * (213) = 1048576.

Эта настройка сохраняется вместе с моделью в качестве IPDataCaptureBufferSize Свойство блока HDL для блока DUT.

Максимальная глубина последовательности захвата данных FPGA: укажите максимальную глубину последовательности для сбора данных из FPGA в одном или нескольких триггерных этапах. Максимальная глубина последовательности - целое число в диапазоне от 1 до 10. По умолчанию максимальная глубина последовательности равна 1. Чтобы захватить указанные данные, предоставив набор условий запуска в несколько этапов, установите максимальную глубину последовательности больше 1.

Эта настройка сохраняется вместе с моделью в качестве IPDataCaptureSequenceDepth Свойство блока HDL для блока DUT.

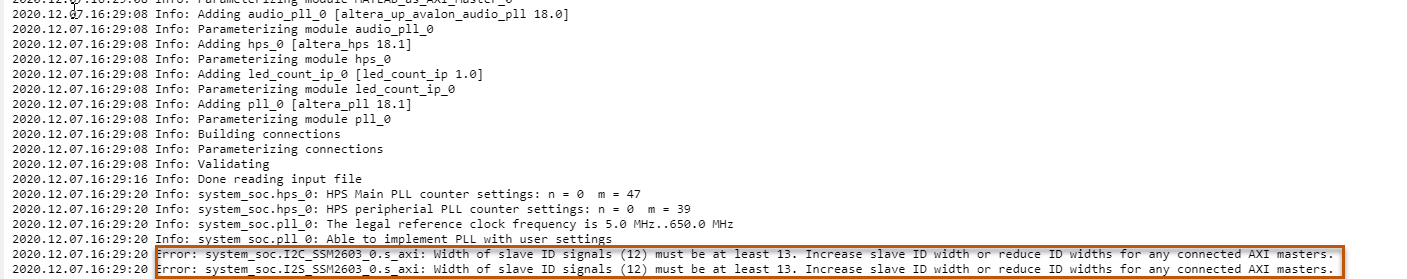

Когда Вы выбираете Вставку JTAG MATLAB как Владелец AXI, AXI4-рабское значение Ширины удостоверения личности приспособлено для IP ядра DUT, которое производит Кодер HDL. Когда Вы выбираете Вставку JTAG MATLAB как Владелец AXI и добавляете таможенные IP, Вы должны определить новое приспособленное рабское значение ширины удостоверения личности. Например, когда Вы выбираете Вставку JTAG MATLAB как Владелец AXI и добавляете таможенные IP, если Вы получаете это сообщение об ошибке во время Создать задачи Проекта:

Восстановите IP-ядра, установив целевую платформу как Generic Intel или Generic Xilinx. Затем сопоставьте один из портов DUT с интерфейсом AXI4, вычислите новую ширину с помощью New width = Base Width + log2(Number of AXI Masters +1)и введите вычисленное значение ширины в поле AXI4 Slave ID width ". Добавьте регенерированные IP-ядра с новыми значениями ширины в папку ссылочного проекта. Щелкните правой кнопкой мыши «Создать проект» и выберите «Выполнить до выбранной задачи». В этом примере два пользовательских IP-адреса являются I2C и I2s. Новая расчетная ширина равна 13.

Создать отчет по IP-ядру: оставить этот параметр выбранным для создания HTML-документации по IP-ядру.

Позвольте readback на рабе AXI4, пишут регистры: Выберите этот выбор, если Вы хотите прочитать назад стоимость, которая написана спискам рабов AXI4 при помощи рабского интерфейса AXI4. При выполнении этой задачи генератор кода добавляет мультиплексор для каждого регистра AXI4 в логике декодера адресов. Этот мультиплексор сравнивает адрес, на который записываются данные при чтении значений. При чтении из нескольких AXI4 подчиненных регистров логика обратного считывания становится длинной мультиплексорной цепью, которая может влиять на частоту синтеза.

Эта настройка сохраняется вместе с моделью в качестве AXI4RegisterReadback Свойство блока HDL для блока DUT.

Generate default AXI4 slave interface: оставьте этот параметр выбранным, если вы хотите создать ядро IP HDL с AXI4 slave interface для таких сигналов, как часы, сброс, готовность, метка времени и так далее. Если требуется создать общее IP-ядро HDL без AXI4 подчиненных интерфейсов, снимите этот флажок. Кроме того, убедитесь, что ни один из портов DUT не сопоставлен с AXI4 или AXI4-Lite интерфейсами. Можно сопоставить порты только с внешними или внутренними интерфейсами ввода-вывода или AXI4-Stream интерфейсом с отображением TLAST.

Эта настройка сохраняется вместе с моделью в качестве GenerateDefaultAXI4Slave Свойство блока HDL для блока DUT.

Создание проектов для поддерживаемых инструментов синтеза FPGA, выполнение задач синтеза FPGA, отображения и размещения/маршрутизации, а также аннотирование критических путей в исходной модели

Задачи в папке FPGA Synthesis and Analysis позволяют:

Создание проектов синтеза FPGA для поддерживаемых инструментов синтеза FPGA.

Запуск поддерживаемых инструментов синтеза FPGA с использованием файлов проекта для выполнения задач синтеза, отображения и размещения/маршрутизации.

Аннотирование исходной модели с помощью информации о критическом пути, полученной из инструментов синтеза.

Список поддерживаемых средств синтеза сторонних производителей см. в разделе Средства синтеза сторонних производителей и поддержка версий.

Задачи в папке:

Создать проект

Выполнение синтеза и P/R

Аннотирование модели с результатом синтеза

Создание проекта синтеза FPGA для поддерживаемого инструмента синтеза FPGA.

Эта задача создает проект синтеза для выбранного инструмента синтеза и загружает проект с кодом HDL, созданным для модели.

По завершении создания проекта помощник по рабочим процессам HDL отображает ссылку на проект на правой панели. Щелкните эту ссылку, чтобы просмотреть проект в окне проекта инструмента синтеза.

Выберите цель синтеза для создания команд Tcl оптимизации для конкретного инструмента для проекта. При указании None, команды РУД не формируются.

Сведения о сопоставлении целей синтеза командам Tcl см. в разделе Отображение целей синтеза командам Tcl.

Введите дополнительные исходные файлы HDL, которые необходимо включить в проект синтеза. Введите имя каждого файла вручную, разделяя его точкой с запятой (;) или с помощью кнопки «Добавить источник».

Например, можно включить исходные файлы HDL (.vhd или .v) или файл ограничений (.ucf или .sdc).

Введите дополнительные файлы Tcl создания проекта, которые необходимо включить в проект синтеза. Введите имя каждого файла вручную, разделяя его точкой с запятой (;) или с помощью кнопки Add Tcl.

Например, можно включить сценарий Tcl (.tcl) для выполнения после создания проекта.

Запуск поддерживаемых средств синтеза FPGA для выполнения задач синтеза, картирования и размещения/маршрутизации.

Задачи в папке Perform Synthesis and P/R позволяют запустить поддерживаемое средство синтеза FPGA и:

Синтезируйте сгенерированный код HDL.

Выполните сопоставление и анализ синхронизации.

Выполнение функций места и маршрута.

Список поддерживаемых средств синтеза сторонних производителей см. в разделе Средства синтеза сторонних производителей и поддержка версий.

Запустите поддерживаемое средство синтеза FPGA и синтезируйте сгенерированный код HDL.

Задача «Выполнение логического синтеза»:

Запускает инструмент синтеза в фоновом режиме.

Открывает ранее созданный проект синтеза, компилирует код HDL, синтезирует дизайн и генерирует списки соединений и связанные файлы.

Отображает журнал синтеза в субпане Result.

Запускает поддерживаемое средство синтеза FPGA и сопоставляет конструкцию синтезированной логики с целевой FPGA.

Задача «Выполнение сопоставления»:

Запускает инструмент синтеза в фоновом режиме.

Выполняет процесс отображения, который сопоставляет конструкцию синтезированной логики с целевым FPGA.

Выдает файл описания канала для использования в фазе размещения и трассы.

Также выдает информацию о времени предварительной маршрутизации для использования в анализе критического пути и обратной аннотации исходной модели.

Отображает журнал в подпанели Результат.

Включите функцию Skip pre-route timing analysis, если сервисная программа не поддерживает раннюю оценку синхронизации. Если эта опция включена, задача «Аннотировать модель с результатом синтеза» устанавливает критический источник пути на пост-маршрут.

Запускает инструмент синтеза в фоновом режиме и запускает процесс Place and Route.

Задача «Выполнить размещение и трассировку»:

Запускает инструмент синтеза в фоновом режиме.

Выполняет процесс Place and Route, который берет описание канала, созданное предыдущим процессом отображения, и выдает описание канала, подходящее для программирования FPGA.

Также выдает информацию о времени после маршрутизации для использования в анализе критического пути и обратной аннотации исходной модели.

Отображает журнал в подпанели Результат.

Совет

Если выбрать Пропустить эту задачу (Skip this task), помощник по рабочим процессам HDL выполнит рабочий процесс, но пропустит задачу Выполнить размещение и маршрут (Perform Place and Route), пометив ее Passed. Можно выбрать Пропустить эту задачу, если вы предпочитаете выполнять работу по месту и маршруту вручную.

Совет

Если Выполнить размещение (Perform Place) и Маршрут (Route) не удается, но необходимо использовать результаты синхронизации после отображения для поиска критических путей в модели, можно выбрать Игнорировать ошибки места и маршрута (Ignore place and route errors) и перейти к задаче Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result).

Запускает Xilinx ® Vivado ® и выполняет этап синтеза Vivado.

Включите функцию Skip pre-route timing analysis, если не требуется выполнять раннюю оценку синхронизации.

Запускает Xilinx Vivado и выполняет шаг реализации Vivado.

Если выбрать Пропустить эту задачу, помощник по рабочим процессам HDL пропустит задачу Выполнить реализацию, пометив ее Passed. Выберите Пропустить эту задачу, если вы предпочитаете выполнять работу по месту и маршруту вручную.

При сбое реализации прогона можно выбрать Игнорировать ошибки размещения и маршрутизации и перейти к задаче Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result).

Если во время выполнения этой задачи возникают сбои синхронизации, задача не завершается неуспешно. Необходимо проверить отчет синхронизации на наличие сбоев синхронизации.

Анализирует информацию о времени до или после маршрутизации и визуально выделяет критические пути в модели.

Задача Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) помогает определить критические пути в модели. При выборе этой опции задача анализирует информацию о времени до или после маршрутизации, создаваемую группой задач «Выполнение синтеза и P/R», и визуально выделяет один или несколько критических путей в модели.

Примечание

При выборе Intel Quartus Pro или Microsemi Libero SoC как инструмент синтеза, задача Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) недоступна. В этом случае можно запустить workflow-процесс для синтеза, а затем просмотреть отчеты о времени для просмотра критического пути.

Если в задаче Создать код RTL (Generate RTL Code and Testbench) выбрана оболочка верхнего уровня Generate FPGA, команда Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) недоступна. Для выполнения обратного анализа аннотаций снимите флажок «Создать оболочку верхнего уровня FPGA».

Выберите предварительную или последующую трассировку.

Опция pre-route недоступна, если в предыдущей группе задач активизирован анализ синхронизации перед маршрутом.

Можно аннотировать до 3 критических путей. Выберите количество контуров, которые требуется аннотировать.

Отображение критических путей, включая повторяющиеся пути.

Показывать только первый экземпляр дублированного пути.

Аннотируйте совокупную задержку синхронизации на каждом тракте.

Показывает конечные точки каждого тракта, но пропускает соединительные сигнальные линии.

Когда задача Аннотировать модель с результатом синтеза (Annotate Model with Synthesis Result) завершается, кодер HDL отображает DUT с выделенной информацией о критическом пути.

Папка Download to Target поддерживает следующие задачи:

Создание файла программирования: создание файла программирования FPGA.

Program Target Device: Загрузка созданного файла программирования на целевую плату разработки.

Создание интерфейса Simulink Real-Time (только для целевых устройств Speedgoat): создание модели, содержащей подсистему интерфейса Simulink Real-Time.

Для получения сводной информации о каждой задаче Загрузить в цель (Download to Target) выберите значок задачи и нажмите кнопку Справка помощника по рабочим процессам HDL (HDL Workflow Advisor Help).

Задача «Создать файл программирования» создает файл программирования FPGA, совместимый с выбранным целевым устройством.

Задача Program Target Device загружает созданный файл программирования FPGA на выбранное оконечное устройство.

Перед выполнением задачи Program Target Device убедитесь, что хост-компьютер правильно подключен к целевой плате разработки через необходимый кабель программирования.

Задача «Создать интерфейс Simulink в реальном времени» создает модель, содержащую подсистему интерфейса, которую можно подключить к модели Simulink в реальном времени.

Соглашение об именовании для созданной модели:

gm_fpgamodelname_slrt

где fpgamodelname - имя исходной модели.

Текущие настройки помощника по рабочим процессам HDL можно сохранить в именованной точке восстановления. Позже эти параметры можно восстановить, загрузив данные точек восстановления в помощник по рабочим процессам HDL.

Установите параметры FIL и выполните обработку FIL.

Установите тип соединения, IP-адрес платы и MAC-адреса и при необходимости выберите дополнительные файлы.

Выберите либо JTAG(только платы Altera ®) илиEthernet.

Используйте эту опцию для установки IP-адреса платы, если он не является IP-адресом по умолчанию (192.168.0.2).

В большинстве случаев изменение MAC-адреса платы не требуется. Это необходимо при подключении нескольких плат разработки FPGA к одному компьютеру (для которых для каждой платы требуется отдельная сетевая карта). Необходимо изменить MAC-адрес платы для дополнительных плат, чтобы каждый адрес был уникальным.

При необходимости выберите дополнительные исходные файлы для проекта HDL, которые должны быть проверены на плате FPGA. Помощник по рабочим процессам HDL пытается определить тип файла; измените тип файла в столбце «Тип файла», если он неверен.

В процессе построения выполняются следующие действия.

FPGA-in-the-loop генерирует блок FIL с именем модуля верхнего уровня и помещает его в новую модель.

После создания новой модели FIL открывает командное окно. В этом окне программное обеспечение проектирования FPGA выполняет синтез, подгонку, локализацию и трассировку, анализ синхронизации и генерацию файлов программирования FPGA. По завершении процесса в командной строке появится сообщение с предложением закрыть окно.

FPGA-in-the-loop строит модель испытательного стенда вокруг сгенерированного блока FIL.

Модель должна иметь два входных порта и два выходных порта со знаком 16-разрядных сигналов.

На этом шаге инициируется создание файла программирования FPGA. В поле «Входные параметры» введите путь к ранее загруженным файлам Ettus Research™ USRP™ FPGA. Если эти файлы еще не загружены, см. документацию «Пакет поддержки радиоприемника USRP».

По завершении этого шага см. инструкции по загрузке файла программирования в FPGA и запуску моделирования в документации по поддержке радиоканала USRP для FPGA Targeting.

DUT должен соответствовать определенным требованиям к сигнальному интерфейсу. Во время проверки совместимости SDR выполняются следующие проверки интерфейса (входы и выходы проходят те же проверки).

Должен включать одиночный комплексный сигнал, два скалярных сигнала или одиночный векторный сигнал размера 2

Должна иметь битовую ширину 16

Необходимо подписать

Должна быть разовая ставка

Если имеются векторизированные порты, необходимо использовать параметр Scalarize Vectors

При наличии нескольких скоростей необходимо использовать Single clock

Необходимо использовать синхронный сброс

Необходимо использовать сброс с высоким уровнем активности

Необходимо использовать коэффициент оверклокинга пользователя, равный 1

Все проверки ошибок выполняются для данного выполнения задачи и отражаются в таблице. Это позволяет одной итерации исправить все ошибки.

SDR FPGA интегрирует логику заказчика, сформированную на предыдущих этапах, а также специфический для SDR код для обеспечения каналов передачи данных и управления между платой RF и хостом.

Этот шаг состоит из следующих задач:

Настройка параметров SDR: выбор параметров настройки.

Создание SDR: создание файла программирования FPGA для цели SDR.

Выберите опции настройки для завершения внедрения SDR FPGA.

Плата RF для цели

Выберите один из следующих вариантов:

Epic Bitshark FMC-1Rx RevB

Epic Bitshark FMC-1Rx RevC

Папка с исходным кодом HDL поставщика

Укажите папку, содержащую HDL радиочастотного интерфейса, загруженную с сайта поддержки поставщика. Используйте Обзор, чтобы перейти к нужной папке.

Частота синтеза пользовательской логики

Укажите максимальную частоту запуска проекта. Это значение должно быть больше частоты дискретизации для ADC и DAC, как указано в блоке ADI FMCOMMS или Epiq Bitshark™.

Путь к логическим данным пользователя

Выберите либо Receiver data path или Transmitter data path.

IP-адрес платы

Установите IP-адрес платы в этом поле, если он не является IP-адресом по умолчанию (192.168.10.1).

MAC-адрес платы

В большинстве случаев изменение MAC-адреса платы не требуется. Однако это необходимо при подключении нескольких плат разработки FPGA к одному компьютеру (для которых для каждой платы требуется отдельная сетевая карта). Необходимо изменить MAC-адрес платы для дополнительных плат, чтобы каждый адрес был уникальным.

Укажите файлы, которые требуется включить в проект ISE или Vivado. Следует включать только типы файлов, поддерживаемые ISE или Vivado. Если включенный файл не существует, помощник по рабочим процессам HDL не может создать проект.

Файл: Имя файла, добавленного в проект (с помощью команды «Добавить»).

Тип файла: Тип файла. Программа попытается определить тип файла автоматически, но выбор можно переопределить. Опции: VHDL, Verilog, EDIF netlist, VQM netlist, QSF file, Constraints, и Others.

Добавить: Добавить новый файл в список.

Удалить: удаление выбранного файла из списка.

Вверх: перемещает выбранный файл вверх по списку.

Вниз: перемещает выбранный файл вниз по списку.

Показать полные пути к исходным файлам (флажок): запускает отображение полного пути. Если этот флажок не установлен, отображается только имя файла.

Консультант по рабочим процессам HDL создает новый проект Xilinx ISE или Vivado и добавляет следующее:

Все необходимые файлы из репозитория FPGA

Созданные файлы HDL для выбранной подсистемы и алгоритма

Если при создании проекта FPGA и проверке синтаксиса ошибок не обнаружено, запускается процесс создания файла программирования FPGA. Этот процесс можно просмотреть во внешней командной оболочке и контролировать его ход. После завершения процесса в окне команд появится сообщение с предложением закрыть окно.

Задачи в этой папке интегрируют сгенерированное IP-ядро HDL со встроенным процессором.

Создание проекта для встроенного системного инструмента.

В окне сообщения после создания проекта можно щелкнуть ссылку на проект, чтобы открыть созданный проект встроенного системного инструмента.

Инструмент для разработки встраиваемых систем.

Папка, в которой сохраняются созданные файлы проекта.

Выберите цель синтеза для создания команд Tcl оптимизации для конкретного инструмента для проекта. При указании None, команды РУД не формируются.

Сведения о сопоставлении целей синтеза командам Tcl см. в разделе Отображение целей синтеза командам Tcl.

Создайте модель программного интерфейса или скрипт или оба с блоками драйверов ядра IP для генерации встроенного кода C.

После создания модели программного интерфейса можно создать код C из него с помощью Embedded Coder ®. Сценарий содержит команды, которые позволяют подключаться к целевому оборудованию, а также выполнять запись в сгенерированное ядро IP или чтение из него с помощью блоков драйверов AXI.

Если снять флажки Создать модель интерфейса программного обеспечения Simulink (Generate Simulink software interface model) и Создать сценарий интерфейса программного обеспечения MATLAB (Generate MATLAB software interface script), эта задача будет пропущена.

Операционная система: Выберите целевую операционную систему.

Создание битового потока для встроенной системы.

Включите этот параметр, чтобы запустить процесс сборки параллельно с MATLAB ®. Если этот параметр отключен, нельзя использовать MATLAB до завершения построения.

Чтобы настроить сборку синтеза, сохраните пользовательские команды Tcl в файле и выберите Custom. Введите путь к файлу вручную или с помощью кнопки «Обзор». Содержимое пользовательского файла Tcl вставляется между командами Tcl, открывающими и закрывающими проект.

При выборе Custom и хотят генерировать битовый поток, команда TCl генерации битового потока должна ссылаться на имя и местоположение верхнего файла или прямо, или неявно. Например, следующая команда Xilinx Vivado Tcl генерирует битовый поток и неявно ссылается на имя и расположение верхнего файла:

launch_runs impl_1 -to_step write_bitstream

Выберите этот параметр, чтобы ускорить время генерации битового потока с помощью контрольной точки конструкции предыдущей сборки. Эта опция доступна только при использовании инструмента синтеза Xilinx Vivado.

Чтобы использовать этот параметр, выберите Включить контрольную точку проекта с маршрутизацией для построения. Для использования файла контрольных точек проекта с маршрутизацией по умолчанию выберите Default. Расположение файла по умолчанию: hdl_prj\checkpoint\system_routed.dcp. Чтобы использовать пользовательский файл контрольных точек проекта с маршрутизацией, выберите Custom и укажите путь к пользовательскому расположению файла. Эта опция доступна только при использовании инструмента синтеза Xilinx Vivado.

Чтобы использовать этот параметр, выберите Custom для маршрутизируемого файла контрольной точки проекта для построения. Эта опция используется для указания на пользовательский файл контрольной точки проекта с маршрутизацией. После завершения формирования битового потока новый файл проекта маршрутизируемой контрольной точки будет записан в расположение, указанное в файле Routed design checkpoint. Эта опция доступна только при использовании инструмента синтеза Xilinx Vivado.

Сократите время генерации битового потока за счет использования нескольких логических ядер ПК. Этот параметр используется для выбора максимального количества используемых ядер ПК. Выбор synthesis tool default выбирает максимальное количество ядер, заданное в инструменте синтеза. Чтобы вручную выбрать максимальное количество ядер между 2 и 32.

Программирование подключенного целевого устройства SoC. Укажите метод программирования для целевого устройства:

JTAG: Использует кабель JTAG для программирования целевого устройства SoC.

Download: Это метод программирования по умолчанию. Копирование сгенерированного битового потока FPGA, дерева устройств и сценариев инициализации системы на карту SD на плате Zynq и постоянное сохранение битового потока на карте SD. Для использования этого метода программирования лицензия Embedded Coder не требуется. Можно создать объект SSH, указав IP-адрес, имя пользователя SSH и пароль SSH. Кодер HDL использует объект SSH для копирования потока битов на карту SD и перепрограммирования платы.

Чтобы определить собственную функцию для программирования целевого устройства в пользовательском эталонном проекте, можно использовать Custom

Метод программирования. Для использования пользовательского программирования зарегистрируйте дескриптор функции пользовательского программирования с помощью CallbackCustomProgrammingMethod способ hdlcoder.ReferenceDesign класс. Например:

hRD.CallbackCustomProgrammingMethod = ...

@parameter_callback.callback_CustomProgrammingMethod;Дополнительные сведения см. в разделе Программные целевые платы FPGA или устройства SoC.