Можно создать многоразовое ядро HDL IP для любого поддерживаемого устройства Xilinx ® или Altera ® FPGA. Рабочий процесс создает отчет о ядре IP, в котором отображается конфигурация целевого интерфейса и заданные параметры кодера. См. раздел Пользовательское поколение ядра IP.

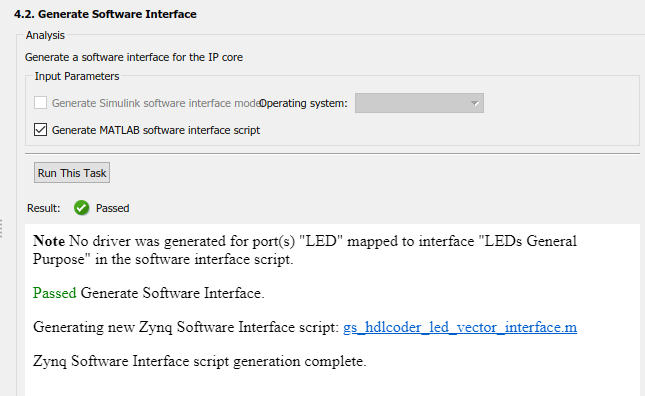

При необходимости можно создать собственные пользовательские ссылочные конструкции и интегрировать сгенерированное ядро IP в ссылочную конструкцию. Для рабочего процесса не требуется программное обеспечение Embedded Coder ®, поскольку не требуется создавать встроенный код, выполняемый на процессоре. Это означает, что рабочий процесс имеет задачу Создать программный интерфейс, но создать модель программного интерфейса невозможно. Если установлен HDL Verifier™, в задании Set Target Reference Design (Задать целевое эталонное проектирование) установите значение Insert JTAG MATLAB as AXI Master (требуется верификатор HDL) равнымon. Затем можно создать сценарий интерфейса программного обеспечения в задаче Создать интерфейс программного обеспечения (Generate Software Interface) для быстрого прототипирования и тестирования основных функций HDL IP с помощью MATLAB AXI Master. См. раздел Создание сценария интерфейса программного обеспечения для проверки и быстрого создания прототипа IP-ядра HDL.

Рабочий процесс для плат FPGA имеет следующие функции:

Задание целевой ссылочной конструкции. Заполнение ссылочной конструкции, ее версии инструмента и заданных параметров.

Задание целевого интерфейса. Сопоставьте порты DUT интерфейсам на целевой платформе.

Задание целевой частоты. Задает целевую частоту (МГц) для изменения модуля синхронизации в опорной конструкции для формирования тактового сигнала с этой частотой.

Создание кода RTL и задачи IP Core. Создает многоразовое и совместно используемое ядро IP. Ядро IP упаковывает код RTL, файл заголовка C и файлы определения ядра IP.

Создать задачу проекта. Создает проект для интеграции ядра IP в предопределенные ссылочные проекты.

Можно создать ядро IP с дополнительным AXI4 или интерфейсом AXI4-Lite.

На этом рисунке показано, как HDL Coder™ генерирует ядро IP с интерфейсом AXI4 и интегрирует ядро IP в эталонную конструкцию FPGA. См. Система регистрации системных плат и эталонных конструкций.

Используйте сгенерированный AXI4-Lite интерфейс кодера HDL для соединения ядра IP с устройством AXI4 или AXI4-Lite Master, например:

Процессор MicroBlaze.

Процессор Nios II.

PCIe Endpoint, который подключается к внешнему процессору.

Мастер JTAG.

При подключении IP-ядра HDL к процессору, такому как MicroBlaze, необходимо интегрировать рукописный код C для запуска на процессоре. В сгенерированном базовом отчете IP отображается информация о сопоставлении адресов регистров. Эта информация о сопоставлении используется для поиска смещений регистров в пространстве регистров ядра IP. Чтобы получить адрес памяти каждого регистра, добавьте смещение регистра к базовому адресу, указанному в ссылочной конструкции. Смещения регистров также можно найти в файле заголовка C в созданной основной IP-папке.

В функции определения ссылочного проекта можно создавать собственные пользовательские ссылочные проекты без AXI4 подчиненного интерфейса. См. также addAXI4SlaveInterface.

При создании пользовательской эталонной конструкции для назначения автономной платы FPGA используйте EmbeddedCoderSupportPackage способ hdlcoder.ReferenceDesign класс:

hRD.EmbeddedCoderSupportPackage = ... hdlcoder.EmbeddedCoderSupportPackage.None;

EmbeddedCoderSupportPackage.Кодер HDL поддерживает эти платы FPGA с IP Core Generation рабочий процесс:

Xilinx Kintex-7 KC705 development board

Arrow DECA MAX 10 FPGA evaluation kit

С помощью этих плат можно интегрировать сгенерированное ядро IP в default system эталонный проект. По умолчанию эта ссылочная конструкция не имеет AXI4 подчиненного интерфейса. Дополнительно можно добавить интерфейс в функцию определения ссылочного проекта.

IP Core Generation рабочий процесс не поддерживает:

Для архитектуры ОЗУ установлено значение Generic RAM without clock enable.

Использование различных часов для ядра IP и интерфейса AXI. IPCore_Clk и AXILite_ACLK должна быть синхронной и подключенной к одному и тому же источнику синхросигналов. IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса. См. раздел Синхронизация сигнала глобального сброса с доменом тактовой синхронизации ядра IP.