Целочисленный делитель тактового сигнала с двумя коэффициентами делителя

Блок смешанного сигнала/PLL/компоновочные блоки

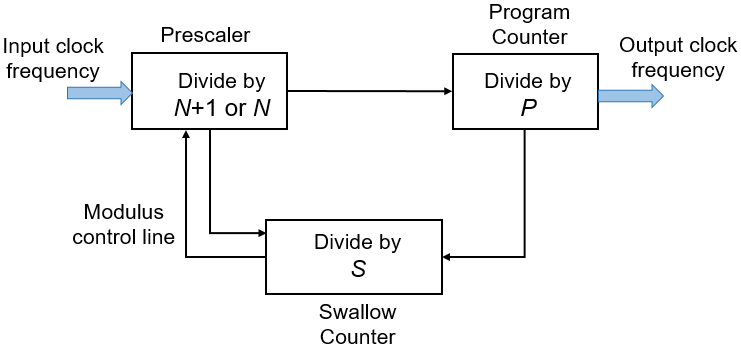

Блок подсистемы Dual Modulus Prescaler состоит из счетчика программ, счетчика ласточек и прескалера.

Когда блок впервые принимает входной сигнал, активизируется функция глотания импульсов. Прескалер делит частоту входного сигнала на (N + 1), где N определяется параметром делителя Прескалера (N). Счетчики программы и ласточки начинают отсчет. Счетчик глотания сбрасывается после подсчета в S импульсов, или (N + 1) S циклов, где S определяется параметром Значение счетчика глотания (S). Затем функция импульсного глотания деактивируется, и прескалер делит входную частоту на N.

Поскольку счетчик программы уже обнаружил S импульсов, он требует (P-S) больше импульсов или (P-S) N циклов для достижения переполнения, где P определяется параметром Program counter value (P). Цикл повторяется после сброса обоих счетчиков.

Эффективное значение делителя прескалера двойного модуля представляет собой отношение входной частоты к выходной частоте:

− S) = NP + S

Примечание

Чтобы предотвратить преждевременный сброс счетчика программ и прескалера до окончания подсчета счетчика ласточки, необходимо выполнить P≥S условия.

Двухмодульный прескалер также известен как делитель проглатывания импульсов.

[1] Разави, Бехзад. Микроэлектроника РФ. Река Верхнее Седло, Нью-Джерси: Prentice Hall PTR, 1998.

Дробный разделитель часов с накопителем | Разделитель дробных синхросигналов с DSM | PFD | Один модуль Prescaler | VCO