Конечная импульсная характеристика (КИХ) децимирующего фильтра - оптимизирована для генерации HDL-кода

Поддержка/фильтрация HDL-файлов DSP System Toolbox

Блок FIR Decimation HDL Optimized реализует полифазу конечной импульсной характеристики децимирующий фильтр, который оптимизирован для генерации HDL-кода. Блок обеспечивает аппаратный интерфейс с входными и выходными сигналами управления. Чтобы обеспечить точное по циклу симуляцию сгенерированного HDL-кода, блок моделирует архитектурную задержку, включая регистры трубопроводов и совместное использование ресурсов.

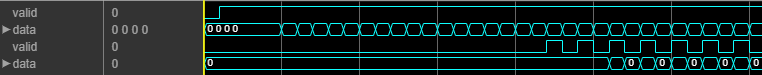

Блок принимает скаляр или векторный вход. Когда вы используете векторный вход, коэффициент десятикратного уменьшения должен быть целым числом, кратным размеру вектора. Блок использует односкоростную реализацию. Значение выхода скаляром, и допустимый сигнал указывает, какие выборки действительны после десятикратного уменьшения. Форма волны показывает вектор входа из четырех выборок и десятикратного уменьшения коэффициент восемь. Выходная выборка действительна каждый второй цикл.

Блок обеспечивает две структуры фильтра. Системная архитектура прямой формы обеспечивает полностью параллельную реализацию, которая эффективно использует Intel® и Xilinx® Блоки DSP. Транспонированная архитектура прямой формы является полностью параллельной реализацией, которая подходит для приложений FPGA и ASIC. Для реализации фильтра, который совпадает с множителями, регистрами трубопроводов и предварительными добавками к строению DSP вашего поставщика FPGA, укажите целевое устройство, когда вы генерируете HDL-код.

Блок реализует один фильтр для каждой выборки в векторе входа. Блок затем разделяет этот фильтр между полифазными подфильтрами путем чередования коэффициентов подфильтра во времени.

Для конечной импульсной характеристики децимирующего фильтра с размером входного сигнала, большим коэффициент десятикратного уменьшения, или последовательной реализации HDL (только скаляр ввода) используйте блок FIR Decimation вместо этого блока.

Сброс поведения

По умолчанию блок FIR Decimation HDL Optimized соединяет сгенерированный глобальный сброс HDL только с регистрами пути управления. Два параметра сброса, Enable reset input port и Use HDL global reset, соединяют сигнал сброса с регистрами пути данных. Из-за дополнительной маршрутизации и загрузки сигнала сброса сброс регистров пути данных может снизить эффективность синтеза.

Параметр Enable reset input port включает порт reset на блоке. Сигнал сброса реализует локальный синхронный сброс регистров пути данных. Для оптимального использования ресурсов FPGA эта опция не соединяет сигнал сброса с регистрами, нацеленными на блоки DSP FPGA.

Параметр Use HDL global reset соединяет сгенерированный HDL сигнал глобального сброса с регистрами пути данных. Этот параметр не изменяет внешний вид блока и не изменяет поведение симуляции в Simulink. Сгенерированный глобальный сброс HDL может быть синхронным или асинхронным в зависимости от параметра HDL Code Generation Global Settings > Reset type > в Параметры конфигурации модели. В зависимости от вашего устройства, использование глобального сброса может переместить регистры из блоков DSP и увеличить использование ресурсов.

Когда вы выбираете параметры Enable reset input port и Use HDL global reset вместе, глобальные и локальные сигналы сброса очищают регистры пути данных и управления.

Факторы о сбросе для сгенерированных испытательных стендов

Инициализация FPGA в цикле обеспечивает глобальный сброс, но не обеспечивает автоматически локальный сброс. С параметрами сброса по умолчанию регистры пути данных, которые не сбрасываются, могут привести к несоответствиям цикл (FIL), если вы запускаете модель FIL более одного раза, не сбрасывая плату. Выберите Use HDL global reset, чтобы автоматически сбросить регистры пути данных или выберите Enable reset input port и утвердите локальный сброс в модели, чтобы сигнал сброса стал частью испытательного стенда Simulink FIL.

Сгенерированный испытательный стенд HDL обеспечивает глобальный сброс, но не обеспечивает автоматического локального сброса. С параметрами сброса по умолчанию и параметрами конфигурации сброса регистра по умолчанию, сгенерированный HDL-код включает начальное значение симуляции для регистров пути данных. Однако, если вы обеспокоены X-предложение в проекте, можно задать параметр HDL Code Generation Global Settings > Coding style > No-reset register initialization > в Параметрах конфигурации Do not initialize. В этом случае, с параметрами сброса блоков по умолчанию, регистры пути данных, которые не сбрасываются, могут вызвать X-предложение по пути данных в начале симуляции HDL. Выберите Use HDL global reset, чтобы автоматически сбросить регистры пути данных или выберите Enable reset input port и задайте локальный сброс в модели, чтобы сигнал сброса стал частью сгенерированного HDL- испытательного стенда.