Вы можете сгенерировать переиспользуемое ядро IP HDL для любого поддерживаемого Xilinx® или Altera® Устройство ПЛИС. Рабочий процесс создает отчет по IP-ядру, в котором отображаются строение целевого интерфейса и заданные параметры кодера. См. Раздел «Настраиваемое ядро IP- Генерации»

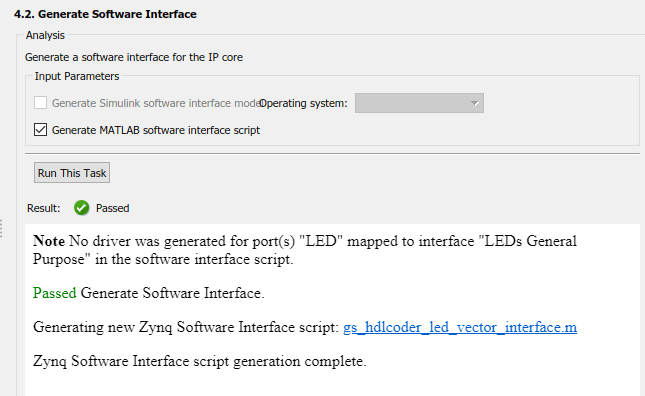

Вы можете, опционально, создать свои собственные пользовательские исходные проекты и интегрировать сгенерированное IP-ядро в исходный проект. Рабочий процесс не требует Embedded Coder® программное обеспечение, поскольку вам не нужно генерировать встраиваемый код, который запускается на процессоре. Это означает, что рабочий процесс имеет Generate Software Interface задачу, но вы не можете сгенерировать модель интерфейса программного обеспечения. Если у вас установлены HDL Verifier™, на Set Target Reference Design задаче установите Insert JTAG MATLAB as AXI Master (HDL Verifier Required) равным on. Затем можно сгенерировать скрипт программного интерфейса в Generate Software Interface задаче, чтобы быстро прототипировать и протестировать функциональность HDL-ядра IP с помощью MATLAB AXI Master. См. «Генерация скрипта интерфейса программного обеспечения для зондирования» и «Быстрое прототипирование HDL IP Core».

Рабочий процесс для плат FPGA имеет следующие функции:

Set Target Reference Design задачу. Заполняет исходный проект, ее версию инструмента и заданные параметры.

Set Target Interface задачу. Сопоставьте ваши порты DUT с интерфейсами на целевой платформе.

Set Target Frequency задачу. Задает Target Frequency (MHz) изменения модуля синхроимпульса в исходном проекте для формирования синхроимпульса с этой частотой.

Generate RTL Code and IP Core задачу. Генерирует многоразовое и резкое IP-ядро. Ядро IP упаковывает код RTL, файл заголовка C и файлы определения ядра IP.

Create Project задачу. Создает проект для интеграции ядра IP в предопределенные исходные проекты.

Можно сгенерировать IP-ядро с опциональным AXI4 или AXI4-Lite интерфейсом.

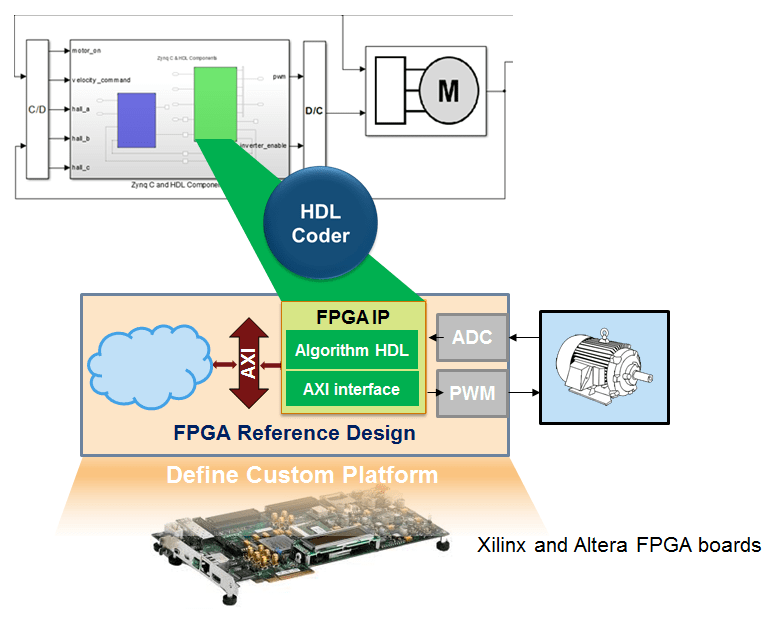

Этот рисунок показывает, как HDL- Coder™ генерирует IP-ядро с AXI4 интерфейсом и интегрирует IP-ядро в исходный проект FPGA. См. раздел «Системная плата и система регистрации Исходного проекта».

Используйте HDL Coder, сгенерированный AXI4-Lite интерфейс, чтобы соединить IP-ядро с устройством AXI4 или AXI4-Lite Master, таким как:

Процессор MicroBlaze.

Процессор Nios II.

PCIe Endpoint, который соединяется с внешним процессором.

Мастер JTAG.

Когда вы подключаете HDL-IP-ядро к процессору, такому как MicroBlaze, необходимо интегрировать рукописный код С, чтобы запустить его на процессоре. Сгенерированный отчет IP core отображает информацию о отображении адресов регистров. Чтобы найти смещения регистров в пространстве регистров ядра IP, используйте эту информацию отображения. Чтобы получить адрес памяти каждого регистра, добавьте смещение регистра к базовому адресу, который вы задаете в своем исходном проекте. Смещения регистров можно также найти в заголовочном файле C в сгенерированной папке IP core.

В функции определения исходного проекта можно создать свои собственные пользовательские исходные проекты без AXI4 ведомого интерфейса. См. также addAXI4SlaveInterface.

При создании пользовательского исходного проекта для назначения автономной платы FPGA используйте EmbeddedCoderSupportPackage метод hdlcoder.ReferenceDesign класс:

hRD.EmbeddedCoderSupportPackage = ... hdlcoder.EmbeddedCoderSupportPackage.None;

EmbeddedCoderSupportPackage.HDL Coder поддерживает эти платы FPGA с IP Core Generation рабочий процесс:

Xilinx Kintex-7 KC705 development board

Arrow DECA MAX 10 FPGA evaluation kit

Используя эти платы, можно интегрировать сгенерированное IP-ядро в default system исходный проект. По умолчанию этот исходный проект не имеет AXI4 ведомого интерфейса. Вы можете добавить интерфейс в функцию определения исходного проекта.

IP Core Generation рабочий процесс не поддерживает:

RAM Architecture установлено на Generic RAM without clock enable.

Использование различных синхроимпульсов для ядра IP и интерфейса AXI. The IPCore_Clk и AXILite_ACLK должен быть синхронным и подключен к одному и тому же источнику синхроимпульса. The IPCore_RESETN и AXILite_ARESETN должен быть подключен к тому же источнику сброса. См. «Синхронизация сигнала глобального сброса с тактовой Областью IP Core».