Программное обеспечение HDL- Verifier™ предоставляет средство для проверки HDL-модулей в MATLAB® окружение. Вы делаете это, кодируя HDL- модели и функцию MATLAB, которая может делиться данными с HDL- моделями. В этой главе рассматриваются соглашения о программировании, интерфейсах и планировании для функций испытательного стенда MATLAB, которые взаимодействуют с Симулятором HDL.

MATLAB test bench функции позволяют вам проверить эффективность HDL-модели или компонентов в модели. Функция испытательного стенда управляет значениями на сигналах, подключенных к входным портам тестируемого проекта HDL, и получает значения сигналов от выходных портов модуля.

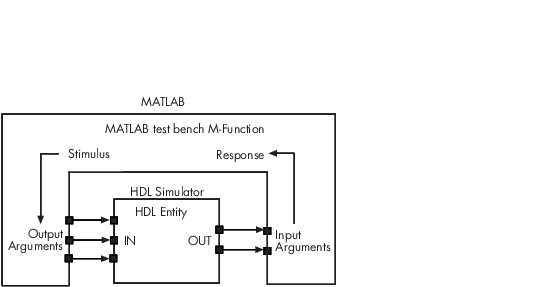

Следующий рисунок показывает, как функция MATLAB оборачивается и общается с симулятором HDL во время сеанса симуляции испытательного стенда.

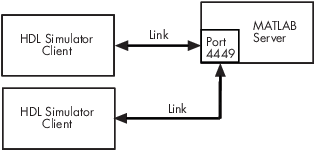

При соединении с MATLAB Симулятора HDL функционирует как клиент, а MATLAB - как сервер. Следующий рисунок показывает сценарий с несколькими клиентами, соединяющийся с сервером в порте 4449 сокета TCP/IP.

MATLAB-сервер может обслуживать несколько одновременных сеансов Симулятора HDL и HDL-модулей. Однако необходимо следовать рекомендуемым рекомендациям, чтобы помочь серверу отслеживать вводы-выводы, связанные с каждым модулем и сеансом. Сервер MATLAB, который вы начинаете с предоставленной функции hdldaemon, ожидает запросов на подключение от образцов из Симуляторов HDL, работающих на том же или других компьютерах. Когда сервер получает запрос, он выполняет указанную функцию MATLAB, которую вы закодировали, чтобы выполнять задачи от имени модуля в вашем HDL- проекта. Параметры, которые вы задаете при запуске сервера, указывают, устанавливает ли сервер общую память или коммуникационные ссылки TCP/IP сокета.

Для получения информации о действительных Строениях машины см. Строения косимуляции.

Примечание

Соглашения о программировании, интерфейсах и планировании для функций испытательного стенда и функций компонента практически идентичны. По большей части одни и те же процедуры применяются к обоим типам функций.

Следуйте этим шагам рабочего процесса, чтобы создать сеанс испытательного стенда MATLAB для косимуляции с Симулятором HDL.

Связывание Испытательного стенда вызовами функций с matlabtb

Установите точки останова для интерактивной отладки HDL (необязательно).

Выберите имя модуля HDL для использования с испытательным стендом MATLAB

Задайте режимы направления портов в HDL-модуле для использования с испытательным стендом

Укажите типы данных портов в модулях HDL для использования с испытательным стендом

Компилируйте и разрабатывайте проект HDL для использования с испытательным стендом

Самым базовым элементом связи в интерфейсе HDL Verifier является HDL-модуль. Интерфейс передает все данные между симулятором HDL и MATLAB в качестве данных порта. Программное обеспечение HDL Verifier работает с любым существующим HDL-модулем. Однако при кодировании модуля HDL, предназначенного для верификации MATLAB, следует учитывать его имя, типы данных, которые будут использоваться совместно между этими двумя окружениями, и режимы направления.

Хотя и не требуется, при присвоении имени HDL-модулю рассмотрите выбор имени, которое также может использоваться в качестве имени функции MATLAB. (Обычно правила именования для VHDL® или Verilog® и MATLAB совместимы.) По умолчанию программное обеспечение HDL Verifier предполагает, что HDL-модуль и его функция симуляции имеют то же имя. См. Bind Test Bench Function Calls With matlabtb.

Для получения дополнительной информации о руководствах по названию функций MATLAB, смотрите «Советы программирования MATLAB» о файлах и именах файлов в документации MATLAB.

В операторе модуля необходимо задать каждый порт с режимом направления (вход, вывод или двунаправленный). Следующая таблица определяет эти три режима.

| Использовать режим VHDL... | Использовать режим Verilog... | Для портов, которые... |

|---|---|---|

IN | input | Представление сигналов, которые могут управляться функцией MATLAB |

OUT | output | Представление значений сигналов, которые передаются в функцию MATLAB |

INOUT | inout | Представление двунаправленных сигналов, которые могут управляться или передавать значения в функцию MATLAB |

В этом разделе описывается, как задать типы данных, совместимые с MATLAB для портов в модулях HDL. Дополнительные сведения о том, как интерфейс HDL Verifier преобразует типы данных для окружения MATLAB, см. в разделе Поддерживаемые типы данных.

Примечание

При использовании неподдерживаемых типов программа HDL Verifier выдает предупреждение и игнорирует порт во время выполнения. Например, если вы задаете свой интерфейс с пятью портами, один из которых является портом доступа VHDL, во время выполнения, то интерфейс выводит предупреждение и ваш код видит только четыре порта.

Типы данных портов для сущностей VHDL. В оператора сущности необходимо задать каждый порт, который планируется тестировать с MATLAB с типом данных VHDL, поддерживаемым программным обеспечением HDL Verifier. Интерфейс может преобразовывать скалярные и массивные данные следующих типов VHDL в сопоставимые типы MATLAB:

STD_LOGIC, STD_ULOGIC, BIT, STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR, и BIT_VECTOR

INTEGER и NATURAL

REAL

TIME

Перечисляемые типы, включая пользовательские перечисляемые типы и CHARACTER

Интерфейс также поддерживает все подтипы и массивы предыдущих типов.

Примечание

Программное обеспечение HDL Verifier не поддерживает расширенные идентификаторы VHDL для следующих компонентов:

Имена портов и сигналов, используемые в косимуляции

Перечисление литералов при использовании в качестве индексов массивов имен портов и сигналов, используемых в косимуляции

Однако программное обеспечение поддерживает основные идентификаторы для VHDL.

Типы данных портов для модулей Verilog. В определении модуля необходимо определить каждый порт, который вы планируете тестировать с MATLAB с типом данных порта Verilog, который поддерживается программным обеспечением HDL Verifier. Интерфейс может преобразовывать данные следующих типов портов Verilog в сопоставимые типы MATLAB:

reg

целое число

провод

Примечание

Программное обеспечение HDL Verifier не поддерживает идентификаторы Verilog escaped для имен портов и сигналов, используемых в косимуляции. Однако он поддерживает простые идентификаторы для Verilog.

После создания или редактирования исходных файлов HDL используйте компилятор Симулятора HDL для компиляции и отладки кода.

Дополнительные примеры см. в руководствах HDL Verifier и демонстрациях. Для получения дополнительной информации об использовании HDL-компилятора смотрите документацию симулятора.

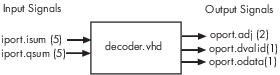

Эта выборка фрагмента кода VHDL задаёт сущность decoder. По умолчанию сущность связана с функцией испытательного стенда MATLAB decoder.

Ключевое слово PORT помечает начало предложения порта сущности, которое задает два IN порты - isum и qsum- и три OUT порты - adj, dvalid, и odata. Порты выхода управляют сигналами к входным портам функции MATLAB для обработки. Порты входа получают сигналы от портов выхода функции MATLAB.

Оба входных порта заданы как векторы, состоящие из пяти стандартных логических значений. Порт выхода adj также определяется как стандартный логический вектор, но состоит только из двух значений. Порты выхода dvalid и odata заданы как скалярные стандартные логические порты. Для получения информации о том, как интерфейс HDL Verifier преобразует данные стандартных логических скаляров и типов массивов для использования в среде MATLAB, смотрите Поддерживаемые типы данных.

ENTITY decoder IS PORT ( isum : IN std_logic_vector(4 DOWNTO 0); qsum : IN std_logic_vector(4 DOWNTO 0); adj : OUT std_logic_vector(1 DOWNTO 0); dvalid : OUT std_logic; odata : OUT std_logic); END decoder ;

Кодирование функции MATLAB для проверки HDL-модуля или компонента требует, чтобы вы следовали определенным соглашениям о кодировании. Вы также должны понять происходящие преобразования типов данных и программные преобразования типов данных для работы с данными и возврата данных в Симулятор HDL.

Чтобы кодировать функцию MATLAB для проверки HDL-модуля или компонента, выполните следующие шаги:

Изучение синтаксиса функции MATLAB HDL Verifier испытательного стенда. Смотрите Синтаксис функции испытательного стенда.

Осмыслите, как программное обеспечение HDL Verifier преобразует данные из Симулятора HDL для использования в окружение MATLAB. См. «Поддерживаемые типы данных».

Выберите имя для функции MATLAB. Смотрите Bind HDL Module Component, чтобы MATLAB Испытательного стенда Function.

Задайте ожидаемые параметры в линии определения функции. См. «Синтаксис функции MATLAB и определения аргументов функции».

Определите типы данных портов, передаваемых в функцию. См. «Синтаксис функции MATLAB и определения аргументов функции».

Извлеките и, если применимо к симуляции, примените информацию, полученную в portinfo структура. См. Раздел «Получение доступа к информации о портах и применение».

Преобразуйте данные для манипуляций в среде MATLAB, как применимо. См. раздел Преобразование данных HDL в MATLAB.

Преобразуйте данные, которые нужно вернуть в Симулятор HDL. Смотрите Преобразование данных для возврата в Симулятор HDL.

Для получения дополнительной информации смотрите Испытательный Стенд и Component Function Writing.

Синтаксис функции испытательного стенда MATLAB:

function [iport, tnext] = MyFunctionName(oport, tnow, portinfo)

Для получения объяснений по каждому из аргументов функции см. Функцию MATLAB Определений синтаксиса функции и аргумента функции.

В этом разделе используется пример функции MATLAB, чтобы идентифицировать разделы функции испытательного стенда MATLAB, требуемой программным обеспечением HDL Verifier. Полный текст кода, используемого в этой выборке, можно увидеть в разделе MATLAB Builder EX Function Example: manchester_decoder.m.

Для пользователей ModelSim

Этот пример использует сущность VHDL и функциональный код MATLAB Builder™ EX, полученный из фрагмента декодера примера Приемник Манчестерского Кода. Полный список VHDL и кода функции см. в следующих файлах:

matlabroot\toolbox\edalink\extensions\modelsim\modelsimdemos\vhdl\manchester\decoder.vhdmatlabroot\toolbox\edalink\extensions\modelsim\modelsimdemos\manchester_decoder.mКак первый шаг к кодированию функции EX испытательного стенда MATLAB Builder, вы должны понять, как данные, смоделированные в сущности VHDL, сопоставляются с данными в окружение EX MATLAB Builder. Сущность VHDL- decoder определяется следующим образом:

ENTITY decoder IS PORT ( isum : IN std_logic_vector(4 DOWNTO 0); qsum : IN std_logic_vector(4 DOWNTO 0); adj : OUT std_logic_vector(1 DOWNTO 0); dvalid : OUT std_logic; odata : OUT std_logic ); END decoder ;

В следующем обсуждении освещаются ключевые строки кода в определении manchester_decoder Функция MATLAB Builder EX:

Укажите имя функции MATLAB и необходимые параметры.

Следующий код является объявлением функции manchester_decoder Функция MATLAB Builder EX.

function [iport,tnext] = manchester_decoder(oport,tnow,portinfo)

См. «Синтаксис функции MATLAB и определения аргументов функции».

Объявление функции выполняет следующие действия:

Называет функцию. Это объявление называет функцию manchester_decoder, который отличается от имени сущности decoder. Поскольку имена различаются, имя функции должно быть задано явным образом позже, когда сущность инициализируется для верификации с matlabtb или matlabtbeval функция. Смотрите Bind HDL Module Component, чтобы MATLAB Испытательного стенда Function.

Задает требуемый аргумент и параметры возврата. Функция испытательного стенда MATLAB Builder EX должна вернуть два параметра, iport и tnextи передайте три аргумента, oport, tnow, и portinfo, и должен появиться в указанном порядке. См. «Синтаксис функции MATLAB и определения аргументов функции».

Выходы функции должны быть инициализированы до пустых значений, как в следующем примере кода:

tnext = []; iport = struct();

Вы должны инициализировать выходы функции в начале функции, чтобы следовать рекомендованной лучшей практике.

Следующий рисунок показывает связь между портами сущности и функцией MATLAB Builder EX iport и oport параметры.

Для получения дополнительной информации о необходимых параметрах функции испытательного стенда MATLAB Builder EX, смотрите Синтаксис Функции MATLAB и Определения аргументов функции.

Обратите внимание на типы данных портов, определенных для моделируемой сущности.

Программа HDL Verifier преобразует типы данных HDL в сопоставимые типы данных MATLAB Builder EX и наоборот. Когда вы разрабатываете функцию MATLAB Builder EX, вы должны знать типы данных, которые она получает от Симулятора HDL и должна вернуться к Симулятору HDL.

Сущность VHDL, определенный для этого примера, состоит из следующих портов

Примеры определений портов VHDL

| Порт | Направление | Тип... | Преобразование в/требует преобразования в... |

|---|---|---|---|

isum | IN | STD_LOGIC_VECTOR(4 DOWNTO 0) | 5-битный столбец или вектор-строка символов, где каждый бит преобразуется в стандартный логический литерал символов. |

qsum | IN | STD_LOGIC_VECTOR(4 DOWNTO 0) | 5-битный столбец или вектор-строка символов, где каждый бит преобразуется в стандартный логический литерал символов. |

adj | OUT | STD_LOGIC_VECTOR(1 DOWNTO 0) | 2-элементный вектор-столбец символов. Каждый символ соответствует соответствующему буквальному символу, который представляет логическое состояние и преобразуется в один бит. |

dvalid | OUT | STD_LOGIC | Символ, соответствующий литералу символов, представляющему логическое состояние. |

odata | OUT | STD_LOGIC | Символ, соответствующий литералу символов, представляющему логическое состояние. |

Дополнительные сведения о преобразовании типов данных интерфейса см. в разделе Поддерживаемые типы данных.

Настройте все необходимые параметры синхронизации.

The tnext оператор назначения настраивает параметр timing tnext таким образом, симулятор вызывает функцию MATLAB Builder EX каждую наносекунду.

tnext = tnow+1e-9;

Преобразуйте выходы порта в типы данных MATLAB для обработки.

Следующий фрагмент кода иллюстрирует преобразование данных типа выхода данных порта.

%% Compute one row and plot isum = isum + 1; adj(isum) = mvl2dec(oport.adj'); data(isum) = mvl2dec([oport.dvalid oport.odata]); . . .

Эти два вызова для mvl2dec преобразовать двоичные данные, которые функция MATLAB Builder EX получает от выходных портов сущности, adj, dvalid, и odata к беззнаковым десятичным значениям, которые может вычислить MATLAB Builder EX. Функция преобразует 2-битный транспонированный вектор oport.adj десятичное значение в области значений от 0 до 4 и oport.dvalid и oport.odata до десятичного значения 0 или 1.

Синтаксис функции MATLAB и Аргумента функции Определений предоставляет сводные данные типов преобразований данных, учитываемых при кодировании симуляции функций MATLAB.

Преобразуйте данные, которые будут возвращены в Симулятор HDL.

Следующий фрагмент кода иллюстрирует преобразование данных типа данных, которые должны быть возвращены в Симулятор HDL.

if isum == 17 iport.isum = dec2mvl(isum,5); iport.qsum = dec2mvl(qsum,5); else iport.isum = dec2mvl(isum,5); end

Три вызова на dec2mvl преобразуйте десятичные значения, вычисленные MATLAB Builder EX, в двоичные данные, которые функция MATLAB Builder EX может отложить во входные порты сущности, isum и qsum. В каждом случае функция преобразует десятичное значение в 5-элементный битовый вектор с каждым битом, представляющим символ, который преобразуется в буквальный символ, представляющий логическое состояние.

Преобразование данных для возврата в Симулятор HDL предоставляет сводные данные типов преобразований данных, учитываемых при возвращении данных в Симулятор HDL.

Пример функции EX MATLAB Builder: manchester_decoder.m

function [iport,tnext] = manchester_decoder(oport,tnow,portinfo) % MANCHESTER_DECODER Test bench for VHDL 'decoder' % [IPORT,TNEXT]=MANCHESTER_DECODER(OPORT,TNOW,PORTINFO) - % Implements a test of the VHDL decoder entity which is part % of the Manchester receiver demo. This test bench plots % the IQ mapping produced by the decoder. % % iport oport % +-----------+ % isum -(5)->| |-(2)-> adj % qsum -(5)->| decoder |-(1)-> dvalid % | |-(1)-> odata % +-----------+ % % isum - Inphase Convolution value % qsum - Quadrature Convolution value % adj - Clock adjustment ('01','00','10') % dvalid - Data validity ('1' = data is valid) % odata - Recovered data stream % % Adjust = 0 (00b), generate full 16 cycle waveform % Copyright 2003-2009 The MathWorks, Inc. persistent isum; persistent qsum; %persistent ga; persistent x; persistent y; persistent adj; persistent data; global testisdone; % This useful feature allows you to manually % reset the plot by simply typing: >manchester_decoder tnext = []; iport = struct(); if nargin == 0, isum = []; return; end if exist('portinfo') == 1 isum = []; end tnext = tnow+1e-9; if isempty(isum), %% First call scale = 9; isum = 0; qsum = 0; for k=1:2, ga(k) = subplot(2,1,k); axis([-1 17 -1 17]); ylabel('Quadrature'); line([0 16],[8 8],'Color','r','LineStyle',':','LineWidth',1) line([8 8],[0 16],'Color','r','LineStyle',':','LineWidth',1) end xlabel('Inphase'); subplot(2,1,1); title('Clock Adjustment (adj)'); subplot(2,1,2); title('Data with Validity'); iport.isum = '00000'; iport.qsum = '00000'; return; end % compute one row, then plot isum = isum + 1; adj(isum) = bin2dec(oport.adj'); data(isum) = bin2dec([oport.dvalid oport.odata]); if isum == 17, subplot(2,1,1); for k=0:16, if adj(k+1) == 0, % Bang on! line(k,qsum,'color','k','Marker','o'); elseif adj(k+1) == 1, % line(k,qsum,'color','r','Marker','<'); else line(k,qsum,'color','b','Marker','>'); end end subplot(2,1,2); for k=0:16, if data(k+1) < 2, % Invalid line(k,qsum,'color','r','Marker','X'); else if data(k+1) == 2, %Valid and 0! line(k,qsum,'color','g','Marker','o'); else line(k,qsum,'color','k','Marker','.'); end end end isum = 0; qsum = qsum + 1; if qsum == 17, qsum = 0; disp('done'); tnext = []; % suspend callbacks testisdone = 1; return; end iport.isum = dec2bin(isum,5); iport.qsum = dec2bin(qsum,5); else iport.isum = dec2bin(isum,5); end